ADP3171 Synchronous Buck Controller with Dual Linear Regulator

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Microwave Tube Fault-Current Model for Design of Crowbar Protection

Microwave Tube Fault-Current Model for Design of Crowbar Protection Subhash Joshi T.G. Vinod John Member, IEEE Senior Member, IEEE Power Electronics Group Department of Electrical Engineering Centre for Development of Advanced Computing Indian Institute of Science Thiruvananthapuram-695033, India Bangalore-560012, India Email:[email protected] Email:[email protected] Abstract—Many applications that use high energy plasma are realized using Microwave tubes (MWT) that operate at peak power in the range of hundreds of MW and frequency in GHz. One failure mode of the MWT is due to the excess energy in the tube during internal arcing events. Crowbar is used to protect the MWT by diverting the energy during fault. To compute the energy released into the MWT, the dc fault current model and the MWT model are essential. An equivalent fuse wire model is utilized for the MWT for the crowbar applications. The paper proposes a model for the dc fault current, the analysis for (a) (b) which is based on Joules Integral energy concept. The model Fig. 1. Circuit network used for crowbar analysis (a) HV power supply with provides flexibility to choose a range of practically observed MWT and crowbar (b) MWT is replaced with fuse wire for wire survivability reactance to resistance ratio (X=R) of transformer and also test. allows the use of a range of dc current limiting resistances that are utilized in the High Voltage (HV) power supply circuits in Microwave applications. The non-linearity of the system due to is decided by the speed of operation of crowbar. -

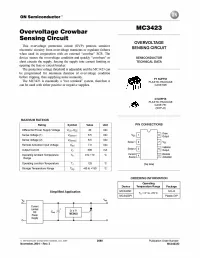

Overvoltage Crowbar Sensing Circuit MC3423

ON Semiconductor ™ ijjp MC3423 Overvoltage Crowbar Sensing Circuit OVERVOLTAGE Tliis overvoltage protection Circuit (OVP) protects sensitive SENSING CIRCUIT electronic circuitry from overvoltage transients or regulator failures when used in conjunction with an extemal “crowbar” SCR. The device senses the overvoltage condition and ąuickly “crowbars” or SEMICONDUCTOR short circuits the supply, forcing the supply into current limiting or TECHNICAL DATA opening the fuse or Circuit breaker. The protection voltage threshold is adjustable and the MC3423 can be programmed for minimum duration of overvoltage condition before tripping, thus supplying noise immunity. P1 SUFFIX The MC3423 is essentially a “two tenninal” system, therefore it PLASTIC PACKAGE can be used with either positive or negative supplies. CASE 626 D SUFFIX PLASTIC PACKAGE CASE 751 (SOP-8) MAXIMUM RATINGS Rating Symbol Value Unit PIN CONNECTIONS Differential Power Supply Voltage 40 Vdc VCC-VEE W Drive Sense Voltage (1) 6.5 Vdc 1 8 ^Sensel v cc Output Sense Voltage (2) Vsense2 6.5 Vdc Sense 1 2 7 VEE Remote Activation Input Voltage ^act 7.0 Vdc Indicator Sense 2 3 6 Output Current >o 300 mA Output Current Remote Operating Ambient Temperaturę Ta 0 to +70 °C 4 5 Rangę Source Activation Operating Junction Temperaturę Tj 125 °C (Top View) Storage Temperaturę Rangę Tstg -65 to +150 °C ORDERING INFORMATION Operating Device Temperaturę Rangę Package Simplified Application MC3423D SO-8 Ta - 0° to +70°C MC3423P1 Plastic DIP vout Current Limited + 1 r 0. V. P. 7 DC Cout MC3423 Power Supply © Semiconductor Components Industries, LLC, 2001 2690 Publication Order Number: November, 2001 - Rev. -

The Silicon Controlled Rectifier (SCR)

The silicon controlled rectifier (SCR) Shockley diodes are curious devices, but rather limited in application. Their usefulness may be expanded, however, by equipping them with another means of latching. In doing so, each becomes true amplifying devices (if only in an on/off mode), and we refer to these as silicon-controlled rectifiers, or SCRs. The progression from Shockley diode to SCR is achieved with one small addition, actually nothing more than a third wire connection to the existing PNPN structure: (Figure below) The Silicon-Controlled Rectifier (SCR) If an SCR's gate is left floating (disconnected), it behaves exactly as a Shockley diode. It may be latched by breakover voltage or by exceeding the critical rate of voltage rise between anode and cathode, just as with the Shockley diode. Dropout is accomplished by reducing current until one or both internal transistors fall into cutoff mode, also like the Shockley diode. However, because the gate terminal connects directly to the base of the lower transistor, it may be used as an alternative means to latch the SCR. By applying a small voltage between gate and cathode, the lower transistor will be forced on by the resulting base current, which will cause the upper transistor to conduct, which then supplies the lower transistor's base with current so that it no longer needs to be activated by a gate voltage. The necessary gate current to initiate latch-up, of course, will be much lower than the current through the SCR from cathode to anode, so the SCR does achieve a measure of amplification. -

Crowbar Replacement Through Solid State Opening Switches

SOLID STATE 2MW KLYSTRON POWER CONTROL SYSTEM I. Roth, J. Casey, T. Hawkey, M. Gaudreau, M. Kempkes, Diversified Technologies, Inc. 35 Wiggins Ave. Bedford, MA 01730 USA Abstract upper part of Figure 1 shows a typical crowbar circuit, Under an SBIR effort for the DOE, Diversified which shunts energy from the load. The disadvantages of Technologies, Inc. designed, built, and installed a solid this approach are well-known. The power supply, state power control system for the Advanced Light Source capacitors, and crowbar are subjected to very high klystrons at Argonne National Laboratory (ANL). This currents and mechanical forces with every arc, and the system consists of two major elements – a 100 kV, 20 A entire power system must be reset after each arc. Using a CW solid state series switch, and a solid state voltage solid-state switch can overcome these problems. regulator for the mod-anode of the klystron. The series switch replaces the existing mercury ignitron crowbar, LOAD PROTECTION USING A SOLID- eliminating these environmentally hazardous components STATE SWITCH while providing enhanced arc protection and faster return An alternative way to protect a high voltage load is to to transmit. The mod-anode voltage regulator uses series use a solid-state switch that opens during an arc, as shown IGBTs, operating in the linear regime, to provide highly in the lower diagram of Figure 1. In a pulsed system, this rapid and accurate control of the mod-anode voltage, and switch can also serve as the pulse modulator when an therefore the output power from the klystron. -

Silicon-Controlled Rectifiers

Component Theory SCRs 1 Silicon-Controlled Rectifiers Our exploration of thyristors begins with a device called the four-layer diode, also known as a PNPN diode, or a Shockley diode after its inventor, William Shockley. This is not to be confused with a Schottky diode, that two-layer metal-semiconductor device known for its high switching speed. A crude illustration of the Shockley diode, often seen in textbooks, is a four-layer sandwich of P-N-P-N semiconductor material. 2 Silicon-Controlled Rectifiers Shockley or 4-layer diode Transistor equivalent of Shockley diode 3 Silicon-Controlled Rectifiers A silicon-controlled rectifier (or semiconductor- controlled rectifier) is a four-layer solid state device that controls current. The name "silicon controlled rectifier" or SCR is General Electric's trade name for a type of thyristor. The SCR was developed by a team of power engineers led by Gordon Hall and commercialized by Frank W. "Bill" Gutzwiller in 1957. 4 Silicon-Controlled Rectifiers Construction of SCR An SCR consists of four layers of alternating P and N type semiconductor materials. Silicon is used as the intrinsic semiconductor, to which the proper dopants are added. The junctions are either diffused or alloyed. The planar construction is used for low power SCRs (and all the junctions are diffused). The mesa type construction is used for high power SCRs. In this case, junction J2 is obtained by the diffusion method and then the outer two layers are alloyed to it, since the PNPN pellet is required to handle large currents. 5 Silicon-Controlled Rectifiers It is properly braced with tungsten plates to provide greater mechanical strength. -

Synchronous-Buck MOSFET Drivers with Deadtime

TPS2834, TPS2835 SYNCHRONOUSĆBUCK MOSFET DRIVERS WITH DEADĆTIME CONTROL SLVS223B − NOVEMBER 1999 − REVISED AUGUST 2002 D Floating Bootstrap or Ground-Reference D PACKAGE High-Side Driver (TOP VIEW) D Adaptive Dead-Time Control ENABLE 1 14 BOOT D 50-ns Max Rise/Fall Times With 3.3-nF Load IN 2 13 NC D 2.4-A Typical Output Current CROWBAR 3 12 HIGHDR NC 4 11 BOOTLO D 4.5-V to 15-V Supply Voltage Range SYNC 5 10 LOWDR D TTL-Compatible Inputs DT 6 9 NC D Internal Schottky Bootstrap Diode PGND 7 8 VCC D SYNC Control for Synchronous or Nonsynchronous Operation PWP PACKAGE (TOP VIEW) D CROWBAR for OVP, Protects Against Faulted High-Side Power FETs ENABLE 1 14 BOOT D Low Supply Current....3 mA Typical IN 2 13 NC D CROWBAR 3 12 HIGHDR Ideal for High-Current Single or Multiphase Thermal Power Supplies NC 4 Pad 11 BOOTLO SYNC 5 10 LOWDR D ° ° −40 C to 125 C Operating Virtual Junction DT 6 9 NC Temperature Range PGND 7 8 VCC D Available in SOIC and TSSOP PowerPAD Packages NC − No internal connection description The TPS2834 and TPS2835 are MOSFET drivers for synchronous-buck power stages. These devices are ideal for designing a high-performance power supply using switching controllers that do not include on-chip MOSFET drivers. The drivers are designed to deliver minimum 2-A peak currents into large capacitive loads. The high-side driver can be configured as ground-reference or as floating-bootstrap. An adaptive dead-time control circuit eliminates shoot-through currents through the main power FETs during switching transitions, and provides high efficiency for the buck regulator. -

Design and Development of High Voltage Scheme for a Crowbar in RF Heating

Proceedings of the 2009 IEEE International Conference on Systems, Man, and Cybernetics San Antonio, TX, USA - October 2009 Design and Development of High Voltage Scheme for a Crowbar in RF Heating Prof. Himanshu K. Patel, Deep Shah Atman Shah Mauli Thacker Electrical Engineering, Post Graduate Student Post Graduate Student, Engineer, Tech Mahindra Nirma University, Polytechnic University, Drexel University, Ltd., Pune, INDIA Ahmedabad, INDIA NewYork, USA Philadelphia, USA [email protected] [email protected], [email protected] [email protected] [email protected] Abstract— Plasma is a mixture of freely moving charged pulsed signals, one each for the trigger network of the series particles. To sustain these particles in ionic state, very high switch and the crowbar. temperature is essential. RF heating systems are utilized for obtaining high temperatures. Arching phenomenon in these The crowbar is turned ON first, shunting the current across the systems can cause enormous damage to the RF tube. Fast load. This bypass of the load leads to short-circuiting of the switching circuit breakers are used to cutoff the load from the HVPS. If this persists, it may damage the power supply. Thus, supply in cases of arcing. The crowbar interrupts the connection a combination of series switch and crowbar is generally between the high voltage power supply (HVPS) and the RF tube preferred. for a temporary period during which the series switch has to open. CIRCUIT This paper presents the design and development of Crowbar BREAKER based on fiber optic triggering for the protection of RF heating system. The importance of optical triggering and utilization of fiber optic has been justified. -

Design and Performance Analysis of a Crowbar-Less High Voltage Power Supply Based on PSM Technique

Sådhanå (2018) 43:129 Ó Indian Academy of Sciences https://doi.org/10.1007/s12046-018-0813-2Sadhana(0123456789().,-volV)FT3](0123456789().,-volV) Design and performance analysis of a crowbar-less high voltage power supply based on PSM technique S K THAKUR*, S K KUMARI and YASHWANT KUMAR Variable Energy Cyclotron Centre, HBNI, 1/AF Bidhan Nagar, Kolkata 700064, India e-mail: [email protected] MS received 20 June 2017; revised 15 November 2017; accepted 6 December 2017; published online 3 July 2018 Abstract. A high voltage power supply (HVPS) of rating -40 kV, 5 A is designed and developed based on pulse step modulation (PSM) technique for inductive output tube based RF amplifier. The commercial avail- ability of such power supplies are very limited and that to at a very high cost. In future also, we shall need several PSM based HVPS of various ratings, so in-house development of a high voltage power supply is important to reduce the cost to less than half and also for easy maintenance. The present development is aimed to utilise a modern technique meeting all the important criteria, i.e., solid state based modular construction, crowbar-less design, reliable operation, voltage regulation with higher efficiency, fast response and most importantly easy to service. This paper deals with the design and development of HVPS rated at -40 kV, 5 A by using DSP TMS320F28335 as the main controller along with algorithms for the control system, interlocks and protections, test results, etc. Keywords. High voltage; power supply; RF amplifier; PSM; crowbar protection. 1. -

Application Note

Littelfuse.com APPLICATION NOTE ABSTRACT The Zener Sense Circuit This paper addresses the requirements for the The simplest way to protect against overvoltage is to use semiconductor sensing circuitry and SCR crowbar devices a Zener diode to sense the output voltage (Figure 1). When used in DC power supply over/under voltage protection the Zener goes into avalanche, it triggers the SCR. schemes. There are problems with this kind of protection: 1. No threshold adjustment, except by selecting INTRODUCTION different Zener diodes. It is uncommon now to find several hundred dollars 2. Inability to ignore momentary transients. worth of microprocessors and memory chips powered from 3. Poor SCR reliability caused by inadequate a single low DC supply. trigger–current rise time when slowly varying If this supply on the board doesn’t have overvoltage or voltage is sensed. undervoltage protection, potentially large sums of money can literally go up in smoke due to component failure, or, for instance, a tool may be accidentally dropped across the Power supply output line Level sensing supply buses of different voltages during testing or repair Zener diode SCR of the system. crowbar Since a couple of years, computer and industrial manufacturers agree to put additional small investment in RSC Over Voltage Protection (OVP) and Over/Under Voltage Protection (OUVP) circuitry to prevent disasters. Littelfuse chose the “crowbar” sensing circuit Common technology. This system senses the overvoltage condition, Figure 1. and quickly “crowbars” or short circuits the supply, forcing the supply into current limiting or opening the fuse or The Discrete Sense Circuit circuit breaker. -

Use of Diode As a Crowbar for Electromagnetic Launcher

Downloaded from http://iranpaper.ir http://www.itrans24.com/landing1.html 2016 International Conference on Automatic Control and Dynamic Optimization Techniques (ICACDOT) International Institute of Information Technology (I²IT), Pune Use Of Diode As A Crowbar For Electromagnetic Launcher Pradnya Pawar, A.B.Patil Gaurav Kumar, Pradeep Kumar Pimpri Chinchwad College of Engineering ARDE-DRDO, Pashan Pune, India Pune, India [email protected] Abstract— High current high voltage switches are extensively others due to its simplicity but found limitations in case of used for power applications. Electromagnetic launcher (Railgun) modular power supplies. As evident from previous discussion requires switching large current in the proper sequence to ensure the switch used in the railgun has to discharge the stored acceleration of projectiles to attain required velocities. These energy from the capacitors and the response time should be power applications require current of the order of Mega Ampere minimal, and can handle very high di/dt. The selection of for 5-10 ms and hence need special purpose switches. The Spark Gap or Ignitron are conventionally used for power application as switches mainly based on the power rating and the technology a crowbar switch. These switches operate at high voltage and used [1]. The conventional switches are having limitations to high current capacity but have low reliability, robustness and operate at these high voltage and high current capacity. Spark lifespan. In this paper ignitron as a crowbar switch is replaced by gap gives poor reliability and Ignitron is having drawback of diode switch. This reduced negative overshoot in the current. short service life. -

KEK-79-4 April 1979 P PERFORMANCE TESTS OF

KEK-79-4 April 1979 P PERFORMANCE TESTS OF CROWBAR CIRCUIT FOR KLYSTRON PROTECTION Hisashi KOBAYAKAWA, Koji TAKATA and Isao TOYAMA NATIONAL LABORATORY FOR HIGH ENERGY PHYSICS OHO-MACHI, TSUKUBA-GUN IBARAKI, JAPAN KEK Reports are available from Technical Information Office National Laboratory for High Energy Physics Oho-machi, Tsukuba-gun Ibarakl-ken, 300-32 JAPAN Phone: 02986-4-1171 Telex: 3652-534 (Domestic) (0)3652-534 (International) Cable: KEKOHO PERFORMANCE TESTS OF CROWBAR CIRCUIT FOR KLYSTRON PROTECTION Hisashi KOBAYAKAWA Depertment of Physics, Nagoya University, Nagoya, 464, Japan Koji TAKATA National Laboratory for High Energy Physics Oho-machi, Tsukuba-gun, Ibaraki-ken, 300-32, Japan Isao TOYAMA Nichicon Capacitor Ltd. Kusatsu, Shiga-ken, 525, Japan Abstract A crowbar circuit to protect high power klystron for the rf accele ration of the PF storage ring has been constructed for the experimental purposes. Brief description of the test circuit and results of the performance tests are presented. The circuit is designed for 50 kV operation and works sufficiently well for our purpose: electrical energy of 9 kJ switched within 5 ps and thus only 3 J fed to the load. 1. Introduction The PF storage ring (2.5 GeV) requires more than 500 kW of continuously rated rf power at 500 MHz. The rf generators consist of A klystrons each having an output power of 180 kW in the continuous mode. The klystron will be fed by a high voltagd dc power supply (50 kV, 10 A). The klystron beam voltage is produced by a conventional 12 phase YA bridge rectifier followed by a single stage LC filter, the design of which achieves a reasonably low level of ripple content of the beam voltage (0.2 %pp) . -

Crowbar Devices Used for Over Voltage Protection

CROWBAR DEVICES USED FOR OVER VOLTAGE PROTECTION Shefali Sinha1, Mr. Anil Gupta2, Dr. Manish Khemariya3, Mr. Amol Barve4 1Electrical and Electronics Engineering, Department, LNCT, Bhopal, (India) 2Asst. Professor, 3Professor, 4Associate Professor, Electrical and Electronics Engineering, Department, LNCT, Bhopal, (India) ABSTRACT One of the most common reason for the damage of electrical equipment in your power system is due to voltage Transient. There are various methods for overvoltage protection. In this paper, Protection from overvoltage is implemented with the help of Crowbar device. With the help of Gate triggering, a silicon controlled rectifier (SCR) and TRIAC is turned ON which ultimately protects the loads from overvoltage. Amplifiers are also being used to amplify the output voltage. Practically the condition arises when the regulator is short. To check this, we would produce excess voltage by varying the resistance connected between input and Output of regulator. Keywords: Over voltage protection, SCR, TRIAC, Transient, Regulator, Crowbar circuit. I. INTRODUCTION In electrical conveyance frameworks, dependably there exist an electrical homeless people which are accessible in the shape voltage surges. Really, they were not given the due significance preceding the presence and execution of semiconductor gadgets. A large portion of the electrical and hardware gadgets can be influenced and/or harmed by voltage homeless people or it might be because of mix of voltage and current. High voltage can open unintended current ways, for example, forward or turn around breakdown of diodes or oxides achieving their separate voltage inside incorporated circuits. In hardware circuits three stick positive and negative regulators are normally used to give stable DC voltages.