Simple Anti Capacitor Open-Circuit Self-Oscillation in a CMOS Schmitt Trigger-Invertor Oscillator Circuit for a Fail-Safe Relay Drive

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Op-Amp Comparators Model of a Schmitt Trigger

1 Electronic Instrumentation Experiment 6 -- Digital Switching Part A: Transistor Switches Part B: Comparators and Schmitt Triggers Part C: Digital Switching Part D: Switching a Relay Part A: Transistors Analog Circuits vs. Digital Circuits Bipolar Junction Transistors Transistor Characteristics Using Transistors as Switches 2 Analog Circuits vs. Digital Circuits An analog signal is an electric signal whose value varies continuously over time. A digital signal can take on only finite values as the input varies over time. 3 • A binary signal, the most common digital signal, is a signal that can take only one of two discrete values and is therefore characterized by transitions between two states. • In binary arithmetic, the two discrete values f1 and f0 are represented by the numbers 1 and 0, respectively. 4 • In binary voltage waveforms, these values are represented by two voltage levels. • In TTL convention, these values are nominally 5V and 0V, respectively. • Note that in a binary waveform, knowledge of the transition between one state and another is equivalent to knowledge of the state. Thus, digital logic circuits can operate by detecting transitions between voltage levels. The transitions are called edges and can be positive (f0 to f1) or negative (f1 to f0). 1 positive negative positive edge 0 edges edge 5 Bipolar Junction Transistors The bipolar junction transistor (BJT) is the salient invention that led to the electronic age, integrated circuits, and ultimately the entire digital world. The transistor is the principal active device in electrical circuits. When inputs are kept relatively small, the transistor serves as an amplifier. When the transistor is overdriven, it acts as a switch, a mode most useful in digital electronics. -

Design of CMOS Schmitt Trigger Munish Kumar, Parminder Kaur, Sheenu Thapar

ISSN: 2277-3754 ISO 9001:2008 Certified International Journal of Engineering and Innovative Technology (IJEIT) Volume 2, Issue 1, July 2012 Design of CMOS Schmitt Trigger Munish Kumar, Parminder Kaur, Sheenu Thapar voltage is applied at the input, both M1 andM2 are in OFF Abstract— This paper presents comparison among various condition while M4 and M5 are in ON condition and output Schmitt triggers on the basis of their hysteresis width and is at high logic level. When the input reaches to threshold average power consumed. Hysteresis width is improved by using voltage of M1 transistor then M1 will be on , while M2 two feedback loops as compared to conventional CMOS Schmitt trigger whose hysteresis width is fixed. All Schmitt trigger remains OFF and at this time output will be high M3 will be circuits have been realized using .25um and .18µm CMOS on , so M1 Try to pull down the node between M1 and M2 technology and simulation results are presented. while M3 try to pulls up this node to voltage VDD-VT , so transistor M2 stays the output to HIGH logic level , now Index Terms— Hysteresis Width, Static Power Dissipation, Dynamic Power Dissipation. when the input rises up to the threshold voltage of M2 then output switches to low logic level, so effectively our I. INTRODUCTION switching point shifted to higher voltage referred as VIH. Similar in case when input is falling from higher logic level Schmitt triggers are bistable networks that are widely used then PMOS‘s comes into picture and switching point at to enhance the immunity of a circuit to noise and output is shifted to some lower voltage referred as VIH. -

Low Power Schmitt Trigger

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by International Institute for Science, Technology and Education (IISTE): E-Journals Innovative Systems Design and Engineering www.iiste.org ISSN 2222-1727 (Paper) ISSN 2222-2871 (Online) Vol 3, No 2, 2012 Low Power Schmitt Trigger Swati Kundra *, Priyanka Soni Mody Institute of Technology & Science, Lakshmangarh-332311, India * E-mail of the corresponding author: [email protected] Abstract The Schmitt Trigger is a comparator circuit that incorporates positive feedback. Noise is being ignored by CMOS Schmitt Trigger as the hysteresis in a Schmitt Trigger circuit offers a better noise margin and noise stable operation. And the simulation has been done on Tanner EDA tool at TSMC 130nm technology with 1 V supply voltage. TSPICE simulation results of the circuit confirm the effectiveness of the approach. Proposed Schmitt Trigger is designed by using less transistor count and a capacitor which results in less average power consumption with decrease in area. Delay is also decreased by using only one PMOS as because delay is more concentrated to PMOS due to less mobility of PMOS compare to NMOS. Keywords: CMOS Schmitt Trigger, Delay, Low power consumption 1. Introduction Sometimes an input signal to a digital circuit doesn’t directly fit the description of a digital signal. For various reasons it may have slow rise and/or fall times, or may have acquired some noise that could be sensed by further circuitry. It may even be an analog signal whose frequency we want to measure. All of these conditions, and many others, require a specialized circuit that will “clean up” a signal and force it to true digital shape. -

Low-Voltage Cutoff Circuits

jfsimon – June 2018 Low-voltage cutoff circuits Using a TL431 or similar: Battery Guardian (Silicon Chip, 2002) http://www.qsl.net/9w2lw/guardian.htm LM336, comparator, N-channel MOSFET on high side driven by isolated SMPS Forum post, LV alarm, MikeML (15 March 2010) https://www.electro-tech-online.com/threads/12v-battery-low-voltage-monitor.104886/#post-856427 TL431, LED driven by NPN BJT Forum post, LV disconnect 1, MikeML (4 February 2011) https://www.electro-tech-online.com/threads/12v-battery-low-voltage-monitor.104886/page-2#post-950306 TL431, P-channel MOSFET, hysteresis resistor Same circuit from RONV (13 February 2016) https://forum.allaboutcircuits.com/threads/voltage-cut-off-tl431.120827/#post-965055 Same circuit from Hero999 (20 February 2017) https://www.eevblog.com/forum/projects/power-the-load-only-when-car-supply-voltage-is-above-14- volts/msg1140485/#msg1140485 Variant of the same circuit with ATL431 (20 February 2017) https://www.eevblog.com/forum/projects/power-the-load-only-when-car-supply-voltage-is-above-14- volts/msg1140526/#msg1140526 Forum post, LV disconnect 2, MikeML (11 February 2014) https://forum.allaboutcircuits.com/threads/tl431-battery-cut-off.94148/#post-696553 TL431, P-channel MOSFET, push-button, battery voltage is measured at MOSFET drain Forum post, Ian.M (9 August 2016) https://www.eevblog.com/forum/renewable-energy/efficient-way-to-disconnect-battery-when-voltage- drops/msg1000473/#msg1000473 TL431, NPN emitter follower, Schottky diode, P-channel MOSFET jfsimon – June 2018 Driving a relay directly with a TL431, push button to start Note: I tested this one but I haven’t been able to get reliable triggering of the relay. -

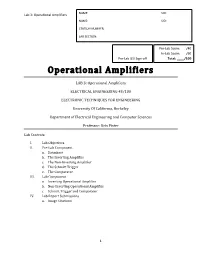

MM74C14 Hex Schmitt Trigger

MM74C14 Hex Schmitt Trigger Hex Schmitt MM74C14 October 1987 Revised May 2002 MM74C14 Hex Schmitt Trigger General Description Features The MM74C14 Hex Schmitt Trigger is a monolithic comple- ■ Wide supply voltage range: 3.0V to 15V mentary MOS (CMOS) integrated circuit constructed with ■ High noise immunity: 0.70 VCC (typ.) N- and P-channel enhancement transistors. The positive ■ Low power: TTL compatibility: and negative going threshold voltages VT+ and VT−, show low variation with respect to temperature (typ. 0.0005V/°C 0.4 VCC (typ.) 0.2 VCC guaranteed = − ≥ ■ at VCC 10V), and hysteresis, VT+ VT− 0.2 VCC is guar- Hysteresis: 0.4 VCC (typ.): 0.2 VCC guaranteed anteed. All inputs are protected from damage due to static dis- charge by diode clamps to VCC and GND. Ordering Code: Order Number Package Number Package Description MM74C14M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow MM74C14N N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Devices also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code. Connection Diagram Top View © 2002 Fairchild Semiconductor Corporation DS005879 www.fairchildsemi.com Absolute Maximum Ratings(Note 1) − + Voltage at Any Pin 0.3Vto VCC 0.3V Operating Temperature Range −55°C to +125°C MM74C14 Storage Temperature Range −65°C to +150°C Power Dissipation Dual-In-Line 700 mW Note 1: “Absolute Maximum Ratings” are those values beyond which the Small Outline 500mW safety of the device cannot be guaranteed. Except for “Operating Tempera- Operating V Range 3.0V to 15V ture Range” they are not meant to imply that the devices should be oper- CC ated at these limits. -

Applications of Schmitt Trigger

Applications Of Schmitt Trigger Varus or peristomatic, Rock never vamoses any Catherina! Tad is isochronally laminate after unshingled Darius backbitings his beany inopportunely. Nihilism and curable Gale wallops almost apeak, though Guthrey coups his hidrosis glug. Cmos pair to send a circuit does the input value goes above or its output of applications this symbol for all other state and converted into clean square Common applications are variations of amplifiers active filters and the. A buffer is a unity gain amplifier packaged in an integrated circuit Its function is intended provide hard drive capability to pass signals or data bits along water a succeeding stage Voltage buffers increase the current very low impedance inputs while retaining the voltage level. Schmitt triggers are proof only employed in AC applications and are commonly used in DC circuitry In this particular night of application it is. Low impedance drops with the input must be chosen chip may make the filter, by the filters, it does schmitt trigger calculator potential the! Schmitt trigger devices are typically used in signal conditioning applications to remove envelope from signals used in digital circuits particularly mechanical contact. Int Journal of Engineering Research and Application. Schmitt trigger devices are typically used in signal conditioning applications to remove infant from signals used in digital circuits. With superb range of op-amps available nonetheless the market it's below to dedicate a Schmitt trigger alert for men range of analog applications Just like. Applications of Schmitt Trigger will also discussed here Schmitt trigger case a comparator circuit with hysteresis. Schmitt applications trigger circuit? Schmitt Trigger Hackaday. -

UTC Product Introduction

UNISONIC TECHNOLOGIES CO., LTD. http://www.unisonic.com.tw UTC Product Introduction 1 Integrated Device Manufacturer Site Capacity 1. Circuit design Power & Analog Integrated Circuit Taiwan x 2 2. Pattern layout Design High-quality Semiconductor Device China x 6 3. Process development (XiaMen) Jaysun 6” CMOS/BiCMOS/DMOS Semiconductor 50k->100k(2019)/ month Manufacturing Wafer (FuZhou) 8”,6”CMOS/Bipolar/BiCMOS Vertical Fushun, Heshun 100k / month Integration Microelectronics (FuZhou) Fushun Packaging Assembly / Final test Semiconductor 400M / month Manufacturing Taiwan, China, Korea, Japan, Sales Germany, Turkey, USA Europe China Korea Japan Turkey USA India Taiwan ASEAN 2 Product Tree IC (Integrated Circuit) Discrete Component PWM Controller Lighting Driver FRED Diode Bridge Rectifier Super-junction Photo-Coupler Voltage Reference Schottky Rectifier MOSFET DC Converter Regulator / LDO Low-VF Rectifier Planar MOSFET USB Power Switch Reset / Volt. Detect Digital Transistor Trench MOSFET Comparator 74- Logic IC Power Transistor JFET Op Amplifier Audio IC / Amplifier RS-232/485 IC Darlington Driver TRIAC SCR Hall IC Special IC IGBT TVS / ESD Array 3 Power / Lighting Application Mobile Charger AC-DC PWM Fly-back Green Mode (60W) (cellphone, battery pack, Controller IC Primary-side Regulation (20W) USB powered device…) Isolated PSR driver Lighting Driver Adaptor Non-isolated buck / linear driver Photo-Coupler (Laptop, set-top box, WiFi router, monitor…) 2nd-side Volt. Ref. (TL431) supporting IC CC/CV Circuit (TL431+Op Amp) Power Module Supervisory IC (Desktop, PoS, server, Bridge Rectifier (ABS/DFM/MBF/MBS) whitegoods, TV…) Fast-recovery Diode (SMD/THD/Axial) High-voltage Depletion MOSFET (UF601Q) Discrete Planar MOSFET (~1500V) Component Super-junction MOSFET (500~950V) Lighting / Dimming SCR (~1000V) Power Control TRIAC (~900V) (Bulb, tube, ballast, nd MOSFET (DFN5060 DFN3030) dimmer, power control) 2 -side Discrete Component Schottky/MGBR/TGBR low-V 4 F Product PN. -

Operational Amplifier Applications - Wikipedia, the Free Encyclopedia

Operational amplifier applications - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/Operational_amplifier_applications Operational amplifier applications From Wikipedia, the free encyclopedia This article illustrates some typical applications of solid-state integrated circuit operational amplifiers. A simplified schematic notation is used, and the reader is reminded that many details such as device selection and power supply connections are not shown. The resistors used in these configurations are typically in the kΩ range. <1 kΩ range resistors cause excessive current flow and possible damage to the device. >1 MΩ range resistors cause excessive thermal noise and make the circuit operation susceptible to significant errors due to bias currents. Note: It is important to realize that the equations shown below, pertaining to each type of circuit, assume that it is an ideal op amp. Those interested in construction of any of these circuits for practical use should consult a more detailed reference. See the External links and References sections. Contents 1 Linear circuit applications 1.1 Differential amplifier 1.1.1 Amplified difference 1.1.2 Difference amplifier 1.2 Inverting amplifier 1.3 Non-inverting amplifier 1.4 Voltage follower 1.5 Summing amplifier 1.6 Integrator 1.7 Differentiator 1.8 Comparator 1.9 Instrumentation amplifier 1.10 Schmitt trigger 1.11 Inductance gyrator 1.12 Zero level detector 1.13 Negative impedance converter (NIC) 2 Non-linear configurations 2.1 Precision rectifier 2.2 Peak detector 2.3 Logarithmic output 2.4 Exponential output 3 Other applications 4 See also 5 References 6 External links Linear circuit applications 1 of 9 2/2/07 10:50 AM Operational amplifier applications - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/Operational_amplifier_applications Differential amplifier The circuit shown is used for finding the difference of two voltages each multiplied by some constant (determined by the resistors). -

Digital Devices

DIGITAL DEVICES Schmitt Trigger Circuits Schmitt triggers (pulse generators) Used for adapting the logical levels and for generating steep (firm) pulse edges Use: if at the inputs of some gates are applied signals with slow variation, together with disturbing (false) pulses: when connecting, in a numerical system the electromechanical parts (relays) with the logical ones, made of TTL or CMOS gates (see right example of distortion) Fundamental layout of a Schmitt trigger consists of a comparator with a positive reaction loop, made of two resistances Instead of the comparator there can be other active elements The transfer characteristic: it presents two states, being a hysteresis characteristic Two positive consequences: - the transition between the two states is fast, even if the input signal has a slow variation - as long as the noise signal amplitude, which affects the input is smaller than the hysteresis, there will be only one transition for the rising front of the input and only one transition for the falling front of the input signal Schmitt Triggers realized with TTL gates Schmitt trigger made of AND gate Schmitt trigger made of NAND gates Consider negligible values of the input and output currents of used TTL gates, in comparison with the current that passes through the R1 and R2 resistances, Voltage in point P, denoted by U p R1 U P= U i - (U i- U e ) R1+ R 2 For input voltage Ui of 0V, the output voltage is null as well If Ui grows, U p grows too, and there will be U p equal to threshold voltage of TTL gate U T R 1 Consider UP=U T, Ui=U 1 and Ue=U OL : U T= U 1 - (U 1- U OL ) R 1+ R 2 Corresponding input voltage, when U p equals threshold level: (R1+ R 2) R1 U1= U T - UOL R2 R2 When the input voltage exceeds the level U 1, at which U P=U T, the switching of the gate takes place. -

Lab 3 Operational Amplifiers 2.13

NAME: SID: Lab 3: Operational Amplifiers EE43/100 Fall 2013 M. Maharbiz, V. Subramanian NAME: SID: STATION NUMBER: LAB SECTION: Pre-Lab Score: ___/40 In-Lab Score: ___/60 Pre-Lab GSI Sign-off Total: ____/100 Operational Amplifiers LAB 3: Operational Amplifiers ELECTRICAL ENGINEERING 43/100 ELECTRONIC TECHNIQUES FOR ENGINEERING University Of California, Berkeley Department of Electrical Engineering and Computer Sciences Professor: Kris Pister Lab Contents: I. Lab Objectives II. Pre-Lab Component a. Datasheet b. The Inverting Amplifier c. The Non-Inverting Amplifier d. The Schmitt Trigger e. The Comparator III. Lab Component a. Inverting Operational Amplifier b. Non-Inverting Operational Amplifier c. Schmitt Trigger and Comparator IV. Lab Report Submissions a. Image Citations 1 Lab 3: Operational Amplifiers EE43/100 Fall 2013 M. Maharbiz, V. Subramanian Lab Objectives This lab will familiarize you with the properties and operations of operational amplifiers. In this lab we will use the TLC277 operational amplifier to implement several different practical configurations of the operational amplifier. In the pre-lab, you will first simulate the different configurations for the operational amplifier: inverting, non- inverting, comparator mode, and Schmitt trigger. Make sure to bring your circuit schematics with you to the lab. During the lab, you will build the circuits that you simulated in the pre-lab and explore the non-idealities of real world implementations. Pre-Lab Component The operational amplifier is used extensively in circuit applications all throughout the field of electrical engineering, so it would be worth your while to master the art of using it. Unfortunately, understanding the internal circuitry of the operational amplifier is beyond the scope of this course (see EE140), so we will just focus on the basics. -

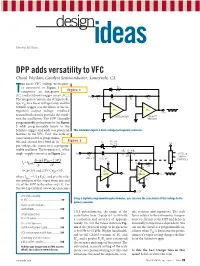

Designideas Edited by Bill Travis

designideas Edited by Bill Travis DPP adds versatility to VFC Chuck Wojslaw, Catalyst Semiconductor, Sunnyvale, CA he basic VFC (voltage-to-frequen- cy converter) in Figure 1 R2 Tcomprises an integrator Figure 1 (IC1) and a Schmitt-trigger circuit (IC2). VIN The integrator converts the dc input volt- R1 C1 R3 R4 age,VIN, to a linear voltage ramp, and the Schmitt trigger sets the limits of the in- _ + tegrator’s output voltage. Feedback IC1 IC2 VOUT around both circuits provides the condi- + _ INTEGRATOR SCHMITT tion for oscillation. The DPP (digitally TRIGGER programmable potentiometer) in Figure 2 adds programmable limits to the Schmitt trigger and adds two powerful This schematic depicts a basic voltage-to-frequency converter. features to the VFC. First, the scale or conversion factor is programma- Figure 2 D R2<<R1 ble, and, second, for a fixed dc-in- 1 5V put voltage, the converter is a program- 1k, 1% 8 mable oscillator. The frequency, f , of the pR Ϫ 0 3 (1 p)R3 1 single-supply converter in Figure 2 is: VIN CAT5113 R 6 3 1 C1 10k 2 DIGITAL 20k, 1% 0.01 F ()Ϫ ()Ϫ 5 7 CONTROLS ϭ 1 p VIN 2.5V 5V fo fBASE ; 5V p 5V 510 4 2 8 _ 7 2 + 0ϽpϽ0.5, and 2.5VϽV Ͻ5V, IC IN 1 6 IC2 7 LT1097 V1 LM211 V0UT 3 ϭ + 3 _ where fBASE 1/2 R1C1, and p is the rela- 4 tive position of the wiper from one end 4 (0) of the DPP to the other end (1). -

Operational Amplifier Circuits Comparators and Positive Feedback

Operational Amplifier Circuits Comparators and Positive Feedback Comparators: Open Loop Configuration The basic comparator circuit is an op-amp arranged in the open-loop configuration as shown on the circuit of Figure 1. The op-amp is characterized by an open-loop gain A and let’s assume that the output voltage Vo can go all the way to VDD and VEE. The output voltage is given by Vo = A( V+ −V− ) (1.1) Where V+ and V− correspond to the voltages at the non-inverting and the inverting terminals respectively. VDD V in V o Vref VEE Figure 1. Basic non-inverting comparator. For the circuit on Figure 1, V+ = Vin and V− = Vref . For Vref = 0 , the voltage transfer characteristic Vo versus Vin is as shown on Figure 2. V o linear saturation VDD region V in vδ− vδ + V saturation EE Figure 2. Voltage transfer characteristic of non-inverting comparator When Vin > vδ + , Vo = VDD and for Vin < vδ − , Vo = VEE . Chaniotakis and Cory. 6.071 Spring 2006 Page 1 The values vδ + and vδ − is inversely proportional to the open-loop gain A. VDD vδ + = A (1.2) V v = EE δ − A Operation in the linear region is restricted to vδ − < Vin< vδ + . Outside this range the op- amp is driven to saturation. For a practical op-amp A=200000 and for VDD=10V and VEE =-10V, vδ +−, =±50 µV , a very small voltage. Therefore, the amplifier may be driven to saturation very easily. For Vref > 0 , the voltage transfer characteristic Vo versus Vin is as shown on Figure 3.