Mathematics and Speed for Interval Arithmetic a Complement to IEEE 1788

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Variable Precision in Modern Floating-Point Computing

Variable precision in modern floating-point computing David H. Bailey Lawrence Berkeley Natlional Laboratory (retired) University of California, Davis, Department of Computer Science 1 / 33 August 13, 2018 Questions to examine in this talk I How can we ensure accuracy and reproducibility in floating-point computing? I What types of applications require more than 64-bit precision? I What types of applications require less than 32-bit precision? I What software support is required for variable precision? I How can one move efficiently between precision levels at the user level? 2 / 33 Commonly used formats for floating-point computing Formal Number of bits name Nickname Sign Exponent Mantissa Hidden Digits IEEE 16-bit “IEEE half” 1 5 10 1 3 (none) “ARM half” 1 5 10 1 3 (none) “bfloat16” 1 8 7 1 2 IEEE 32-bit “IEEE single” 1 7 24 1 7 IEEE 64-bit “IEEE double” 1 11 52 1 15 IEEE 80-bit “IEEE extended” 1 15 64 0 19 IEEE 128-bit “IEEE quad” 1 15 112 1 34 (none) “double double” 1 11 104 2 31 (none) “quad double” 1 11 208 4 62 (none) “multiple” 1 varies varies varies varies 3 / 33 Numerical reproducibility in scientific computing A December 2012 workshop on reproducibility in scientific computing, held at Brown University, USA, noted that Science is built upon the foundations of theory and experiment validated and improved through open, transparent communication. ... Numerical round-off error and numerical differences are greatly magnified as computational simulations are scaled up to run on highly parallel systems. -

Decimal Rounding

Mathematics Instructional Plan – Grade 5 Decimal Rounding Strand: Number and Number Sense Topic: Rounding decimals, through the thousandths, to the nearest whole number, tenth, or hundredth. Primary SOL: 5.1 The student, given a decimal through thousandths, will round to the nearest whole number, tenth, or hundredth. Materials Base-10 blocks Decimal Rounding activity sheet (attached) “Highest or Lowest” Game (attached) Open Number Lines activity sheet (attached) Ten-sided number generators with digits 0–9, or decks of cards Vocabulary approximate, between, closer to, decimal number, decimal point, hundredth, rounding, tenth, thousandth, whole Student/Teacher Actions: What should students be doing? What should teachers be doing? 1. Begin with a review of decimal place value: Display a decimal in the thousandths place, such as 34.726, using base-10 blocks. In pairs, have students discuss how to read the number using place-value names, and review the decimal place each digit holds. Briefly have students share their thoughts with the class by asking: What digit is in the tenths place? The hundredths place? The thousandths place? Who would like to share how to say this decimal using place value? 2. Ask, “If this were a monetary amount, $34.726, how would we determine the amount to the nearest cent?” Allow partners or small groups to discuss this question. It may be helpful if students underlined the place that indicates cents (the hundredths place) in order to keep track of the rounding place. Distribute the Open Number Lines activity sheet and display this number line on the board. Guide students to recall that the nearest cent is the same as the nearest hundredth of a dollar. -

Interval Notation and Linear Inequalities

CHAPTER 1 Introductory Information and Review Section 1.7: Interval Notation and Linear Inequalities Linear Inequalities Linear Inequalities Rules for Solving Inequalities: 86 University of Houston Department of Mathematics SECTION 1.7 Interval Notation and Linear Inequalities Interval Notation: Example: Solution: MATH 1300 Fundamentals of Mathematics 87 CHAPTER 1 Introductory Information and Review Example: Solution: Example: 88 University of Houston Department of Mathematics SECTION 1.7 Interval Notation and Linear Inequalities Solution: Additional Example 1: Solution: MATH 1300 Fundamentals of Mathematics 89 CHAPTER 1 Introductory Information and Review Additional Example 2: Solution: 90 University of Houston Department of Mathematics SECTION 1.7 Interval Notation and Linear Inequalities Additional Example 3: Solution: Additional Example 4: Solution: MATH 1300 Fundamentals of Mathematics 91 CHAPTER 1 Introductory Information and Review Additional Example 5: Solution: Additional Example 6: Solution: 92 University of Houston Department of Mathematics SECTION 1.7 Interval Notation and Linear Inequalities Additional Example 7: Solution: MATH 1300 Fundamentals of Mathematics 93 Exercise Set 1.7: Interval Notation and Linear Inequalities For each of the following inequalities: Write each of the following inequalities in interval (a) Write the inequality algebraically. notation. (b) Graph the inequality on the real number line. (c) Write the inequality in interval notation. 23. 1. x is greater than 5. 2. x is less than 4. 24. 3. x is less than or equal to 3. 4. x is greater than or equal to 7. 25. 5. x is not equal to 2. 6. x is not equal to 5 . 26. 7. x is less than 1. 8. -

Interval Computations: Introduction, Uses, and Resources

Interval Computations: Introduction, Uses, and Resources R. B. Kearfott Department of Mathematics University of Southwestern Louisiana U.S.L. Box 4-1010, Lafayette, LA 70504-1010 USA email: [email protected] Abstract Interval analysis is a broad field in which rigorous mathematics is as- sociated with with scientific computing. A number of researchers world- wide have produced a voluminous literature on the subject. This article introduces interval arithmetic and its interaction with established math- ematical theory. The article provides pointers to traditional literature collections, as well as electronic resources. Some successful scientific and engineering applications are listed. 1 What is Interval Arithmetic, and Why is it Considered? Interval arithmetic is an arithmetic defined on sets of intervals, rather than sets of real numbers. A form of interval arithmetic perhaps first appeared in 1924 and 1931 in [8, 104], then later in [98]. Modern development of interval arithmetic began with R. E. Moore’s dissertation [64]. Since then, thousands of research articles and numerous books have appeared on the subject. Periodic conferences, as well as special meetings, are held on the subject. There is an increasing amount of software support for interval computations, and more resources concerning interval computations are becoming available through the Internet. In this paper, boldface will denote intervals, lower case will denote scalar quantities, and upper case will denote vectors and matrices. Brackets “[ ]” will delimit intervals while parentheses “( )” will delimit vectors and matrices.· Un- derscores will denote lower bounds of· intervals and overscores will denote upper bounds of intervals. Corresponding lower case letters will denote components of vectors. -

A Library for Interval Arithmetic Was Developed

1 Verified Real Number Calculations: A Library for Interval Arithmetic Marc Daumas, David Lester, and César Muñoz Abstract— Real number calculations on elementary functions about a page long and requires the use of several trigonometric are remarkably difficult to handle in mechanical proofs. In this properties. paper, we show how these calculations can be performed within In many cases the formal checking of numerical calculations a theorem prover or proof assistant in a convenient and highly automated as well as interactive way. First, we formally establish is so cumbersome that the effort seems futile; it is then upper and lower bounds for elementary functions. Then, based tempting to perform the calculations out of the system, and on these bounds, we develop a rational interval arithmetic where introduce the results as axioms.1 However, chances are that real number calculations take place in an algebraic setting. In the external calculations will be performed using floating-point order to reduce the dependency effect of interval arithmetic, arithmetic. Without formal checking of the results, we will we integrate two techniques: interval splitting and taylor series expansions. This pragmatic approach has been developed, and never be sure of the correctness of the calculations. formally verified, in a theorem prover. The formal development In this paper we present a set of interactive tools to automat- also includes a set of customizable strategies to automate proofs ically prove numerical properties, such as Formula (1), within involving explicit calculations over real numbers. Our ultimate a proof assistant. The point of departure is a collection of lower goal is to provide guaranteed proofs of numerical properties with minimal human theorem-prover interaction. -

Signedness-Agnostic Program Analysis: Precise Integer Bounds for Low-Level Code

Signedness-Agnostic Program Analysis: Precise Integer Bounds for Low-Level Code Jorge A. Navas, Peter Schachte, Harald Søndergaard, and Peter J. Stuckey Department of Computing and Information Systems, The University of Melbourne, Victoria 3010, Australia Abstract. Many compilers target common back-ends, thereby avoid- ing the need to implement the same analyses for many different source languages. This has led to interest in static analysis of LLVM code. In LLVM (and similar languages) most signedness information associated with variables has been compiled away. Current analyses of LLVM code tend to assume that either all values are signed or all are unsigned (except where the code specifies the signedness). We show how program analysis can simultaneously consider each bit-string to be both signed and un- signed, thus improving precision, and we implement the idea for the spe- cific case of integer bounds analysis. Experimental evaluation shows that this provides higher precision at little extra cost. Our approach turns out to be beneficial even when all signedness information is available, such as when analysing C or Java code. 1 Introduction The “Low Level Virtual Machine” LLVM is rapidly gaining popularity as a target for compilers for a range of programming languages. As a result, the literature on static analysis of LLVM code is growing (for example, see [2, 7, 9, 11, 12]). LLVM IR (Intermediate Representation) carefully specifies the bit- width of all integer values, but in most cases does not specify whether values are signed or unsigned. This is because, for most operations, two’s complement arithmetic (treating the inputs as signed numbers) produces the same bit-vectors as unsigned arithmetic. -

General Topology

General Topology Tom Leinster 2014{15 Contents A Topological spaces2 A1 Review of metric spaces.......................2 A2 The definition of topological space.................8 A3 Metrics versus topologies....................... 13 A4 Continuous maps........................... 17 A5 When are two spaces homeomorphic?................ 22 A6 Topological properties........................ 26 A7 Bases................................. 28 A8 Closure and interior......................... 31 A9 Subspaces (new spaces from old, 1)................. 35 A10 Products (new spaces from old, 2)................. 39 A11 Quotients (new spaces from old, 3)................. 43 A12 Review of ChapterA......................... 48 B Compactness 51 B1 The definition of compactness.................... 51 B2 Closed bounded intervals are compact............... 55 B3 Compactness and subspaces..................... 56 B4 Compactness and products..................... 58 B5 The compact subsets of Rn ..................... 59 B6 Compactness and quotients (and images)............. 61 B7 Compact metric spaces........................ 64 C Connectedness 68 C1 The definition of connectedness................... 68 C2 Connected subsets of the real line.................. 72 C3 Path-connectedness.......................... 76 C4 Connected-components and path-components........... 80 1 Chapter A Topological spaces A1 Review of metric spaces For the lecture of Thursday, 18 September 2014 Almost everything in this section should have been covered in Honours Analysis, with the possible exception of some of the examples. For that reason, this lecture is longer than usual. Definition A1.1 Let X be a set. A metric on X is a function d: X × X ! [0; 1) with the following three properties: • d(x; y) = 0 () x = y, for x; y 2 X; • d(x; y) + d(y; z) ≥ d(x; z) for all x; y; z 2 X (triangle inequality); • d(x; y) = d(y; x) for all x; y 2 X (symmetry). -

IEEE Standard 754 for Binary Floating-Point Arithmetic

Work in Progress: Lecture Notes on the Status of IEEE 754 October 1, 1997 3:36 am Lecture Notes on the Status of IEEE Standard 754 for Binary Floating-Point Arithmetic Prof. W. Kahan Elect. Eng. & Computer Science University of California Berkeley CA 94720-1776 Introduction: Twenty years ago anarchy threatened floating-point arithmetic. Over a dozen commercially significant arithmetics boasted diverse wordsizes, precisions, rounding procedures and over/underflow behaviors, and more were in the works. “Portable” software intended to reconcile that numerical diversity had become unbearably costly to develop. Thirteen years ago, when IEEE 754 became official, major microprocessor manufacturers had already adopted it despite the challenge it posed to implementors. With unprecedented altruism, hardware designers had risen to its challenge in the belief that they would ease and encourage a vast burgeoning of numerical software. They did succeed to a considerable extent. Anyway, rounding anomalies that preoccupied all of us in the 1970s afflict only CRAY X-MPs — J90s now. Now atrophy threatens features of IEEE 754 caught in a vicious circle: Those features lack support in programming languages and compilers, so those features are mishandled and/or practically unusable, so those features are little known and less in demand, and so those features lack support in programming languages and compilers. To help break that circle, those features are discussed in these notes under the following headings: Representable Numbers, Normal and Subnormal, Infinite -

Multidisciplinary Design Project Engineering Dictionary Version 0.0.2

Multidisciplinary Design Project Engineering Dictionary Version 0.0.2 February 15, 2006 . DRAFT Cambridge-MIT Institute Multidisciplinary Design Project This Dictionary/Glossary of Engineering terms has been compiled to compliment the work developed as part of the Multi-disciplinary Design Project (MDP), which is a programme to develop teaching material and kits to aid the running of mechtronics projects in Universities and Schools. The project is being carried out with support from the Cambridge-MIT Institute undergraduate teaching programe. For more information about the project please visit the MDP website at http://www-mdp.eng.cam.ac.uk or contact Dr. Peter Long Prof. Alex Slocum Cambridge University Engineering Department Massachusetts Institute of Technology Trumpington Street, 77 Massachusetts Ave. Cambridge. Cambridge MA 02139-4307 CB2 1PZ. USA e-mail: [email protected] e-mail: [email protected] tel: +44 (0) 1223 332779 tel: +1 617 253 0012 For information about the CMI initiative please see Cambridge-MIT Institute website :- http://www.cambridge-mit.org CMI CMI, University of Cambridge Massachusetts Institute of Technology 10 Miller’s Yard, 77 Massachusetts Ave. Mill Lane, Cambridge MA 02139-4307 Cambridge. CB2 1RQ. USA tel: +44 (0) 1223 327207 tel. +1 617 253 7732 fax: +44 (0) 1223 765891 fax. +1 617 258 8539 . DRAFT 2 CMI-MDP Programme 1 Introduction This dictionary/glossary has not been developed as a definative work but as a useful reference book for engi- neering students to search when looking for the meaning of a word/phrase. It has been compiled from a number of existing glossaries together with a number of local additions. -

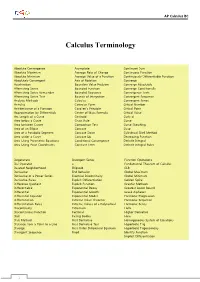

Calculus Terminology

AP Calculus BC Calculus Terminology Absolute Convergence Asymptote Continued Sum Absolute Maximum Average Rate of Change Continuous Function Absolute Minimum Average Value of a Function Continuously Differentiable Function Absolutely Convergent Axis of Rotation Converge Acceleration Boundary Value Problem Converge Absolutely Alternating Series Bounded Function Converge Conditionally Alternating Series Remainder Bounded Sequence Convergence Tests Alternating Series Test Bounds of Integration Convergent Sequence Analytic Methods Calculus Convergent Series Annulus Cartesian Form Critical Number Antiderivative of a Function Cavalieri’s Principle Critical Point Approximation by Differentials Center of Mass Formula Critical Value Arc Length of a Curve Centroid Curly d Area below a Curve Chain Rule Curve Area between Curves Comparison Test Curve Sketching Area of an Ellipse Concave Cusp Area of a Parabolic Segment Concave Down Cylindrical Shell Method Area under a Curve Concave Up Decreasing Function Area Using Parametric Equations Conditional Convergence Definite Integral Area Using Polar Coordinates Constant Term Definite Integral Rules Degenerate Divergent Series Function Operations Del Operator e Fundamental Theorem of Calculus Deleted Neighborhood Ellipsoid GLB Derivative End Behavior Global Maximum Derivative of a Power Series Essential Discontinuity Global Minimum Derivative Rules Explicit Differentiation Golden Spiral Difference Quotient Explicit Function Graphic Methods Differentiable Exponential Decay Greatest Lower Bound Differential -

Calculus Formulas and Theorems

Formulas and Theorems for Reference I. Tbigonometric Formulas l. sin2d+c,cis2d:1 sec2d l*cot20:<:sc:20 +.I sin(-d) : -sitt0 t,rs(-//) = t r1sl/ : -tallH 7. sin(A* B) :sitrAcosB*silBcosA 8. : siri A cos B - siu B <:os,;l 9. cos(A+ B) - cos,4cos B - siuA siriB 10. cos(A- B) : cosA cosB + silrA sirrB 11. 2 sirrd t:osd 12. <'os20- coS2(i - siu20 : 2<'os2o - I - 1 - 2sin20 I 13. tan d : <.rft0 (:ost/ I 14. <:ol0 : sirrd tattH 1 15. (:OS I/ 1 16. cscd - ri" 6i /F tl r(. cos[I ^ -el : sitt d \l 18. -01 : COSA 215 216 Formulas and Theorems II. Differentiation Formulas !(r") - trr:"-1 Q,:I' ]tra-fg'+gf' gJ'-,f g' - * (i) ,l' ,I - (tt(.r))9'(.,') ,i;.[tyt.rt) l'' d, \ (sttt rrJ .* ('oqI' .7, tJ, \ . ./ stll lr dr. l('os J { 1a,,,t,:r) - .,' o.t "11'2 1(<,ot.r') - (,.(,2.r' Q:T rl , (sc'c:.r'J: sPl'.r tall 11 ,7, d, - (<:s<t.r,; - (ls(].]'(rot;.r fr("'),t -.'' ,1 - fr(u") o,'ltrc ,l ,, 1 ' tlll ri - (l.t' .f d,^ --: I -iAl'CSllLl'l t!.r' J1 - rz 1(Arcsi' r) : oT Il12 Formulas and Theorems 2I7 III. Integration Formulas 1. ,f "or:artC 2. [\0,-trrlrl *(' .t "r 3. [,' ,t.,: r^x| (' ,I 4. In' a,,: lL , ,' .l 111Q 5. In., a.r: .rhr.r' .r r (' ,l f 6. sirr.r d.r' - ( os.r'-t C ./ 7. /.,,.r' dr : sitr.i'| (' .t 8. tl:r:hr sec,rl+ C or ln Jccrsrl+ C ,f'r^rr f 9. -

Complete Interval Arithmetic and Its Implementation on the Computer

Complete Interval Arithmetic and its Implementation on the Computer Ulrich W. Kulisch Institut f¨ur Angewandte und Numerische Mathematik Universit¨at Karlsruhe Abstract: Let IIR be the set of closed and bounded intervals of real numbers. Arithmetic in IIR can be defined via the power set IPIR (the set of all subsets) of real numbers. If divisors containing zero are excluded, arithmetic in IIR is an algebraically closed subset of the arithmetic in IPIR, i.e., an operation in IIR performed in IPIR gives a result that is in IIR. Arithmetic in IPIR also allows division by an interval that contains zero. Such division results in closed intervals of real numbers which, however, are no longer bounded. The union of the set IIR with these new intervals is denoted by (IIR). The paper shows that arithmetic operations can be extended to all elements of the set (IIR). On the computer, arithmetic in (IIR) is approximated by arithmetic in the subset (IF ) of closed intervals over the floating-point numbers F ⊂ IR. The usual exceptions of floating-point arithmetic like underflow, overflow, division by zero, or invalid operation do not occur in (IF ). Keywords: computer arithmetic, floating-point arithmetic, interval arithmetic, arith- metic standards. 1 Introduction or a Vision of Future Computing Computers are getting ever faster. The time can already be foreseen when the P C will be a teraflops computer. With this tremendous computing power scientific computing will experience a significant shift from floating-point arithmetic toward increased use of interval arithmetic. With very little extra hardware, interval arith- metic can be made as fast as simple floating-point arithmetic [3].