A Revised I/O Simulation for the HP 21Xx/1000 J

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

1985 , Volume , Issue Apr-1985

HEW LET"TPACKARD CD ei APRIL 19B5 © Copr. 1949-1998 Hewlett-Packard Co. HEW LETT-PACKARD UlÕs)LJ-Ú April 1985 Volume 36 • Number 4 Articles 4 A Low-Cost, Compact, Block-Mode Computer Terminal, by Jean-Louis Chapuis and Michèle in Reliability and ergonomic considerations were given high priority in its design. 7 A Reliable, Low-Cost Keyboard Interface Mechanical Design of a Low-Cost Terminal, by Michel Cauzid Integral display tilt 8 and swivel mechanisms anda detached low-profile keyboard help it adapt to users' needs. 9 VLSI Design in the HP 2392A Terminal, by Jean-Jacques Simon The cost of the CRT control function was reduced 80% by integrating it in a single VLSI chip. 13 A Fast Gate Array Companion for a CRT Controller 15 How to Scroll Smoothly 1O Fully Automated Production of Display Terminal Printed Circuit Assemblies, by D Christian-Marcel Dulphy DIP and axial inserters install 103 components and a six-axis robot inserts 41 more. 1O A Low-Cost, Reliable Analog Video Display Terminal Design, by Rene Martinelli and O Jean Yves Chatron A small cabinet with no fan made heat dissipation a major concern. 23 Authors An Intelligent Plotter for High-Throughput, Unattended Operation, by Martin L Stone, Peter L transparency JefferyW. Groenke, andTodd L Russell A cut-sheet paper or transparency feeder graphics 6g pen acceleration enable users to get multiple copies of presentation graphics quickly and easily. Low-Mass, Low-Cost Pen-Lift Mechanism for High-Speed Plotting, by Tammy V. Herr and Hatem E. Mostafa An adaptive pen up/down cycle reduces pen nib wear without sacrificing plotting speed. -

Características Impresora HP 2100

HP LaserJet 2100, HP LaserJet 2100 2100 2100M M, 2100TN 2100 Printers TN Printers User Guide • User Guide Copyright© 1998 Hewlett-Packard Co. Printed in Germany Manual Part No. C4170-90901 *C4170-90901* Printed on *C4170-90901* Recycled Paper C4170-90901 HP LaserJet 2100, 2100 M, and 2100 TN Printers User Guide _________________ © Copyright Hewlett-Packard Warranty Trademark Credits Company 2002 The information contained in Adobe®, Acrobat®, PostScript®, All Rights Reserved. this document is subject to and Adobe Photoshop® are Reproduction, adaptation, or change without notice. trademarks of Adobe Systems translation without prior written Hewlett-Packard makes no Incorporated which may be permission is prohibited, except warranty of any kind with registered in certain as allowed under the copyright respect to this information. jurisdictions. laws. HEWLETT-PACKARD Arial®, Monotype®, and Times Publication number: SPECIFICALLY DISCLAIMS New Roman® are U.S. THE IMPLIED WARRANTY OF C4170-90901 registered trademarks of the MERCHANTABILITY AND Monotype Corporation. Second Edition, January 2002 FITNESS FOR A PARTICULAR PURPOSE. CompuServe™ is a U.S. trademark of CompuServe, Inc. Hewlett-Packard shall not be liable for any direct, indirect, Helvetica™, Palatino™, Times™, incidental, consequential, or and Times Roman™ are other damage alleged in trademarks of Linotype AG and/ connection with the furnishing or or its subsidiaries in the U.S. use of this information. and other countries. Microsoft®, MS Windows, Windows®, and Windows NT® are U.S. registered trademarks of Microsoft Corporation. LaserWriter® is a registered trademark of Apple Computer, Inc. TrueType™ is a U.S. trademark of Apple Computer, Inc. ENERGY STAR® is a U.S. -

Measure for the Men and Women Or Hewlett-Packard F MAY 19N

Measure For the men and women or Hewlett-Packard f MAY 19n • ICs the HP way (pages 2-6) • Revised Corporate Objectives (pages 7-10) • The role of enterprise (pages 11-13) • Lucky young lady (pages 14-15) The miracle in asmall package HP's big stake in the Ie revolution o The introduction of HP's 9100A desktop calculator in 1968 was hailed as a technological milestone. The 91 OOA could solve problems in science and engi neering that had been beyond the reach of earlier electronic calculators, even In a speech to Stanford graduate stu outperforming some computers of its day. It could be programmed with mag dents and alumni last November, HP netic cards so that complex problems could be solved with a fe\'l keystrokes. Executive Vice President John Young And it was no bigger than an office typewriter. which was quite an accomplish commented on the dramatic progress of ment at the time. IC technology. "In 1960," he said, "simple minicomputers would typically need Today that same capability - and a little more - is packed in a pocket 10,000 separate, discrete transistors, each sized, battery-powered version, the HP-67. It weighs only 11 ounces - 58 times made on a single chip of silicon. Then less than the 9100A. came the integrated circuit revolution. By The reason for this tremendous reducing act in less thEm a decade? Inte 1965 there were commercially available grated circuits. Tiny devices that combine thousands of circuit elements on a ICs that combined about ten transistors, single silicon chip. The Ie, third-generation descendant of the vacuum tube with all their interconnections. -

Microprogramming and Its Relationship to Emulation and Technology*

MICROPROGRAMMING AND ITS RELATIONSHIP TO EMULATION AND TECHNOLOGY* Samuel H. Fuller and Victor R. Lesser Carnesie-Mellon University Pittsburgh, Pennsylvania C. Gordon Bell and Charles Kaman Digital Equipment Corporation Maynard, Massachusetts ABSTRACT data paths; or features of a processor's realization, such as the speed of main memory to that of the control (micro-) This paper is a survey of the development and future memory, are easily rejected on the basis of existing trends in rnicroprograrnrning. We show how the structure of processors that are commonly recosnized to be rnicroprograrnmed processors has been shaped primarily by microprogramrned processors yet do not possess the required two factors= the state of (semiconductor) technology and the features. task of emulation. The other main theme of this article is that it is a fruitless exercise to try to characterize and understand Most of this confusion in alternative definitions of microprograrnming in terms of how it differs from 'regular' microprograrnrning comes from the fact that it has been used programming. The right approach to understanding in two very different ways: (1) in a technological manner to microprogramrning is to recognize that it is primarily applied economically implement a complex instruction set or a small to the task of emulation (interpretation). Through this number of different instruction sets on a single processor, approach the evolution of rnicroprograrnming, independent of and (2) in a software manner to provide programmers with an a particular technology and type of instruction set being extra degree of representational freedom, i.e. develop emulated, is reviewed and future trends indicated. multiple instruction sets, each one appropriate for a particular task domain. -

HP3000 Evolution

HP3000 Evolution -Homestead -Tune Up -Migrate Edited by Bob Green. From articles written by Robelle, by The 3000 Newswire, and by experts in the HP 3000 field: Chris Edler, Paul Edwards, Marius Schild, Neil Armstrong, John Burke, Alan Wyman and Alan Heter, Stan Sieler and Gavin Scott, Ken Robertson, Eugene Volokh (VESoft), Alfredo Rego, Fred White, Steve Hammond, Wayne Boyer, Alan Yeo, Gunnar Fredlund, Terry O'Brien, Michael Marxmeier, Aaron Holmes, Dave Lo, and Glenn Cole. Copyright © 2003-2004 Robelle Solutions Technology Inc. Articles included in this book are courtesy of individual authors and respective copyright owners. Original copyrights are applicable to each article. Updated Friday, May 07, 2004 Qedit and Suprtool are trademarks of Robelle Solutions Technology Inc. HP is a trademark of the Hewlett-Packard Company. Windows is a trademark of Microsoft Corporation. Other product and company names mentioned herein may be the trademarks of their respective owners. PRINTED IN CANADA Robelle Solutions Technology Inc. 7360 137 Street, Suite 372 Surrey, B.C. Canada V3W 1A3 Phone: 604.501.2001 Fax: 604.501.2003 E-mail: [email protected] E-mail: [email protected] Web: www.robelle.com Contents Introduction 1 Migrate, Homestead, or Evolve?................................................................................................1 The Future....................................................................................................................2 Updates to HP 3000 Evolution ....................................................................................3 -

HP 2100 Simulator User's Guide

HP 2100 Simulator User’s Guide 29-Apr-2021 COPYRIGHT NOTICE The following copyright notice applies to the SIMH source, binary, and documentation: Original code published 1993-2012, written by Robert M Supnik Copyright © 1993-2012, Robert M Supnik Copyright © 2012-2021, J. David Bryan Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions: The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software. THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE. Except as contained in this notice, the names of the authors shall not be used in advertising or otherwise to promote the sale, use, or other dealings in this Software without prior written authorization from the authors. 1 1 Introduction.......................................................................................................................................4 -

MESSAGE from YOUR EDITOR. . . MAKE WAY for REMOTE PROCESSING Programmable Controller Joins HP's 3000 Lineup ONE SYSTEM

JULYIAUGUST 1974 Volume 1 Number 4 A 'MINI' MESSAGE FROM YOUR creases the number of channels to 31. Memory EDITOR. I can also be expanded to 32K. The 30300A is accessed through the file system of the 3000 Multiprogramming Executive (MPE) and can be located up to 250 feet away. User-written programs can monitor and control the application program executing the Controller, thanks to the supplied software. Data transfer be- tween the Controller and 3000, besides Controller operation, works through 3000 and 2100 appli- cation programs. HP terminals can access an application program, provide terminal control of the controller, and direct input and output. Programs loaded by the Controller can be stored as 3000 files in absolute binary format, and can be down-loaded from the 3000 to the Controller. The absolute binary code is automatically loaded into the 2100 and executed. The link between 3000 application programs and the Controller is imme- diately established and ready for data transfer or command information flow. Contact your local sales representative for details. New "Computer News" Editor Linda Schefter. Welcome to Hewlett-Packard's fourth "Computer News" editon - and my first! I'm Linda Schefter and recently joined the HP family as editor of this newsletter. I'm excited about our pi-oducts and hope you will be, too. With the changeover, we skipped our April/May edition, but filled this issue with lots of HP news we want to share with all of you. MAKE WAY FOR REMOTE PROCESSING Programmable Controller Joins HP's 3000 Lineup Another addition to the HP 3000 family? Now HP HP's new 21MX series for OEM's. -

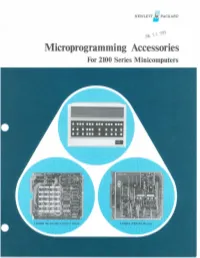

Microprogramming Accessories for 2100 Series Minicomputers, 1973

Microprogramming Accessories For 2100 Series Minicomputers I - WRITEABLE CONTROL STORE (WCS) WRITEABLE CONTROL STORE The Writeable Control Store (WCS) Card contains Features semi-conductor random access memory for storage of s Incorporates microprograms into computer microprograms. Each card contains 256 24-bit words. hardware. Up to three WCS cards can be inserted in the com- 256 24-bit word storage for microprograms. puter mainframe. Enables access to six additional high-speed The instruction word format as stored on the WCS is: registers. s: 196 nanosecond cycle time. Dynamically alterable. Field: ReadIWrite capability from memory and disc. You can even have your own library of microprograms on disc and transfer them to the WCS card as needed. MICROPROGRAMMING After execution, the microprograms can be swapped A microprogram is a computer program written with with other microprograms on the disc or left on the advanced, concise instructions that are stored in com- WCS card. puter hardware rather than in memory. This makes it possible to execute microprograms from 5 to 10 times By such use of microprograms and disc files, you can faster than ordinary software subroutines. In addition dynamically alter the 2100 , configuring its power and your subroutines can be coded using a fraction of the speed to your specific purposes. The computer can instruction words needed for conventional programming. thus be customized to entirely different system functions Microprograms are expressed in 24-bit, 6 field format. as quickly as microprograms can be transferred from These powerful instructions are executed in a mere 196 disc files. nanoseconds. All this not only saves vast memory space, but reduces execution time to a fraction of The microprograms that will not change can be per- conventional computing time. -

UPFRONT Editor: Brad Whitworth HP Graphics Play Heavy Role Art Director: a Annette Yatovitz in Box-Office Smash

UPFRONT Editor: Brad Whitworth HP graphics play heavy role Art director: a Annette Yatovitz in box-office smash. Associate editors: Betty Gerard Joanne Engelhardt Contributors: omputer securityis making could view the overall effect ofthe pro Gregg Piburn headlines around the world. (See posed graphics display at anygiven Karen Gervais C storyon page 16 bystaffer Betty point in the script. Gerard about HP's own efforts in the The final images were all created on a Circulation: field.) But HP also helped dramatize single design station using a desktop Kathleen Gogarty the problem through a supporting role computerconnectedwith an HP 9874A in the movie "WarGames." digitizer onwhich the draWings were In the spectacular closingscenes of done. The large size (up to 18 feet) of the movie. tension builds in the make the war-room screens meant the com believe U.S. defense command post. putergraphics had to be photographed MEASURE Wall screens and computer terminals from a very high-resolution vector dis "Man is the measure of all things." around the room flash with the chang play (the HP 1345A) driving an HP -Protagoras (circa 481-411 B.C.) ing pattern ofapproachingenemy 1336Adisplay tube. The huge mass of nuclear missiles. draWings was stored on an HP flexible Measure is published six times a It's all a skillful illusion created by disc drive. then played back-one year for employees and associates computergraphics consultantColin frame at a time-by three otherdesk ofHewlett-Packard Company. Pro Cantwell. using four HP 9845C desk top computers. each connected to a duced by Corporate Public Rela top computers alongwith other HP motion picture camera by a 16-bit tions. -

Title Cross Assembler/Editor Program of HP2100 to Use INTEL 8085

Cross Assembler/Editor Program of HP2100 to Use INTEL Title 8085 Author(s) Higo, Toshiyasu; Iwashita, Yoshihisa Bulletin of the Institute for Chemical Research, Kyoto Citation University (1980), 58(1): 1-4 Issue Date 1980-03-31 URL http://hdl.handle.net/2433/76866 Right Type Departmental Bulletin Paper Textversion publisher Kyoto University Bull. Inst. Chem. Res., Kyoto Univ., Vol. 58, No. 1, 1980 Cross Assembler/Editor Program of HP2100 to Use INTEL 8085 ToshiyasuHIGO and Yoshihisa IwASxmTA* ReceivedNovember 25,1979 To savethe timeof programmingof a microprocessor INTEL 8085, a programof crossas- semblerwith editor was developed. This program is executedon a minicomputerHP2100 and is writtenin FORTRANII and ASSEMBLER.By the useof thisprogram and a systemof the HP2I00,the timeof programmingis saved by an orderof magnitudecompared to the caseof hand-assembling. KEY WORDS: Computer program / Cross Assembler with Editor / INTEL 8085 / I. INTRODUCTION Program development is a very much time-consuming work when one wants to use a microprocessor (NP). However, if a large computer system is available, one can lessen the time of programming remarkably by providing a translation program of the computer system, fit to the specified pP.1) This program (cross assembler) translates the symbolic source language instructions into object codes. We report here a Cross Assembler/Editor program of a minicomputer HP2100~) developed in our laboratory to use the INTEL 8085. II. FUNCTIONS OF CROSS ASSEMBLER/EDITOR II-1. Principle A primitive method to run a pP is to load it with the machine codes. However this method needs a very tedious work of hand-assembling. This work can be omitted by the use of a minicomputer run with Cross Assembler/Editor program. -

Hewlett-Packard 2100 Processor Description, 1972

Processor de :ription The 2100 is designed to fit a variety of needs. A computer is an effective problem-solver The 1/0structure of the computer is designed only when it adapts easily and inexpensively so a single interface card is all that is usually to the problems of the outside world. The needed to interface to a peripheral or debate of one specification over another is instrument. Hewlett-Packard offers cards to relevant only to the specificproblem. The 2100 interface to over 30 HP supported peripherals was designed so that you can tailor your and over 100 scientific instruments. And, configuration with proven software and general-purpose interface cards are available so peripherals. And, with writeable control store that your special instrument or peripheral will you can easily enhance the instruction set of the have inexpensive access to the 2100. processor to optimize your programs. So when Software-we have it. Standard languages you need it, the 21 00 can be customized include, FORTRAN I1 and IV, Assembly to solve a particular problem. Language, ALGOL, and HP Extended BASIC. All these capabilities are provided without For your application needs, a library of over sacrificing the features of a general-purpose 500 user-contributed routines are available. HP minicomputer. Standard equipment includes software has been field tested in over 4000 80 powerful instructions, hardware multiply/ installations. It provides proven capability with divide, memory protect, power fail with complete documentation. automatic restart, unlimited levels of indirect The 2 100 is the processor of a number of HP addressing, 14 1/0channels, and many more. -

HP 2100 Simulator User's Guide 23-May-2018

HP 2100 Simulator User’s Guide 23-May-2018 COPYRIGHT NOTICE The following copyright notice applies to the SIMH source, binary, and documentation: Original code published 1993-2012, written by Robert M Supnik Copyright © 1993-2012, Robert M Supnik Copyright © 2012-2018, J. David Bryan Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions: The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software. THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE. Except as contained in this notice, the names of the authors shall not be used in advertising or otherwise to promote the sale, use, or other dealings in this Software without prior written authorization from the authors. 1 1 Introduction ...................................................................................................................................... 4 1.1 The HP 21xx/1000 Computer Systems ............................................................................................ 4 1.2 Simulator Files .................................................................................................................................. 5 2 Simulator Features ...........................................................................................................................