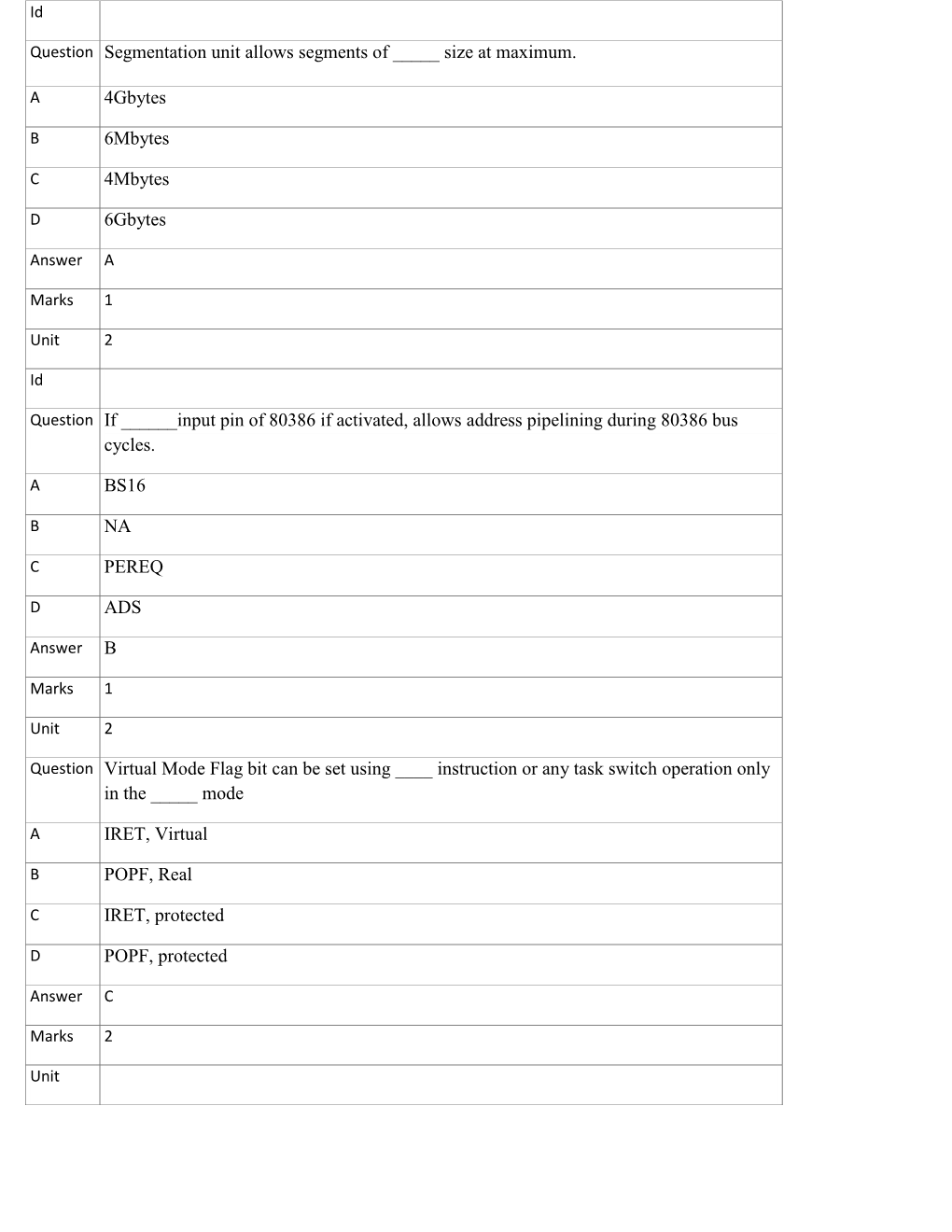

Id Question Segmentation Unit Allows Segments Of

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 3 System Calls, Exceptions, and Interrupts

DRAFT as of September 29, 2009: Copyright 2009 Cox, Kaashoek, Morris Chapter 3 System calls, exceptions, and interrupts An operating system must handle system calls, exceptions, and interrupts. With a system call a user program can ask for an operating system service, as we saw at the end of the last chapter. Exceptions are illegal program actions that generate an inter- rupt. Examples of illegal programs actions include divide by zero, attempt to access memory outside segment bounds, and so on. Interrupts are generated by hardware de- vices that need attention of the operating system. For example, a clock chip may gen- erate an interrupt every 100 msec to allow the kernel to implement time sharing. As another example, when the disk has read a block from disk, it generates an interrupt to alert the operating system that the block is ready to be retrieved. In all three cases, the operating system design must range for the following to happen. The system must save user state for future transparent resume. The system must be set up for continued execution in the kernel. The system must chose a place for the kernel to start executing. The kernel must be able to retrieve information about the event, including arguments. It must all be done securely; the system must main- tain isolation of user processes and the kernel. To achieve this goal the operating system must be aware of the details of how the hardware handles system calls, exceptions, and interrupts. In most processors these three events are handled by a single hardware mechanism. -

Virtual Memory in X86

Fall 2017 :: CSE 306 Virtual Memory in x86 Nima Honarmand Fall 2017 :: CSE 306 x86 Processor Modes • Real mode – walks and talks like a really old x86 chip • State at boot • 20-bit address space, direct physical memory access • 1 MB of usable memory • No paging • No user mode; processor has only one protection level • Protected mode – Standard 32-bit x86 mode • Combination of segmentation and paging • Privilege levels (separate user and kernel) • 32-bit virtual address • 32-bit physical address • 36-bit if Physical Address Extension (PAE) feature enabled Fall 2017 :: CSE 306 x86 Processor Modes • Long mode – 64-bit mode (aka amd64, x86_64, etc.) • Very similar to 32-bit mode (protected mode), but bigger address space • 48-bit virtual address space • 52-bit physical address space • Restricted segmentation use • Even more obscure modes we won’t discuss today xv6 uses protected mode w/o PAE (i.e., 32-bit virtual and physical addresses) Fall 2017 :: CSE 306 Virt. & Phys. Addr. Spaces in x86 Processor • Both RAM hand hardware devices (disk, Core NIC, etc.) connected to system bus • Mapped to different parts of the physical Virtual Addr address space by the BIOS MMU Data • You can talk to a device by performing Physical Addr read/write operations on its physical addresses Cache • Devices are free to interpret reads/writes in any way they want (driver knows) System Interconnect (Bus) : all addrs virtual DRAM Network … Disk (Memory) Card : all addrs physical Fall 2017 :: CSE 306 Virt-to-Phys Translation in x86 0xdeadbeef Segmentation 0x0eadbeef Paging 0x6eadbeef Virtual Address Linear Address Physical Address Protected/Long mode only • Segmentation cannot be disabled! • But can be made a no-op (a.k.a. -

Windows Security Hardening Through Kernel Address Protection

Windows Security Hardening Through Kernel Address Protection Mateusz \j00ru" Jurczyk August 2011 Abstract As more defense-in-depth protection schemes like Windows Integrity Control or sandboxing technologies are deployed, threats affecting local system components become a relevant issue in terms of the overall oper- ating system user's security plan. In order to address continuous develop- ment of Elevation of Privileges exploitation techniques, Microsoft started to enhance the Windows kernel security, by hardening the most sensitive system components, such as Kernel Pools with the Safe Unlinking mecha- nism introduced in Windows 7[19]. At the same time, the system supports numerous both official and undocumented services, providing valuable in- formation regarding the current state of the kernel memory layout. In this paper, we discuss the potential threats and problems concerning un- privileged access to the system address space information. In particular, we also present how subtle information leakages can prove useful in prac- tical attack scenarios. Further in the document, we conclusively provide some suggestions as to how problems related to kernel address information availability can be mitigated, or entirely eliminated. 1 Introduction Communication between distinct executable modules running at different priv- ilege levels or within separate security domains takes place most of the time, in numerous fields of modern computing. Both hardware- and software-enforced privilege separation mechanisms are designed to control the access to certain re- sources - grant it to modules with higher rights, while ensuring that unathorized entities are not able to reach the protected data. The discussed architecture is usually based on setting up a trusted set of modules (further referred to as \the broker") in the privileged area, while hav- ing the potentially malicious code (also called \the guest") executed in a con- trolled environment. -

Chapter 3 Protected-Mode Memory Management

CHAPTER 3 PROTECTED-MODE MEMORY MANAGEMENT This chapter describes the Intel 64 and IA-32 architecture’s protected-mode memory management facilities, including the physical memory requirements, segmentation mechanism, and paging mechanism. See also: Chapter 5, “Protection” (for a description of the processor’s protection mechanism) and Chapter 20, “8086 Emulation” (for a description of memory addressing protection in real-address and virtual-8086 modes). 3.1 MEMORY MANAGEMENT OVERVIEW The memory management facilities of the IA-32 architecture are divided into two parts: segmentation and paging. Segmentation provides a mechanism of isolating individual code, data, and stack modules so that multiple programs (or tasks) can run on the same processor without interfering with one another. Paging provides a mech- anism for implementing a conventional demand-paged, virtual-memory system where sections of a program’s execution environment are mapped into physical memory as needed. Paging can also be used to provide isolation between multiple tasks. When operating in protected mode, some form of segmentation must be used. There is no mode bit to disable segmentation. The use of paging, however, is optional. These two mechanisms (segmentation and paging) can be configured to support simple single-program (or single- task) systems, multitasking systems, or multiple-processor systems that used shared memory. As shown in Figure 3-1, segmentation provides a mechanism for dividing the processor’s addressable memory space (called the linear address space) into smaller protected address spaces called segments. Segments can be used to hold the code, data, and stack for a program or to hold system data structures (such as a TSS or LDT). -

Intel 64 and IA-32 Architectures Software Developer's Manual

SYSTEM ARCHITECTURE OVERVIEW Physical Address EFLAGS Register Code, Data or Linear Address Stack Segment Control Registers Task-State CR4 Segment Selector Segment (TSS) Task CR3 Code CR2 Register CR1 Data Stack CR0 Global Descriptor Task Register Table (GDT) Interrupt Handler Segment Sel. Seg. Desc. Code Current Interrupt TSS Seg. Sel. TSS Desc. TSS Stack Vector Seg. Desc. Interrupt Descriptor Task-State Segment (TSS) Table (IDT) TSS Desc. Task Code Interrupt Gate LDT Desc. Data Stack Task Gate GDTR Trap Gate Local Descriptor Exception Handler Table (LDT) Code Current TSS Stack IDTR Call-Gate Seg. Desc. Segment Selector Call Gate Protected Procedure Code XCR0 (XFEM) LDTR Current TSS Stack Linear Address Space Linear Address Dir Table Offset Linear Addr. Page Directory Page Table Page Physical Addr. Pg. Dir. Entry Pg. Tbl. Entry 0 This page mapping example is for 4-KByte pages CR3* and the normal 32-bit physical address size. *Physical Address Figure 2-1. IA-32 System-Level Registers and Data Structures Vol. 3 2-3 SYSTEM ARCHITECTURE OVERVIEW 31 22 21 20 19 18 17 16 15 1413 12 11 10 9 8 7 6 5432 1 0 I V V I A V R N O O D I T S Z A P C Reserved (set to 0) I I 0 0 0 1 D C M F T P F F F F F F F F F P F L ID — Identification Flag VIP — Virtual Interrupt Pending VIF — Virtual Interrupt Flag AC — Alignment Check VM — Virtual-8086 Mode RF — Resume Flag NT — Nested Task Flag IOPL— I/O Privilege Level IF — Interrupt Enable Flag TF — Trap Flag Reserved Figure 2-4. -

Chapter 1: Introduction

Access Control in Practice CS461/ECE422 Fall 2009 1 Reading • Computer Security – Chapter 15 2 Outline • Evolution of OS • Object Access Control – Access control lists – Capabilities 3 In the Beginning... • The program owned the machine – Access all power of the hardware – Could really mess things up • Executives emerged – Gather common functionality • Multi-user systems required greater separation – Multics, the source of much early OS development 4 Protecting objects • Desire to protect logical entities – Memory – Files or data sets – Executing program – File directory – A particular data structure like a stack – Operating system control structures – Privileged instructions Access Control Matrix • Access Control Matrix (ACM) and related concepts provides very basic abstraction – Map different systems to a common form for comparison – Enables standard proof techniques – Not directly used in implementation 6 Definitions • Protection state of system – Describes current settings, values of system relevant to protection • Access control matrix – Describes protection state precisely – Matrix describing rights of subjects – State transitions change elements of matrix 7 Description objects (entities) o1 … om s1 … sn • Subjects S = { s1,…,sn } s1 • Objects O = { o1,…,om } s 2 • Rights R = { r1,…,rk } ⊆ • Entries A[si, oj] R subjects … • A[si, oj] = { rx, …, ry } sn means subject si has rights rx, …, ry over object oj 8 Practical object access control • Can slice the logical ACM two ways – By row: Store with subject – By column: Store with object -

![Downloads/Kornau-Tim--Diplomarbeit--Rop.Pdf [34] Sebastian Krahmer](https://docslib.b-cdn.net/cover/8658/downloads-kornau-tim-diplomarbeit-rop-pdf-34-sebastian-krahmer-1798658.webp)

Downloads/Kornau-Tim--Diplomarbeit--Rop.Pdf [34] Sebastian Krahmer

CFI CaRE: Hardware-supported Call and Return Enforcement for Commercial Microcontrollers Thomas Nyman Jan-Erik Ekberg Lucas Davi N. Asokan Aalto University, Finland Trustonic, Finland University of Aalto University, Finland [email protected] [email protected] Duisburg-Essen, [email protected] Trustonic, Finland Germany thomas.nyman@ lucas.davi@wiwinf. trustonic.com uni-due.de ABSTRACT CFI (Section 3.1) is a well-explored technique for resisting With the increasing scale of deployment of Internet of Things (IoT), the code-reuse attacks such as Return-Oriented Programming concerns about IoT security have become more urgent. In particular, (ROP) [47] that allow attackers in control of data memory to subvert memory corruption attacks play a predominant role as they allow the control flow of a program. CFI commonly takes the formof remote compromise of IoT devices. Control-flow integrity (CFI) is inlined enforcement, where CFI checks are inserted at points in the a promising and generic defense technique against these attacks. program code where control flow changes occur. For legacy applica- However, given the nature of IoT deployments, existing protection tions CFI checks must be introduced by instrumenting the pre-built mechanisms for traditional computing environments (including CFI) binary. Such binary instrumentation necessarily modifies the mem- need to be adapted to the IoT setting. In this paper, we describe ory layout of the code, requiring memory addresses referenced by the challenges of enabling CFI on microcontroller (MCU) based the program to be adjusted accordingly [28]. This is typically done IoT devices. We then present CaRE, the first interrupt-aware CFI through load-time dynamic binary rewriting software [14, 39]. -

Empirical Performance Comparison of Hardware and Software Task Context Switching

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Calhoun, Institutional Archive of the Naval Postgraduate School Calhoun: The NPS Institutional Archive Theses and Dissertations Thesis Collection 2009-06 Empirical Performance Comparison of Hardware and Software Task Context Switching Schultz, Eric A. Monterey, California. Naval Postgraduate School http://hdl.handle.net/10945/46226 NAVAL POSTGRADUATE SCHOOL MONTEREY, CALIFORNIA THESIS EMPIRICAL PERFORMANCE COMPARISON OF HARDWARE AND SOFTWARE TASK CONTEXT SWITCHING by Eric A. Schultz June 2009 Thesis Advisor: Cynthia E. Irvine Second Reader: David J. Shifflett Approved for public release; distribution is unlimited THIS PAGE INTENTIONALLY LEFT BLANK ii Form Approved REPORT DOCUMENTATION PAGE OMB No. 0704–0188 The public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden to Department of Defense, Washington Headquarters Services, Directorate for Information Operations and Reports (0704–0188), 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202–4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to any penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. PLEASE DO NOT RETURN YOUR FORM TO THE ABOVE ADDRESS. 1. REPORT DATE (DD–MM–YYYY) 2. REPORT TYPE 3. -

Principles of Operating Systems Lecture 12: Interrupts and Exceptions

ICS143A: Principles of Operating Systems Lecture 12: Interrupts and Exceptions (part 2) Anton Burtsev November, 2017 Privilege levels again Started boot: no CPL yet Prepare to load GDT entry #1 Privilege levels ● Each segment has a privilege level ● DPL (descriptor privilege level) ● 4 privilege levels ranging 0-3 Now CPL=0. We run in the kernel iret: return to user, load GDT #4 Run in user, CPL=3 Privilege levels ● Currently running code also has a privilege level ● “Current privilege level” (CPL): 0-3 ● It is saved in the %cs register Privilege level transitions ● CPL can access only less privileged segments – E.g., 0 can access 1, 2, 3 ● Some instructions are “privileged” ● Can only be invoked at CPL = 0 ● Examples: – Load GDT – MOV <control register> ● E.g. reload a page table by changing CR3 Real world ● Only two privilege levels are used in modern OSes: ● OS kernel runs at 0 ● User code runs at 3 ● This is called “flat” segment model ● Segments for both 0 and 3 cover entire address space ● But then... how the kernel is protected? Page table: user bit ● Each entry (both Level 1 and Level 2) has a bit ● If set, code at privilege level 3 can access ● If not, only levels 0-2 can access ● Note, only 2 levels, not 4 like with segments ● All kernel code is mapped with the user bit clear ● This protects user-level code from accessing the kernel Back to interrupts Recap: interrupt path, no PL change Processing of interrupt (cross PL) ● Assume we're at CPL =3 (user) Interrupt descriptor ● Interrupt is allowed ● If current privilege level (CPL) -

Segmentation, Protected Mode

Copyright Notice CS 410/510 • These slides are distributed under the Creative Commons Languages & Low-Level Programming Attribution 3.0 License • You are free: Mark P Jones • to share—to copy, distribute and transmit the work Portland State University • to remix—to adapt the work • under the following conditions: Fall 2018 • Attribution: You must attribute the work (but not in any way that suggests that the author endorses you or your use of the work) as follows: “Courtesy of Mark P. Jones, Portland State University” Week 3: Segmentation, Protected Mode, Interrupts, and Exceptions The complete license text can be found at http://creativecommons.org/licenses/by/3.0/legalcode !1 2 General theme for the next two weeks Diagrams and Code • In a complex system … • There are a lot of diagrams on these slides • Many of these are taken directly from the “Intel® 64 and App App App App App IA-32 Architectures Software Developer’s Manual”, Operating System Operating System particularly Volume 3 Microkernel • There is a link to the full pdf file in the Reference section Hardware • There is also a lot of code on these slides • Remember that you can study these more carefully later if • Question: how can we protect individual programs from you need to! interference with themselves, or with one another, either directly or by subverting lower layers? • General approach: leverage programmable hardware features! 3 4 Taking stock: Code samples ... so far vram video RAM simulation vram.tar.gz hello boot and say hello on bare metal, via hello.tar.gz GRUB simpleio a simple library for video RAM I/O Segmentation bootinfo display basic boot information from (or: where do “seg faults” come from?) GRUB baremetal.tar.gz mimg memory image bootloader & make tool example-mimg display basic boot information from mimgload example-gdt basic demo using protected mode segments (via a Global Descriptor Table) prot.tar.gz example-idt context switching to user mode (via an Interrupt Descriptor Table) 5 6 BASIC EXECUTION ENVIRONMENT • General-purpose registers. -

Processor Address Space

Agenda ❑ Programming Model ❑ Linux ❑ x86 ❑ Architecture and respective adaption ❑ Memory ❑ Exceptions / Interrupts ❑ Multiprocessing 1 References ❑ Understanding the Linux Kernel, Bovet and Cesati ❑ Linux Device Drivers, Rubini ❑ 2.2.18 ❑ lxr.linux.no ❑ http://os.inf.tu-dresden.de/dxr 2 Linux Kernel 3 IRQ - arch. Independent ❑ IRQ Handler ❑ irq_desc array ❑ irq_action for interrupt sharing ❑ Execution Modell ❑ Top Half ❑ Bottom Half ❑ Dynamic Management 4 IRQ - arch. Dependent ❑ CPU interrupt delivery ❑ Entering to ❑ Returning from ❑ Interrupt controller ❑ enabling/disabling ❑ Switch to kernel stack 5 Memory - arch. Independent ❑ Process ❑ VMA , logical segmentation ❑ 3 - level page table ❑ Physical Memory ❑ Page frame ❑ Memory areas ❑ Non-contiguous memory areas 6 Memory - arch. Dependent ❑ x86 - Architecture ❑ Segmentation ❑ Paging ❑ 2 - level ❑ 4k and 4M pages ❑ 2M for PAE.... 7 Address generation 8 Address Generation (2) 9 Segment Descriptors ❑ 8-Byte representation in gdt or ldt ❑ Address generation ❑ 32-bit Base ❑ 20-bit Limit ❑ Protection ❑ 2-bit Privilege level ❑ Type ❑ 4-bit Type field 10 Global Descriptor Table ❑ Manipulation ❑ lgdt ❑ load global descriptor table ❑ sgdt ❑ store global descriptor table struct pdesc{ short pad; unsigned short limit; unsigned long linear_base; }; struct pdesc pd; asm volatile("sgdt %0" : :"m" ((pd)->limit)); 11 Assembly (off thread) ❑ AT&T syntax ❑ operation src, dest (e.g. movl $0xf5, %eax) ❑ 7(+1) registers (eax, edx, ecx, ebx, ebp, esi ,edi, esp) ❑ 2-address instructions ❑ GCC inlining asm volatile -

Operating Systems Memory Management

Operating Systems Memory Management [2] Memory Management What is expected by programmers from the system memory: • to be huge, • to be fast, • to be nonvolatile. Memory hierarchy: • small fast expensive memory (e.g. cache), • average in size, speed and expense memory (e.g. operating memory), • huge, slow and cheap memory (e.g. disk/tape memory). Memory Management (MM) type on the level of operating system is dictated by the computer system architecture. [3] Memory Management Organization Memory management depends on: • structure of address field of instruction arguments, • position of address field in instruction word, • hardware capabilities of address field transformation. Depending on the length of the address field the address space may be the same in size, smaller or bigger than the scope of operating memory addresses. [4] Operating System Functions Functions of the operating systems from the point of view of memory management: • address space management through address translation mechanisms, • memory contents protection, • shared areas access control, Memory Management • effective organization of operating memory management. The size of the operating memory for operating system code is usually fixed, but the allocation process for user processes is usually much more complicated. [5] Memory Allocation Methods Methods of memory allocation to user processes: 1. without division, all the memory allocated to one process. Multiprogram- ming may be implemented by swapping, 2. memory division, free operating memory divided into blocks allocated to particular user processes, 3. usage of virtual memory, there exist one or more virtual address spaces allocated to user processes and without any direct obvious mapping to the physical address space.