A Low-Cost Programmable Digital Sawtooth Wave Generator

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Lab 4: Using the Digital-To-Analog Converter

ECE2049 – Embedded Computing in Engineering Design Lab 4: Using the Digital-to-Analog Converter In this lab, you will gain experience with SPI by using the MSP430 and the MSP4921 DAC to create a simple function generator. Specifically, your function generator will be capable of generating different DC values as well as a square wave, a sawtooth wave, and a triangle wave. Pre-lab Assignment There is no pre-lab for this lab, yay! Instead, you will use some of the topics covered in recent lectures and HW 5. Lab Requirements To implement this lab, you are required to complete each of the following tasks. You do not need to complete the tasks in the order listed. Be sure to answer all questions fully where indicated. As always, if you have conceptual questions about the requirements or about specific C please feel free to as us—we are happy to help! Note: There is no report for this lab! Instead, take notes on the answers to the questions and save screenshots where indicated—have these ready when you ask for a signoff. When you are done, you will submit your code as well as your answers and screenshots online as usual. System Requirements 1. Start this lab by downloading the template on the course website and importing it into CCS—this lab has a slightly different template than previous labs to include the functionality for the DAC. Look over the example code to see how to use the DAC functions. 2. Your function generator will support at least four types of waveforms: DC (a constant voltage), a square wave, sawtooth wave, and a triangle wave, as described in the requirements below. -

Fourier Series

Chapter 10 Fourier Series 10.1 Periodic Functions and Orthogonality Relations The differential equation ′′ y + 2y = F cos !t models a mass-spring system with natural frequency with a pure cosine forcing function of frequency !. If 2 = !2 a particular solution is easily found by undetermined coefficients (or by∕ using Laplace transforms) to be F y = cos !t. p 2 !2 − If the forcing function is a linear combination of simple cosine functions, so that the differential equation is N ′′ 2 y + y = Fn cos !nt n=1 X 2 2 where = !n for any n, then, by linearity, a particular solution is obtained as a sum ∕ N F y (t)= n cos ! t. p 2 !2 n n=1 n X − This simple procedure can be extended to any function that can be repre- sented as a sum of cosine (and sine) functions, even if that summation is not a finite sum. It turns out that the functions that can be represented as sums in this form are very general, and include most of the periodic functions that are usually encountered in applications. 723 724 10 Fourier Series Periodic Functions A function f is said to be periodic with period p> 0 if f(t + p)= f(t) for all t in the domain of f. This means that the graph of f repeats in successive intervals of length p, as can be seen in the graph in Figure 10.1. y p 2p 3p 4p 5p Fig. 10.1 An example of a periodic function with period p. -

Tektronix Signal Generator

Signal Generator Fundamentals Signal Generator Fundamentals Table of Contents The Complete Measurement System · · · · · · · · · · · · · · · 5 Complex Waves · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 15 The Signal Generator · · · · · · · · · · · · · · · · · · · · · · · · · · · · 6 Signal Modulation · · · · · · · · · · · · · · · · · · · · · · · · · · · 15 Analog or Digital? · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 7 Analog Modulation · · · · · · · · · · · · · · · · · · · · · · · · · 15 Basic Signal Generator Applications· · · · · · · · · · · · · · · · 8 Digital Modulation · · · · · · · · · · · · · · · · · · · · · · · · · · 15 Verification · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 8 Frequency Sweep · · · · · · · · · · · · · · · · · · · · · · · · · · · 16 Testing Digital Modulator Transmitters and Receivers · · 8 Quadrature Modulation · · · · · · · · · · · · · · · · · · · · · 16 Characterization · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 8 Digital Patterns and Formats · · · · · · · · · · · · · · · · · · · 16 Testing D/A and A/D Converters · · · · · · · · · · · · · · · · · 8 Bit Streams · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · 17 Stress/Margin Testing · · · · · · · · · · · · · · · · · · · · · · · · · · · 9 Types of Signal Generators · · · · · · · · · · · · · · · · · · · · · · 17 Stressing Communication Receivers · · · · · · · · · · · · · · 9 Analog and Mixed Signal Generators · · · · · · · · · · · · · · 18 Signal Generation Techniques -

Oscilators Simplified

SIMPLIFIED WITH 61 PROJECTS DELTON T. HORN SIMPLIFIED WITH 61 PROJECTS DELTON T. HORN TAB BOOKS Inc. Blue Ridge Summit. PA 172 14 FIRST EDITION FIRST PRINTING Copyright O 1987 by TAB BOOKS Inc. Printed in the United States of America Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein. Library of Cangress Cataloging in Publication Data Horn, Delton T. Oscillators simplified, wtth 61 projects. Includes index. 1. Oscillators, Electric. 2, Electronic circuits. I. Title. TK7872.07H67 1987 621.381 5'33 87-13882 ISBN 0-8306-03751 ISBN 0-830628754 (pbk.) Questions regarding the content of this book should be addressed to: Reader Inquiry Branch Editorial Department TAB BOOKS Inc. P.O. Box 40 Blue Ridge Summit, PA 17214 Contents Introduction vii List of Projects viii 1 Oscillators and Signal Generators 1 What Is an Oscillator? - Waveforms - Signal Generators - Relaxatton Oscillators-Feedback Oscillators-Resonance- Applications--Test Equipment 2 Sine Wave Oscillators 32 LC Parallel Resonant Tanks-The Hartfey Oscillator-The Coipltts Oscillator-The Armstrong Oscillator-The TITO Oscillator-The Crystal Oscillator 3 Other Transistor-Based Signal Generators 62 Triangle Wave Generators-Rectangle Wave Generators- Sawtooth Wave Generators-Unusual Waveform Generators 4 UJTS 81 How a UJT Works-The Basic UJT Relaxation Oscillator-Typical Design Exampl&wtooth Wave Generators-Unusual Wave- form Generator 5 Op Amp Circuits -

Fourier Transforms

Fourier Transforms Mark Handley Fourier Series Any periodic function can be expressed as the sum of a series of sines and cosines (or varying amplitides) 1 Square Wave Frequencies: f Frequencies: f + 3f Frequencies: f + 3f + 5f Frequencies: f + 3f + 5f + … + 15f Sawtooth Wave Frequencies: f Frequencies: f + 2f Frequencies: f + 2f + 3f Frequencies: f + 2f + 3f + … + 8f 2 Fourier Series A function f(x) can be expressed as a series of sines and cosines: where: Fourier Transform Fourier Series can be generalized to complex numbers, and further generalized to derive the Fourier Transform. Forward Fourier Transform: Inverse Fourier Transform: Note: 3 Fourier Transform Fourier Transform maps a time series (eg audio samples) into the series of frequencies (their amplitudes and phases) that composed the time series. Inverse Fourier Transform maps the series of frequencies (their amplitudes and phases) back into the corresponding time series. The two functions are inverses of each other. Discrete Fourier Transform If we wish to find the frequency spectrum of a function that we have sampled, the continuous Fourier Transform is not so useful. We need a discrete version: Discrete Fourier Transform 4 Discrete Fourier Transform Forward DFT: The complex numbers f0 … fN are transformed into complex numbers F0 … Fn Inverse DFT: The complex numbers F0 … Fn are transformed into complex numbers f0 … fN DFT Example Interpreting a DFT can be slightly difficult, because the DFT of real data includes complex numbers. Basically: The magnitude of the complex number for a DFT component is the power at that frequency. The phase θ of the waveform can be determined from the relative values of the real and imaginary coefficents. -

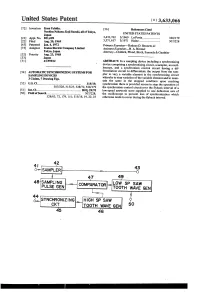

Tooth Wave Supplied to One Deflection Axis of 50 Field of Search

United States Patent (11) 3,633,066 72) Inventors Kozo Uchida; Naohisa Nakaya; Koji Suzuki, all of Tokyo, 56 References Cited Japan UNITED STATES PATENTS (21) Appl. No. 851,609 3,432,762 3/1969 La Porta....................... 328/179 22) Fied Aug. 20, 1969 3,571,617 3/1971 Hainz........................... 307/228 45) Patented Jan. 4, 1972 Primary Examiner-Rodney D. Bennett, Jr. 73 Assignee Iwatsu Electric Company Limited Assistant Examiner-H. A. Birmiel Tokyo, Japan Attorney-Chittick, Pfund, Birch, Samuels & Gauthier 32) Priority Aug. 23, 1968 33 Japan 31) 43/59922 ABSTRACT: In a sampling device including a synchronizing device comprising a synchronizing circuit, a sampler, an oscil loscope, and a synchronism control circuit having a dif 54) AUTOMATICSYNCHRONIZING SYSTEMSFOR ferentiation circuit to differentiate the output from the sam SAMPLNG EDEVICES pler to vary a variable element in the synchronizing circuit whereby to stop variation of the variable element and to main 3 Claims, 7 Drawing Figs. tain the same in the stopped condition upon reaching 52) U.S.C........................................................ 315/19, synchronism there is provided means to stop the operation of 307/228, 315125,328/72,328/179 the synchronism control circuit over the flyback interval of a (51) Int. Cl......................................................... H01j29/70 low-speed sawtooth wave supplied to one deflection axis of 50 Field of Search............................................ 307/228; the oscilloscope to prevent loss of synchronization which 328/63, 72, 179, 151; 315/18, 19, 22, 25 otherwise tends to occur during the flyback interval. LOW SP SAW 48SAMPLNGPULSE GEN COMPARATOR TOOTH WAVE GEN SYNCHRONIZING HGH SP SAW CKT TOOTH WAVE GEN 46 PATENTEDIAN 4972 3,633,066 SHEET 1 OF 2 - - - - - - - - - - was - - - - - - - - - - - - - -- a-- - - - F. -

Experiment 4: Time-Varying Circuits

Name/NetID: Teammate/NetID: Experiment 4: Time-Varying Circuits Laboratory Outline: Last week, we analyzed simple circuits with constant voltages using the DC power supply and digital multimeter (DMM). This week, we’ll learn to deal with voltages that vary over time by using the function generator and oscilloscope which can be found on your lab bench. Once this lab is complete, you’ll understand how and when to use all the bench equipment in the ECE 110 Lab. Unless an experiment requires a particularly-obscure capability from these devices, all future procedures will assume you understand how to take the necessary measurements using the necessary sources and meters. In addition, you will have expanded your knowledge on constructing prototype circuits and will be able to build most circuits required of future experiments. Using the Oscilloscope and Function Generator: In order to analyze voltages that vary with time, we must use a measurement device that can capture a time history of those voltages. This device is called an oscilloscope. In addition, there are many situations in which we might desire to generate a specific periodic voltage without having to build a special circuit to do so. We can do this using what is called a function generator (sometimes called a signal generator or waveform generator). Once we have mastered the use of these pieces of bench equipment, we’ll have all the basic skills needed for the rest of the semester. Notes: Function Generator Important! The function A function generator is a piece of equipment that outputs an electrical waveform that can vary in time, in contrast to the DC generator operates like an ideal power supply that can only output a constant voltage. -

Delta Modulation

DELTA MODULATION PREPARATION ...............................................................................122 principle of operation...............................................................122 block diagram.........................................................................................122 step size calculation................................................................................124 slope overload and granularity.................................................124 slope overload ........................................................................................124 granular noise.........................................................................................125 noise and distortion minimization ..........................................................126 EXPERIMENT .................................................................................126 setting up..................................................................................126 slope overload..........................................................................129 the ADAPTIVE CONTROL signal................................................................129 the output .................................................................................130 complex message.....................................................................131 TUTORIAL QUESTIONS................................................................132 APPENDIX.......................................................................................133 a ‘complex’ -

To Do Symbolic Processing with MATLAB You Have to Create The

EE 207 - Lab #9 Constructing Waveforms from Fourier Series using MATLAB (thanks to Dr. Nehrir for this lab) Objective: In this experiment we will use MATLAB to construct waveforms using Fourier series. Pre-lab: Document your pre-lab and lab work in your lab notebook. Find the Fourier series expression for the sawtooth waveform, shown below, and for a square wave, a full-wave rectified sine wave and a half-wave rectified one, all having the same peak and period as the sawtooth waveform (see Chapter 15 of your text.) Laboratory: Bring a USB stick with you to the computer lab to save your work, or plan to make use of a shared drive that you can access later. We can use MATLAB “sin ( )” function to construct the Fourier series of a waveform with as many terms as we care to include. Construct plots of the first harmonic, the sum of the first two, the first five, and the first ten harmonics of the sawtooth waveform. A listing of the M-file that computes the Fourier series for this sawtooth waveform is given on the next page, where Vm is set to 1. As noted from the listing, a radian frequency of 1, equivalent to a period T = 2S= 6.28 sec. is chosen. A time span of 0-10 seconds is specified so that slightly less than two periods of the waveform can be examined. You can divide the screen into different subplots, as shown below, and use these plotting windows to show the graphs of the developing waveforms when different number of harmonics of the waveform are used. -

Alias-Free Digital Synthesis of Classic Analog Waveforms

Alias-Free Digital Synthesis of Classic Analog Waveforms Tim [email protected] rd.edu Julius Smith [email protected] u CCRMA http://www-ccrma.stanford.edu/ Music Department, Stanford University Abstract Techniques are reviewed and presented for alias-free digital synthesis of classical analog synthesizer waveforms such as pulse train and sawtooth waves. Techniquesdescribed include summation of bandlim- ited primitive waveforms as well as table-lookup techniques. Bandlimited pulse and triangle waveforms are obtained by integrating the difference of two out-of-phase bandlimited impulse trains. Bandlimited impulse trains are generated as a superposition of windowed sinc functions. Methods for more general bandlimited waveform synthesis are also reviewed. Methods are evaluated from the perspectives of sound quality, computational economy, and ease of control. 1 Introduction impulse train Any analog signal with a discontinuity in the wave- 1 form (such as pulse train or sawtooth) or in the wave- 0.8 form slope (such as triangle wave) must be bandlim- 0.6 ited to less than half the sampling rate before sampling 0.4 to obtain a corresponding discrete-time signal. Simple methods of generating these waveforms digitally con- 0.2 tain aliasing due to having to round off the discontinuity 0 0 5 10 15 20 time to the nearest available sampling instant. The sig- nals primarily addressed here are the impulse train, rect- Box Train, and Sample Positions angular pulse, and sawtooth waveforms. Because the 1 latter two signals can be derived from the ®rst by inte- 0.8 gration, only the algorithm for the impulse train is de- 0.6 veloped in detail. -

Oscilloscope Fundamentals 03W-8605-4 Edu.Qxd 3/31/09 1:55 PM Page 2

03W-8605-4_edu.qxd 3/31/09 1:55 PM Page 1 Oscilloscope Fundamentals 03W-8605-4_edu.qxd 3/31/09 1:55 PM Page 2 Oscilloscope Fundamentals Table of Contents The Systems and Controls of an Oscilloscope .18 - 31 Vertical System and Controls . 19 Introduction . 4 Position and Volts per Division . 19 Signal Integrity . 5 - 6 Input Coupling . 19 Bandwidth Limit . 19 The Significance of Signal Integrity . 5 Bandwidth Enhancement . 20 Why is Signal Integrity a Problem? . 5 Horizontal System and Controls . 20 Viewing the Analog Orgins of Digital Signals . 6 Acquisition Controls . 20 The Oscilloscope . 7 - 11 Acquisition Modes . 20 Types of Acquisition Modes . 21 Understanding Waveforms & Waveform Measurements . .7 Starting and Stopping the Acquisition System . 21 Types of Waves . 8 Sampling . 22 Sine Waves . 9 Sampling Controls . 22 Square and Rectangular Waves . 9 Sampling Methods . 22 Sawtooth and Triangle Waves . 9 Real-time Sampling . 22 Step and Pulse Shapes . 9 Equivalent-time Sampling . 24 Periodic and Non-periodic Signals . 10 Position and Seconds per Division . 26 Synchronous and Asynchronous Signals . 10 Time Base Selections . 26 Complex Waves . 10 Zoom . 26 Eye Patterns . 10 XY Mode . 26 Constellation Diagrams . 11 Z Axis . 26 Waveform Measurements . .11 XYZ Mode . 26 Frequency and Period . .11 Trigger System and Controls . 27 Voltage . 11 Trigger Position . 28 Amplitude . 12 Trigger Level and Slope . 28 Phase . 12 Trigger Sources . 28 Waveform Measurements with Digital Oscilloscopes 12 Trigger Modes . 29 Trigger Coupling . 30 Types of Oscilloscopes . .13 - 17 Digital Oscilloscopes . 13 Trigger Holdoff . 30 Digital Storage Oscilloscopes . 14 Display System and Controls . 30 Digital Phosphor Oscilloscopes . -

Week 5 Signals Thru Systems

Crucial ideas • Any signal can be constructed as a sum of sine Signals & Systems for waves • In a linear time-invariant (LTI) system, the Speech & Hearing response to a sinusoid is the same whether it is on its own, or as one component of a complex signal – No interaction of components • An LTI system never introduces frequency Week V components not present in the input – a sinusoidal input gives a sinusoidal output of the same frequency • Hence, the output is the sum of the individual Signals through Systems sinusoidal responses to each individual sinusoidal component of the input 2 Six steps to determining system output to any ) particular input 1. Obtain the system’s amplitude response 2. Obtain the system’s phase response 3. Analyse the waveform to obtain its frequency response spectrum (amplitude and phase ) 4. Calculate the output amplitude of each LTI system system ( LTI component sinusoid in the input spectrum 5. Calculate the output phase of each sinusoid waveform → spectrum spectrum → waveform 6. Sum the output component sinusoids Fourier analysis Fourier synthesis 3 4 A particular example Step 1: Determinining a frequency response Input signal SYSTEM Output signal input signal system output signal transfer output amplitude function input amplitude or frequency response Response Amplitude Amplitude Frequency Frequency Frequency Step 1: Measure the system’s response Step 2: Sawtooth amplitude spectrum For example, by using sinewaves of different frequencies (as for the acoustic resonator) Here the response has a gain of 1 for