DVI on the Motherboard Using the TFP410

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

MON1000AP Series(Projected Capacitive Monitor)

Projected Capacitive Monitor Operations Manual MON1000AP Series Your Industrial Control Solutions Source _____________________ www.maplesystems.com For use with the following: • MON1000AP Series Projected Capacitive Touch Monitors Maple Systems, Inc. | 808 134th St. SW, Suite 120, Everett, WA 98204 | 425.745.3229 Projected Capacitive Touch Monitor Operations Manual: MON1000AP Series 2 TABLE OF CONTENTS TABLE OF CONTENTS ........................................................... 2 COPYRIGHT NOTICE ............................................................. 3 WARRANTY ......................................................................... 3 TECHNICAL SUPPORT .......................................................... 3 UNPACKING THE UNIT ......................................................... 3 SAFETY PRECAUTIONS ......................................................... 4 OVERVIEW OF MON1000AP SERIES ...................................... 5 PC CONNECTION ................................................................. 5 MOUNTING OPTIONS .......................................................... 6 SPECIFICATIONS .................................................................. 6 DIMENSIONAL OUTLINES .................................................... 8 I/O PORTS ......................................................................... 12 ON-SCREEN DISPLAY (OSD) OPERATION ............................ 14 ON-SCREEN DISPLAY PARAMETER ADJUSTMENT ............... 15 Projected Capacitive Touch Monitor Operations Manual: MON1000AP Series -

CHE-HDBT2020 Pro AV/IT 4K 18G Hdbaset™ Extender TX/RX Kit up to 330Ft

CHE-HDBT2020 Pro AV/IT 4K 18G HDBaseT™ Extender TX/RX Kit up to 330ft Operation Manual DISCLAIMERS The information in this manual has been carefully checked and is believed to be accurate. Comprehensive Connectivity assumes no responsibility for any infringements of patents or other rights of third parties which may result from its use. Comprehensive Connectivity assumes no responsibility for any inaccuracies that may be contained in this document. Comprehensive also makes no commitment to update or to keep current the information contained in this document. Comprehensive reserves the right to make improvements to this document and/or product at any time and without notice. COPYRIGHT NOTICE No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or any of its part translated into any language or computer file, in any form or by any means— electronic, mechanical, magnetic, optical, chemical, manual, or otherwise—without express written permission and consent from Comprehensive Connectivity. © Copyright 2018 by Comprehensive All Rights Reserved. TRADEMARK ACKNOWLEDGMENTS All products or service names mentioned in this document may be trademarks of the companies with which they are associated. SAFETY PRECAUTIONS Please read all instructions before attempting to unpack, install or operate this equipment and before connecting the power supply. Please keep the following in mind as you unpack and install this equipment: • Always follow basic safety precautions to reduce the risk of fire, electrical shock and injury to persons. • To prevent fire or shock hazard, do not expose the unit to rain, moisture or install this product near water. • Never spill liquid of any kind on or into this product. -

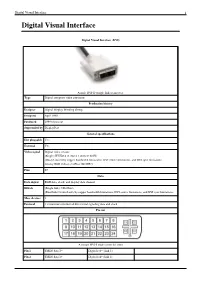

Digital Visual Interface (DVI)

Digital Visual Interface 1 Digital Visual Interface Digital Visual Interface (DVI) A male DVI-D (single link) connector. Type Digital computer video connector Production history Designer Digital Display Working Group Designed April 1999 Produced 1999 to present Superseded by DisplayPort General specifications Hot pluggable Yes External Yes Video signal Digital video stream: (Single) WUXGA (1,920 × 1,200) @ 60 Hz (Dual) Limited by copper bandwidth limitations, DVI source limitations, and DVI sync limitations. Analog RGB video (−3 dB at 400 MHz) Pins 29 Data Data signal RGB data, clock, and display data channel Bitrate (Single link) 3.96 Gbit/s (Dual link) Limited only by copper bandwidth limitations, DVI source limitations, and DVI sync limitations. Max. devices 1 Protocol 3 × transition minimized differential signaling data and clock Pin out A female DVI-I socket from the front Pin 1 TMDS data 2− Digital red− (link 1) Pin 2 TMDS data 2+ Digital red+ (link 1) Digital Visual Interface 2 Pin 3 TMDS data 2/4 shield Pin 4 TMDS data 4− Digital green− (link 2) Pin 5 TMDS data 4+ Digital green+ (link 2) Pin 6 DDC clock Pin 7 DDC data Pin 8 Analog vertical sync Pin 9 TMDS data 1− Digital green− (link 1) Pin 10 TMDS data 1+ Digital green+ (link 1) Pin 11 TMDS data 1/3 shield Pin 12 TMDS data 3- Digital blue− (link 2) Pin 13 TMDS data 3+ Digital blue+ (link 2) Pin 14 +5 V Power for monitor when in standby Pin 15 Ground Return for pin 14 and analog sync Pin 16 Hot plug detect Pin 17 TMDS data 0− Digital blue− (link 1) and digital sync Pin 18 TMDS data 0+ Digital blue+ (link 1) and digital sync Pin 19 TMDS data 0/5 shield Pin 20 TMDS data 5− Digital red− (link 2) Pin 21 TMDS data 5+ Digital red+ (link 2) Pin 22 TMDS clock shield Pin 23 TMDS clock+ Digital clock+ (links 1 and 2) Pin 24 TMDS clock− Digital clock− (links 1 and 2) C1 Analog red C2 Analog green C3 Analog blue C4 Analog horizontal sync C5 Analog ground Return for R, G, and B signals Digital Visual Interface (DVI) is a video display interface developed by the Digital Display Working Group (DDWG). -

5221 Manual 090519.Pdf

User's Manual Remote Control Unit Power On/Off It's possible to use a remote controller within 3~5m, 60 degree of angle scope. You can use an extension receiver for a remote controller if it's far away from the system. The receiver in the system will not work when the extension reciever is connected. Insert battery 1. Pull out the insert part. 2. Insert battery after checking.. 3. Push in the Insert part. "+" Polarity HDS-1151L Connection(CAT5e/6 Mode) How to connect devices with splitter (►Input: Blu-ray Player, HD Stream Generator ►Output: PDP, LCD TV) I $.Note CATC cable is recommended for best results. Use both TMDS & DDC cable to use EDID/HDCP Please ask us if you want to use CAT5e/6 cable only not to use ECMD/HDCP Should re-set the settings of Transmitter & Receiver following the length of CAT5e/8 or resolut" on. For setting, please referto "How to set up CATSe/ff1 10 User's Manual How to set up CAT5e/6 mode Transmitter setting 1. Press & Select "Input 1" en the front 2. Press "Input 1" button 5 times. Please check if "beep" also sounds 5 times. 3. After pressing "Input 1" 5 times, you can hear 3 times buzzer sound. Entered "Boost setting mode" 4. How to set "Boost"? • Press Input 1 or Input 2 buttons Inputi: Make it lower & Input 2: Make it higher. • The setting value covers from 0 to 12 If you can hear 2 times buzzer sounds during pressing Input 1, it means that the setting value is arrived at the lowest level "0". -

Sii9293 MHL/HDMI Receiver Data Sheet Silicon Image, Inc

Data Sheet SiI9293 MHL/HDMI Receiver Data Sheet Document # SiI-DS-1107-A SiI9293 MHL/HDMI Receiver Data Sheet Silicon Image, Inc. March 2013 Copyright Notice Copyright © 2012-2013 Silicon Image, Inc. All rights reserved. The contents of these materials contain proprietary and confidential information (including trade secrets, copyright, and other Intellectual Property interests) of Silicon Image, Inc. or its affiliates. All rights are reserved and contents, (in whole or in part) may not be reproduced, downloaded, disseminated, published, or transferred in any form or by any means, except with the prior written permission of Silicon Image, Inc. or its affiliates. You may not use these materials except only for your bona fide non-commercial evaluation of your potential purchase of products and/or services from Silicon Image or its affiliates; and only in connection with your purchase of products or services from Silicon Image or its affiliates, and only in accordance with the terms and conditions stipulated. Copyright infringement is a violation of federal law subject to criminal and civil penalties. You have no right to copy, modify, transfer, sublicense, publicly display, create derivative works of, distribute these materials, or otherwise make these materials available, in whole or in part, to any third party. Patents The subject matter described herein may contain one or more inventions claimed in patents or patents pending owned by Silicon Image, Inc. or its affiliates. Trademark Acknowledgment Silicon Image®, the Silicon Image logo, Instaport®, the Instaport logo, InstaPrevue®, Simplay®, Simplay HD®, and UltraGig™ are trademarks or registered trademarks of Silicon Image, Inc. in the United States or other countries. -

17.3” HD & SD SDI Digital, Analog, HD HDMI/DVI (+HDCP

LVB17 17.3” HD & SD SDI Digital, Analog, HD HDMI/DVI (+HDCP) •High & Standard Definition Video LCD Monitors 1080/720/576/480(@60/59.94/50) •3G includes 2x3G HD/SD SDI-Digital input/ HD HDMI/DVI (+HDCP) •HDMI/DVI inputs accepts up to 1080p HD •Modes: EGA to UXGA, NTSC/PAL/SECAM/NTSC4.43/PAL-M •Analog Inputs are Composite, Y/C, Component, RGB (SOG), DVI – I (Analog PC) •Aspect Ratio: 16:9, 4:3, 14:9, 13:9, 1.85:1, 2.35:1: •Marker Display. •UMD Support. •Color Temperature – User, VAR, 11000K, 9300K, 6500K, 5400K, 3200K SPECIFICATIONS Active Area (Diagonal): 17.3”/ 439 mm MODES High & Standard Definition Video Modes: 1920x1080p(50/60/30psf/25psf/24psf/30/25/24),1920x1080i(50/60), 1280x720p(50/59.94/60), 480i(59.94),576i(50) Digital, VESA VGA, DVI/HDMI *24psf/23.98psf signal format is not supported in “UNDERSCAN ” Mode. PC Video Modes: EGA, VGA, SVGA, XGA, WXGA, SXGA, WSXGA, UXGA Standard Definition Video Modes: NTSC/PAL/SECAM/NTSC4.43/PAL-M Scanning Modes: Under/Over/Zero/Pixel to Pixel Scanning INPUTS Digital Video Inputs: 3G HD SDI (@50/59.94/60), HD HDMI/DVI (+HDCP) Digital Video Inputs: Digital Visual Interface, VESA & SMPTE Rates. Analog Video Inputs: Composite, Y/C, Component, RGB (SOG), DVI – I (Analog PC) PICTURE Aspect Ratios: Full Screen, 16:9, 4:3, 14:9, 13:9, 1.85:1, 2.35:1 Picture-in-Picture : Analog (Composite1, 2, 3, YPbPr, GBR, PC), SDI 1 inputs + SDI 2, Digital (DVI, HDMI) input PIP Picture-by-Picture: Side by Side split screen display Pixel (RGB Trio) Arrangement: 1920 H x 1080 V Pixels RGB strip arrangement (2,073,600 Pixels, -

Overview of Digital and Analog Connections Digital Video

Overview of Digital and Analog Connections Digital Video connectors are used to deliver the highest quality video signal. The technology uses TMDS (Transition Minimized Differential Signaling) to transmit large amounts of digital data from the source to the display, resulting in a high-quality image. DVI (Digital Visual Interface) was developed by the industry governing organization DDWG (Data Display Working Group) to send digital information from a computer to a digital display, such as a flat-panel LCD monitor. HDMI took a step forward by integrating audio and video into a more compact interface. DisplayPort is an interface technology that is designed to connect high-graphics capable PCs and displays as well as home theater equipment and displays. DisplayPort is similar to HDMI in that the DisplayPort signal carries both digital audio and video. HDMI HDMI stands for High Definition Multimedia Interface. This technology carries the same video information as DVI but adds the capacity for digital audio and control signals as well. The current version of HDMI carries one TMDS link of digital video. Found on many home-theater/consumer electronics devices, HDMI uses a 19-pin connector that is held in place by friction. This connector is technically described as a Type A HDMI connector. See our Available HDMI Cables HDMI Mini The Type C connector HDMI, the HDMI mini connector has the same number of pins but with its compact size, it is used for portable devices. See our Available HDMI Mini Cables DisplayPort™ DisplayPort™ is an interface technology that is designed to connect high-end graphics capable PCs and displays as well as home theater equipment and displays. -

VGA to DVI Adapter.Indd

VGA to DVI Adapter II USER MANUAL www.gefen.com ASKING FOR ASSISTANCE Technical Support: Telephone (818)772-9100 (800) 545-6900 Fax (818)772-9120 Technical Support Hours: 8:00 AM to 5:00 PM Monday thru Friday PST Write To: Gefen Inc. c/o Customer Service 20600 Nordhoff Street Chatsworth CA 91311 [email protected] -- www.gefen.com Notice Gefen Inc. reserves the right to make changes in the hard ware, packaging and any accompanying doc u men ta tion without prior written notice. VGA to DVI Adapter is a trademark of Gefen Inc. © 2006 Gefen Inc., All Rights Reserved TABLE OF CONTENTS 1 Introduction 2 Features 3 Panel Descriptions 4 Connecting and Operating the VGA to DVI Adapter 5 Specifi cations 6 Warranty INTRODUCTION Congratulations on your purchase of the VGA to DVI Adapter II. Your complete satisfaction is very important to us. Gefen’s line of KVM (Keyboard Video & Mouse), DVI, ADC, USB, switches, extenders, converters and hubs is designed to make com- puter use more comfortable, more productive and less expensive. KVM switches allow access to multiple computers from a single keyboard, while the ex- tenders give the user control over a computer up to 330 feet away from the work area. Gefen offers solutions for noise, space and security concerns, data center control, in- formation distribution, conference room presentation, and school and corporate training environments. Our Committment Gefen will always offer the fi nest quality product at the best possible price. Included in that price is a lifetime of free support from a team of outstanding engineers. -

Choosing a Monitor with Video and Audio Ports to Match Your Needs Business White Paper | Connectivity Sorting out Your Ports

Business white paper Connect to a better view Choosing a monitor with video and audio ports to match your needs Business white paper | Connectivity Sorting out your ports Many newer PCs, tablets, smartphones, and video players are designed to deliver outstanding picture quality when they’re hooked up to a high-definition (HD) display. You can make your computer games, photos, movies, and business presentations look and perform their best—regardless of where they’re stored—by showing them on the big screen. Understanding how the various connection ports on your devices work, and which connection is built to deliver the experience you want, will help you choose the optimal match in a display. HP provides a broad selection of PC monitors with multiple connectivity options to help you get more value and enjoyment from your digital devices. To help simplify your choice of monitor, here is an overview of the most popular connectivity options available today, as well as some emerging standards. The shift away from analog VGA One of the oldest and most familiar video connection ports is Video Graphics Array (VGA), which supplies an analog—rather than digital—signal from device to monitor. VGA connectors are inexpensive to manufacture and provide decent picture quality for basic computing and image viewing. Some PCs, desktop monitors, and projectors still come with a VGA port. However, the rise of digital content—in cameras, HDTVs, DVD and Blu-ray players, and many other products—is quickly making analog inputs obsolete. In order to display digital content on-screen through a VGA connection, the signal has to be converted to analog and then back to digital, which can reduce picture quality. -

An Overview of Consumer Electronics Connectivity Brought to You by Quiktron, Inc

An Overview of Consumer Electronics Connectivity Brought to you by Quiktron, Inc. “For a list of all the ways technology has failed to improve the quality of life, please press three.” -- Alice Kahn This quote is certainly applicable to consumer electronics. From the very first commercially produced radios to the latest in high-definition television technology, the manner in which the components used to deliver our news, music, movies and entertainment are interconnected seems to have escaped logic. For both the newcomer and the old hand alike, connecting equipment in the most efficient and effective manner can be a painful chore. It is hoped this article will improve your background knowledge concerning potential A/V system connection schemes and where each is most appropriate. The next time you find yourself in a “connectivity quandary” perhaps the ideas shared here will help you to quickly solve the riddle of which wire goes where and why! HDMI™ HDMI (High Definition Multimedia Interface) is a trademark of HDMI Licensing LLC. Developed by Sony, Hitachi, Thomson (RCA), Philips, Matsushita (Panasonic), Toshiba and Silicon Image, HDMI was created as a digital interface standard for the consumer electronics market. The HDMI protocol combines high-definition video, multi-channel audio, and inter-component control in a single digital interface. This lone interconnect has the ability to transmit uncompressed digital video and up to eight channels of audio from source to display. Even more, the HDMI connection enables audio/video components to share data and commands, thus unifying an oft-disjointed collection of “boxes” into a real, working system. -

Lab 9: Video Interfaces: HDMI And

Lab 9: Video Interfaces: HDMI and DVI EE-459/500 HDL Based Digital Design with Programmable Logic Electrical Engineering Department, University at Buffalo Last update: Cristinel Ababei, October 27 2012 1. Objective The objective of this lab is to learn how to transmit High-Definition Multimedia Interface (HDMI) and Digital Visual Interface (DVI) data streams to HDMI and DVI capable monitors. The top-level design in this lab displays a simple colored pattern. In addition, we will learn how to create ISE WebPack projects that use both VHDL and Verilog source files. 2. Introduction The Atlys board contains four HDMI ports (see Fig.1), including two buffered – via the TI’s TMDS141 buffers – HDMI input/output ports (type A connector), one buffered HDMI output port (type D connector), and one unbuffered port that can be input or output [1]. Figure 1 Illustration of the four HDMI ports of the Atlys board (left). HDMI Male to DVI-D Female Rotating Adapter (top right). HDMI connectors (bottom right) Since the HDMI and DVI systems use the same transition-minimized differential signaling TMDS signaling standard, a simple adaptor shown in the right hand side of Fig.1 (available at most electronics stores such as TigerDirect [2]) can be used to drive a DVI connector from either of the HDMI output ports. The HDMI connector does not include VGA signals, so analog VGA displays cannot be driven. The Atlys board does not have any VGA connector. For examples on how to drive VGA monitors from the Atlys board, please see the supplemental material of this lab on the course’s website. -

Digital Visual Interface Revision 1

Digital Visual Interface Revision 1. 0 Digital Display Working Group Digital Visual Interface DVI Revision 1.0 02 April 1999 Page 1 of 76 HTC EXHIBIT 1013 Digital Visual Interface Revision 1. 0 Digital Display Working Group The Digital Display Working Group Promoters (''DDWG Promoters") are Intel Corporation, Silicon Jmage, lnc., Compaq Computer Corporation, Fujitsu Limited, Hewlett-Packard Company, lntemational Business Macbines Corporation, and NEC Corporation TffiS SPECIFICATION IS PROVIDED "AS lS" WJTH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTAB[LITY, NONlNFRlNGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECWICATION OR SAMPLE. The DDWG Promoters disclaim all liability, including liability for infringement ofany proprietary rights, relating to usc of information in this sprxilil:ation. No license. express or implied, by estoppel or othetwise, to any intellectual property rights is granted herein. The DDWG Promoters may have patents and/or patent applications related to the Digital Visua//nteJfaoe Specification. The DDWG Promoters intend to make avai lable to the industry <Ul Adopter's Agreement that will include a limited. reciprocal, royalty-free license to tl1e electrical interfaces. mechanical interfaces. signals, si ~:,'llaling and coding protocols, and bus protocols described in, and required by, the Digita/11isual Tnte1jace Specfftcation Revision }.() finalized and published by the DDWG Promoters. To encourage early adoption. Adopters will be required to retum their executed copy of the Adopter's Agreement during an "Adoption Period" which is within one year after the DVl Specification Revision 1.0 is first published or within one year after the Adopter first sells products that comply with that specification, whichever is later.