Pegatron and Cadence

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ASUSTEK COMPUTER INC. NON-CONSOLIDATED FINANCIAL STATEMENTS December 31, 2007 and 2006 with Report of Independent Auditors

ASUSTEK COMPUTER INC. NON-CONSOLIDATED FINANCIAL STATEMENTS December 31, 2007 and 2006 With Report of Independent Auditors The reader is advised that these financial statements have been prepared originally in Chinese. In the event of a conflict between these financial statements and the original Chinese version or difference in interpretation between the two versions, the Chinese language financial statements shall prevail. English Translations of Financial Statements Originally Issued in Chinese ASUSTEK COMPUTER INC. NON-CONSOLIDATED BALANCE SHEETS DECEMBER 31, 2007 AND 2006 (Expressed in New Taiwan Thousand Dollars) ASSETS Notes 2007 2006 LIABILITIES AND STOCKHOLDERS' EQUITY Notes 2007 2006 CURRENT ASSETS CURRENT LIABILITIES Cash and cash equivalents II, IV.1 $9,174,219 $10,791,836 Notes and accounts payable $80,372,075 $109,230,069 Financial assets at fair value through profit or loss-current II, IV.2 7 ,257,169 4,218,719 Notes and accounts payable -affiliated companies V 837,669 9,007,117 Notes and accounts receivable-Net II, IV.3 61 ,863,244 80,950,232 Income tax payable II, IV.19 5,795,472 3,558,780 Accounts receivable-affiliated companies-Net II, IV.3, V 45 ,747,118 21,152,900 Accrued expenses II, IV.12, V 31,771,898 21,553,421 Other receivables-Net II,V 5 ,069,634 1,627,107 Other payables V 771,563 469,653 Inventories-Net II, IV.4 53 ,643,865 72,627,961 Receipts in advance V 2,412,198 2,502,732 Prepayments V 121 ,788 162,382 Bonds payable-current portion IV.11 - 6,613,377 Other current assets 101 ,863 - Other current liabilities -

Inventec Corporation

(English Translation of Pro Forma Financial Report Originally Issued in Chinese) PEGATRON CORPORATION AND ITS SUBSIDIARIES PRO FORMA CONSOLIDATED FINANCIAL STATEMENTS DECEMBER 31, 2008 AND 2007 (With Independent Auditors’ Report Thereon) Address: 5F., No.76, Ligong St., Beitou District, Taipei City 112, Taiwan Telephone: 886-2-8143-9001 - 1 - TABLE OF CONTENTS Contents Page Cover Page 1 Table of Contents 2 Independent Auditors’ Report 3 Pro Forma Consolidated Balance Sheets 4 Pro Forma Consolidated Statements of Income 5 Pro Forma Consolidated Statements of Changes in Stockholders’ Equity 6 Pro Forma Consolidated Statements of Cash Flows 7 Notes to Pro Forma Consolidated Financial Statements (1) Organization and Business 8 (2) Summary of Significant Accounting Policies 8-28 (3) Reasons for and Effects of Accounting Changes 28 (4) Summary of Major Accounts 28-49 (5) Related-Party Transactions 50-56 (6) Pledged Assets 56 (7) Significant Commitments and Contingencies 57-58 (8) Significant Catastrophic Losses 59 (9) Significant Subsequent Events 59 (10) Others 59 (11)Additional Disclosures 60-61 (12)Segment Information 61-62 - 2 - (English Translation of Financial Report Originally Issued in Chinese) PEGATRON CORPORATION AND ITS SUBSIDIARIES PRO FORMA CONSOLIDATED BALANCE SHEETS DECEMBER 31, 2008 AND 2007 (All Amounts Expressed in Thousands of New Taiwan Dollars, Except for Share Data) December 31, 2008 December 31, 2007 Amount % Amount % ASSETS Current Asset: Cash (Notes 2 and 4(1)) $ 27,065,987 12 26,294,882 9 Financial assets reported -

Taiwan's Top 50 Corporates

Title Page 1 TAIWAN RATINGS CORP. | TAIWAN'S TOP 50 CORPORATES We provide: A variety of Chinese and English rating credit Our address: https://rrs.taiwanratings.com.tw rating information. Real-time credit rating news. Credit rating results and credit reports on rated corporations and financial institutions. Commentaries and house views on various industrial sectors. Rating definitions and criteria. Rating performance and default information. S&P commentaries on the Greater China region. Multi-media broadcast services. Topics and content from Investor outreach meetings. RRS contains comprehensive research and analysis on both local and international corporations as well as the markets in which they operate. The site has significant reference value for market practitioners and academic institutions who wish to have an insight on the default probability of Taiwanese corporations. (as of June 30, 2015) Chinese English Rating News 3,440 3,406 Rating Reports 2,006 2,145 TRC Local Analysis 462 458 S&P Greater China Region Analysis 76 77 Contact Us Iris Chu; (886) 2 8722-5870; [email protected] TAIWAN RATINGS CORP. | TAIWAN'S TOP 50 CORPORATESJenny Wu (886) 2 872-5873; [email protected] We warmly welcome you to our latest study of Taiwan's top 50 corporates, covering the island's largest corporations by revenue in 2014. Our survey of Taiwan's top corporates includes an assessment of the 14 industry sectors in which these companies operate, to inform our views on which sectors are most vulnerable to the current global (especially for China) economic environment, as well as the rising strength of China's domestic supply chain. -

Summary of Investments by Type

COMMON INVESTMENT FUNDS Schedule of Investments March 31, 2017 SUMMARY OF INVESTMENTS BY TYPE Cost Market Value Fixed Income Investments $ $ Short-term investments 42,653,484 42,653,484 Bonds 175,482,352 175,327,122 Mortgage-backed securities 22,199,796 21,785,061 Emerging markets debt 9,619,817 10,899,147 Bank loans - high income fund 20,985,176 23,595,337 Total Fixed Income Investments 270,940,624 274,260,151 Equity-Type Investments Mutual funds Domestic 9,234,353 12,420,750 International 18,849,681 18,688,379 Common stocks Domestic 152,833,551 187,487,257 International 216,167,277 227,850,648 Total Equity-Type Investments 397,084,862 446,447,034 Alternative Investments Funds of hedge funds 38,264,990 46,247,453 Real estate trust fund 6,876,041 10,104,141 Total Alternatives Investments 45,141,031 56,351,594 TOTAL INVESTMENTS 713,166,517 777,058,779 Page 1 of 32 COMMON INVESTMENT FUNDS Schedule of Investments March 31, 2017 SUMMARY OF INVESTMENTS BY FUND Cost Market Value Fixed Income Fund $ $ Short-term investments 13,092,627 13,092,627 Bonds 143,036,345 143,362,214 Mortgage-backed securities 21,372,523 20,977,317 Emerging markets debt 9,619,817 10,899,147 Bank loans - high income fund 20,985,176 23,595,337 208,106,487 211,926,642 Domestic Core Equity Fund Short-term investments 9,127,791 9,127,791 Common stocks 134,983,626 165,021,220 Futures - (5,950) Private placement 4,150 4,150 144,115,567 174,147,211 Small Cap Equity Fund Short-term investments 2,937,066 2,937,066 Mutual funds 9,234,353 12,420,750 Common stocks 17,845,775 22,467,836 -

Chapter 2 Hon Hai/Foxconn: Which Way Forward ?

Chapter 2 Hon Hai/Foxconn: which way forward ? Gijsbert van Liemt 1 1. Introduction Hon Hai/Foxconn, the world's leading contract manufacturer, assembles consumer electronics products for well-known brand-names. It is also a supplier of parts and components and has strategic alliances with many other such suppliers. Despite its size (over a million employees; ranked 32 in the Fortune Global 500) and client base (Apple, HP, Sony, Nokia), remarkably little information is publicly available on the company. The company does not seek the limelight, a trait that it shares with many others operating in this industry. Quoted on the Taiwan stock exchange, Hon Hai Precision Industry (HHPI) functions as an ‘anchor company’ for a conglomerate of companies. 2 As the case may be, HHPI is the sole, the majority or a minority shareholder in these companies and has full, partial or no control at all. Many subsidiaries use the trade name Foxconn and that is why this chapter refers to the company as Hon Hai/Foxconn. Among its many subsidiaries and affiliates are Ambit Microsystems, Cybermart, FIH Mobile, Fu Taihua Industrial, Hong Fujin Precision and Premier Image. After a near hundredfold increase in sales in the first decade of this century Hon Hai/Foxconn's sales growth slowed down drastically. The company is facing several challenges: slowing demand growth in its core (electronics) business; a weakening link with Apple, its main customer; rising labour costs and a more assertive labour force in China, its main production location; and pressure from its shareholders. 1. Copyright 2015 Gijsbert van Liemt. -

Pegatron Corporation and Subsidiaries

1 Stock Code:4938 (English Translation of Consolidated Financial Statements and Report Originally Issued in Chinese) PEGATRON CORPORATION AND SUBSIDIARIES Consolidated Financial Statements With Independent Accountants’ Review Report For the Three Months Ended March 31, 2018 and 2017 Address: 5F., No.76, Ligong St., Beitou District, Taipei City 112, Taiwan Telephone: 886-2-8143-9001 The auditors’ review report and the accompanying consolidated financial statements are the partial English translation of the Chinese version prepared and used in the Republic of China. If there is any conflict between, or any difference in the interpretation of the English and Chinese language auditors’ review report and consolidated financial statements, the Chinese version shall prevail. 2 Table of contents Contents Page 1. Cover Page 1 2. Table of Contents 2 3. Independent Accountants’ Review Report 3 4. Consolidated Balance Sheets 4 5. Consolidated Statements of Comprehensive Income 5 6. Consolidated Statements of Changes in Equity 6 7. Consolidated Statements of Cash Flows 7 8. Notes to the Consolidated Financial Statements (1) Company history 8 (2) Approval date and procedures of the consolidated financial statements 8 (3) Application of new standards, amendments and interpretations 8~15 (4) Summary of significant accounting policies 16~50 (5) Significant accounting assumptions and judgments, and major sources 50 of estimation uncertainty (6) Explanation of significant accounts 51~90 (7) Related-party transactions 90~91 (8) Pledged assets 91 (9) Significant -

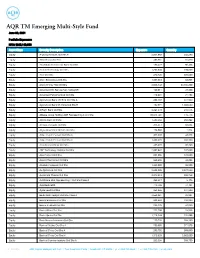

AQR TM Emerging Multi-Style Fund June 30, 2021

AQR TM Emerging Multi-Style Fund June 30, 2021 Portfolio Exposures NAV: $685,149,993 Asset Class Security Description Exposure Quantity Equity A-Living Services Ord Shs H 2,001,965 402,250 Equity Absa Group Ord Shs 492,551 51,820 Equity Abu Dhabi Commercial Bank Ord Shs 180,427 96,468 Equity Accton Technology Ord Shs 1,292,939 109,000 Equity Acer Ord Shs 320,736 305,000 Equity Adani Enterprises Ord Shs 1,397,318 68,895 Equity Adaro Energy Tbk Ord Shs 2,003,142 24,104,200 Equity Advanced Info Service Non-Voting DR 199,011 37,300 Equity Advanced Petrochemical Ord Shs 419,931 21,783 Equity Agricultural Bank of China Ord Shs A 288,187 614,500 Equity Agricultural Bank Of China Ord Shs H 482,574 1,388,000 Equity Al Rajhi Bank Ord Shs 6,291,578 212,576 Equity Alibaba Group Holding ADR Representing 8 Ord Shs 33,044,794 145,713 Equity Alinma Bank Ord Shs 1,480,452 263,892 Equity Ambuja Cements Ord Shs 305,517 66,664 Equity Anglo American Platinum Ord Shs 174,890 1,514 Equity Anhui Conch Cement Ord Shs A 307,028 48,323 Equity Anhui Conch Cement Ord Shs H 1,382,025 260,500 Equity Arab National Bank Ord Shs 485,970 80,290 Equity ASE Technology Holding Ord Shs 2,982,647 742,000 Equity Asia Cement Ord Shs 231,096 127,000 Equity Aspen Pharmacare Ord Shs 565,696 49,833 Equity Asustek Computer Ord Shs 1,320,000 99,000 Equity Au Optronics Ord Shs 2,623,295 3,227,000 Equity Aurobindo Pharma Ord Shs 3,970,513 305,769 Equity Autohome ADS Representing 4 Ord Shs Class A 395,017 6,176 Equity Axis Bank GDR 710,789 14,131 Equity Ayala Land Ord Shs 254,266 344,300 -

2020 Annual Report

AUGUST 31, 2020 2020 Annual Report iShares, Inc. • iShares MSCI Hong Kong ETF | EWH | NYSE Arca • iShares MSCI Japan Small-Cap ETF | SCJ | NYSE Arca • iShares MSCI Malaysia ETF | EWM | NYSE Arca • iShares MSCI Pacific ex Japan ETF | EPP | NYSE Arca • iShares MSCI Singapore ETF | EWS | NYSE Arca • iShares MSCI Taiwan ETF | EWT | NYSE Arca • iShares MSCI Thailand ETF | THD | NYSE Arca Beginning on January 1, 2021, as permitted by regulations adopted by the Securities and Exchange Commission, paper copies of each Fund’s shareholder reports will no longer be sent by mail, unless you specifically request paper copies of the reports from your financial intermediary, such as a broker-dealer or bank. Instead, the reports will be made available on a website, and you will be notified by mail each time a report is posted and provided with a website link to access the report. You may elect to receive all future reports in paper free of charge. Ifyou hold accounts throughafinancial intermediary, you can follow the instructions included with this disclosure, if applicable, or contact your financial intermediary to request that you continue to receive paper copies ofyour shareholder reports. Please note that not all financial intermediaries may offer this service. Your election to receive reports in paper will apply to all funds held with your financial intermediary. If you already elected to receive shareholder reports electronically, you will not be affected by this change and you need not take any action. You may elect to receive electronic delivery of shareholder reports and other communications by contactingyour financial intermediary. -

Taiwan's Turning Tide

BUSINESS SWEDEN TAIWAN’S TURNING TIDE EXPLORING THE NEXT HORIZON FOR ASIA’S HIDDEN MANUFACTURING POWERHOUSE TAIWAN’S TURNINGFORTSÄTT TIDE SURFA EXPLORING THE NEXT HORIZON FOR ASIA’S PÅHIDDEN TILLVÄXTVÅGEN MANUFACTURING POWERHOUSE MARKNADSINSIKT APRIL 2017 Layout/grafik:Layout/Graphics Business Sweden Communications Foto:Business Sid Sweden 1, www.istockphoto.com. Marcom & Digitalisation Sid 3, Anders Thessing, www.thessing.se Tryck:Photos Åtta45, 2017 Page 1, 5, 8, iStock by Getty Images 2 | BUSINESS SWEDEN | TAIWAN’S TURNING TIDE EXECUTIVE SUMMARY Taiwan’s manufacturing competence and footprint is often underesti- mated. This island off the coast of China is where some of the world’s most high-tech goods are produced, and it is home to global OEMs and ODMs headquartered here. Taiwan is also a very important investor in both China and Southeast Asia. Given new realities on the ground in the APAC region – from trade barriers to shifting labour costs, digitalisation and increased demands on sustainability – Swedish suppliers have a new role to play in helping Tai- wanese manufacturers manage change. Sweden has more global manufacturing companies per capita than any other country in the world. These Swedish companies, and the sub-sup- VLAD MÅNSSON pliers that enabled them to thrive, are experts at providing innovative and Market Manager, Taiwan high-tech equipment, solutions and services where productivity and sus- tainability go hand in hand. The purpose of this report is to reflect on the impact of recent trade war developments on the APAC supply chain in relation to Taiwan’s man- ufacturing base in Asia. In addition, Business Sweden provides strategic recommendations for how Swedish companies can match their offering to the fast-changing needs of Taiwanese manufacturers. -

German-Taiwanese Automotive Matchmaking 汽車產業媒合

German-Taiwanese Automotive Matchmaking 汽車產業媒合 German Trade Office Taipei & ARTC Introduction Following the 1st German-Taiwanese Automotive Forum in 2020, the German Trade Office Taipei (GTO) and the Automotive Research and Testing Center (ARTC) are organizing a matchmaking between German and Taiwanese automotive manufacturers and suppliers along the complete value chain. The matchmaking aims to promote the collaboration between Taiwanese and German companies in the automotive industry. Due to the current COVID-19 related travel restrictions, the matchmaking between the German and Taiwanese participants will be conducted online. The details of the matchmaking are as following: • Timeframe: May 24th -27th, 2021 / 08:00 – 12:00 am (German Time), 14:00 – 18:00 (TW time) • Participating Taiwanese Companies: 7 • Organizing Units: German Trade Office Taipei, ARTC • Participation Fee: Free of Charge • Language: English • Software: Microsoft Teams or GoToWebinar The results of the matchmaking and selected best-practice examples of cooperation between German and Taiwanese companies will be presented during the 2nd German-Taiwanese Automotive Forum, which will be held in 2021. Participating Companies from Taiwan: CUB Elecparts Inc............................................................................................................................ 3 CubTEK Inc. ..................................................................................................................................... 4 EOI GmbH ....................................................................................................................................... -

FTSE Publications

2 FTSE Russell Publications 28 October 2020 FTSE Taiwan USD Net Tax Index Indicative Index Weight Data as at Closing on 27 October 2020 Constituent Index weight (%) Country Constituent Index weight (%) Country Constituent Index weight (%) Country Accton Technology 0.45 TAIWAN Formosa Petrochemical 0.44 TAIWAN SinoPac Financial Holdings Co. Ltd. 0.45 TAIWAN Acer 0.29 TAIWAN Formosa Plastics Corp 1.56 TAIWAN Synnex Technology International 0.23 TAIWAN Advantech 0.49 TAIWAN Formosa Taffeta 0.13 TAIWAN Taishin Financial Holdings 0.53 TAIWAN Airtac International Group 0.42 TAIWAN Foxconn Technology 0.23 TAIWAN Taiwan Business Bank 0.19 TAIWAN ASE Technology Holding 0.87 TAIWAN Fubon Financial Holdings 1.21 TAIWAN Taiwan Cement 0.82 TAIWAN Asia Cement 0.38 TAIWAN Genius Electronic Optical 0.2 TAIWAN Taiwan Cooperative Financial Holding 0.75 TAIWAN ASMedia Technology 0.24 TAIWAN Giant Manufacturing 0.31 TAIWAN Taiwan Fertilizer 0.15 TAIWAN Asustek Computer Inc 0.7 TAIWAN GlobalWafers 0.36 TAIWAN Taiwan Glass Industrial 0.08 TAIWAN AU Optronics 0.42 TAIWAN HIWIN Technologies Corp. 0.29 TAIWAN Taiwan High Speed Rail 0.26 TAIWAN Capital Securities 0.09 TAIWAN Hon Hai Precision Industry 3.82 TAIWAN Taiwan Mobile 0.64 TAIWAN Catcher Technology 0.54 TAIWAN Hotai Motor 0.81 TAIWAN Taiwan Secom 0.1 TAIWAN Cathay Financial Holding 1.28 TAIWAN HTC Corporation 0.08 TAIWAN Taiwan Semiconductor Manufacturing 42.94 TAIWAN Chailease Holding 0.73 TAIWAN Hua Nan Financial Holdings 0.67 TAIWAN TECO Electric & Machinery 0.21 TAIWAN Chang Hwa Commercial Bank 0.45 TAIWAN Innolux 0.34 TAIWAN TPK Holding Co Ltd 0.07 TAIWAN Cheng Shin Rubber Industry 0.27 TAIWAN Inventec Co. -

2019 Public Supplier List

2019 Public Supplier List The list of suppliers includes original design manufacturers (ODMs), final assembly, and direct material suppliers. The volume and nature of business conducted with suppliers shifts as business needs change. This list represents a snapshot covering at least 95% of Dell’s spend during fiscal year 2020. Corporate Profile Address Dell Products / Supplier Type Sustainability Site GRI Procurement Category Compal 58 First Avenue, Alienware Notebook Final Assembly and/ Compal YES Comprehensive Free Trade Latitude Notebook or Original Design Zone, Kunshan, Jiangsu, Latitude Tablet Manufacturers People’s Republic Of China Mobile Precision Notebook XPS Notebook Poweredge Server Compal 8 Nandong Road, Pingzhen IoT Desktop Final Assembly and/ Compal YES District, Taoyuan, Taiwan IoT Embedded PC or Original Design Latitude Notebook Manufacturers Latitude Tablet Mobile Precision Notebook Compal 88, Sec. 1, Zongbao Inspiron Notebook Final Assembly and/ Compal YES Avenue, Chengdu Hi-tech Vostro Notebook or Original Design Comprehensive Bonded Zone, Manufacturers Shuangliu County, Chengdu, Sichuan, People’s Republic of China Public Supplier List 2019 | Published November 2020 | 01 of 40 Corporate Profile Address Dell Products / Supplier Type Sustainability Site GRI Procurement Category Dell 2366-2388 Jinshang Road, Alienware Desktop Final Assembly and/ Dell YES Information Guangdian, Inspiron Desktop or Original Design Xiamen, Fujian, People’s Optiplex All in One Manufacturers Republic of China Optiplex Desktop Precision Desktop