Embedded Microcontrollers and Processor Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

HEWLETT-PACKARD JOURNAL Technical Information from the Laboratories of Hewlett-Packard Company

HEWLETT-PACKARD JOURNAL Technical Information from the Laboratories of Hewlett-Packard Company Contents: JANUARY 1981 Volume 32 • Number 1 Handheld Scanner Makes Reading Bar Codes Easy and Inexpensive, by John J. Uebbing, Donald the Lubin, and Edward G. Weaver, Jr. This lightweight unit contains all the elements required to convert bar code into digital signals. Reading Bar Codes for the HP-41C Programmable Calculator, by David R. Conklin and Thomas quickly Revere III A new accessory for HP's most powerful handheld calculator quickly enters data and programs from printed bar code. A High-Quality Low-Cost Graphics Tablet, by Donald J. Stavely The generation and modification of complex graphics images is greatly simplified by use of this instrument. Capacitive Stylus Design, by Susan M. Cardwell The stylus for the 91 11 A Graphics Tablet is slim, rugged, and provides tactile feedback. Programming the Graphics Tablet, by Debra S. Bartlett Software packages for several HP computers use the tablet's built-in capabilities to create diagrams, figures, and charts. Tablet/Display Combination Supports Interactive Graphics, by David A. Kinsell A graph ics tablet combined with vector-scan display system provides a powerful, inexpensive graph ics workstation. Programming for Productivity: Factory Data Collection Software, by Steven H. Richard This software package for HP 1000 Computers generates and manages a data collection system that's tailor-made for an individual factory. A Terminal Management Tool, by Francois Gaullier It provides a reentrant environment for HP 1000 Computers, simplifying the development of multiterminal applications. In this Issue: Computer application programs tell a computer how to accomplish specific tasks. -

Programs Processing Programmable Calculator

IAEA-TECDOC-252 PROGRAMS PROCESSING RADIOIMMUNOASSAY PROGRAMMABLE CALCULATOR Off-Line Analysi f Countinso g Data from Standard Unknownd san s A TECHNICAL DOCUMENT ISSUEE TH Y DB INTERNATIONAL ATOMIC ENERGY AGENCY, VIENNA, 1981 PROGRAM DATR SFO A PROCESSIN RADIOIMMUNOASSAN I G Y USIN HP-41E GTH C PROGRAMMABLE CALCULATOR IAEA, VIENNA, 1981 PrinteIAEe Austrin th i A y b d a September 1981 PLEASE BE AWARE THAT ALL OF THE MISSING PAGES IN THIS DOCUMENT WERE ORIGINALLY BLANK The IAEA does not maintain stocks of reports in this series. However, microfiche copies of these reports can be obtained from INIS Microfiche Clearinghouse International Atomic Energy Agency Wagramerstrasse 5 P.O.Bo0 x10 A-1400 Vienna, Austria on prepayment of Austrian Schillings 25.50 or against one IAEA microfiche service coupon to the value of US $2.00. PREFACE The Medical Applications Section of the International Atomic Energy Agenc s developeha y d severae th ln o programe us r fo s Hewlett-Packard HP-41C programmable calculator to facilitate better quality control in radioimmunoassay through improved data processing. The programs described in this document are designed for off-line analysis of counting data from standard and "unknown" specimens, i.e., for analysis of counting data previously recorded by a counter. Two companion documents will follow offering (1) analogous programe on-linus r conjunction fo i se n wit suitabla h y designed counter, and (2) programs for analysis of specimens introduced int successioa o f assano y batches from "quality-control pools" of the substance being measured. Suggestions for improvements of these programs and their documentation should be brought to the attention of: Robert A. -

The HP-41C: a Literate Calculator?

System Review The HP-41C: A Literate Calculator? Brian P Hayes Scientific American 415 Madison Ave New York NY 10017 Calculator vs Computer can be full of surprises, often to the frustration of the pro The computer and the programmable calculator seem grammer. to be following paths of convergent evolution. As the one The HP-41C, which was introduced by the Hewlett- is made smaller while the other gains in capability, the Packard Company about a year ago, is among the pro line of demarcation between them becomes more and grammable calculators that lie closest to the computer more arbitrary. For now at least, the programmable borderline. It comes close enough for the jargon of com calculator remains a distinct and lesser species, but it puters to be useful in describing it. At the Corvallis Divi shares many of the attributes of the computer. Moreover, sion of Hewlett-Packard, where the HP-41C is made, the shared attributes are chiefly the ones that make the they refer to the calculator itself as the ''mainframe" and computer an interesting machine. Both devices offer an to its accessory devices as the "peripherals." The intimate acquaintance with the powers and pleasures of calculator comes equipped with four input/output (I/O) algorithms. Both exhibit an enigmatic unpredictability: ports, through which the various elements of the system the response of the machine to any given stimulus is are interconnected. Because the peripherals do some data wholly deterministic, yet the behavior of a large program processing internally, the system might even be said to have "distributed intelligence." When compared with a computer, most programmable calculators have a rich instruction set, but they are defi cient in memory capacity and in facilities for communica tion with the user. -

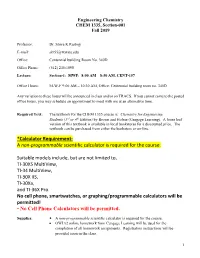

A Non-Programmable Scientific Calculator Is Required for the Course

Engineering Chemistry CHEM 1335, Section-001 Fall 2019 Professor: Dr. Shiva K Rastogi E-mail: [email protected] Office: Centennial building Room No. 340D Office Phone: (512) 245-1098 Lecture: Section-1: MWF: 8:00 AM – 8:50 AM, CENT-157 Office Hours: M-W-F 9:00 AM – 10:30 AM, Office: Centennial building room no. 340D Any variation to these hours will be announced in class and/or on TRACS. If you cannot come to the posted office hours, you may schedule an appointment to meet with me at an alternative time. Required Text: The textbook for the CHEM 1335 course is: Chemistry for Engineering Students (3rd or 4th Edition) by Brown and Holme (Cengage Learning). A loose leaf version of this textbook is available in local bookstores for a discounted price. The textbook can be purchased from either the bookstore or on-line. *Calculator Requirement: A non-programmable scientific calculator is required for the course. Suitable models include, but are not limited to, TI-30XS MultiView, TI-34 MultiView, TI-30X IIS, TI-30Xa, and TI-36X Pro. No cell phone, smartwatches, or graphing/programmable calculators will be permitted! • No Cell Phone Calculators will be permitted. Supplies: A non-programmable scientific calculator is required for the course. • OWLv2 online homework from Cengage Learning will be used for the completion of all homework assignments. Registration instructions will be provided soon in the class. 1 • A Turning Technologies account is required for this class. You can purchase a remote response pad at the bookstore for approximately $40. Alternately you can purchase a subscription that allows you to use a smartphone or tablet to submit your answers, but since this is the first year of this function this may be buggy. -

External Assessment Equipment List

External assessment equipment list External assessment - Bundaberg State High School 2020 Supervisors will check your equipment, including calculators, before you enter the assessment room. Approved equipment for all assessments • black or blue pens • 2B pencil, sharpener and eraser Note: a 2B pencil is only required for multiple choice questions and drawing graphs or diagrams. Black or blue pen must be used for all other written responses. • a highlighter • a clear plastic ruler • water in a clear unlabelled bottle • asthma inhaler. You may use a clear plastic container or ziplock bag to carry your equipment if needed. QCAA-approved calculators Only calculators approved for use in assessments are permitted. Scientific and graphics calculators must: • meet the requirements set out in the Scientific calculator list and Graphics calculator list • be handheld and solar or battery powered • be cleared of memory before the assessment/s. For assessments that permit the use of a non-programmable calculator (Accounting, Economics, Geography, Legal Studies), the calculator must be handheld and solar or battery powered. It must not allow access to the following functions: computer algebra system (CAS), spellchecker, dictionary, thesaurus or translator. Student devices A student device is a battery-powered laptop or tablet. For assessments that require the use of a student device, you will either bring your own or a device will be provided by your school. Your school will advise you of the arrangements that apply to student devices for your assessments. -

Build a Ti-59 Programmable Calculator

BUILD A TI-59 PROGRAMMABLE CALCULATOR The TI-59 Programmable calculator from Texas Instruments along with the HP-65 from Hewlett Packard was considered at one time to be the equivalent of a pocket PC in power and functionality during the late 70's and early 80's. The feature that made this calculator so popular was the Algebraic Operating System (AOS) that allowed the user to enter mathematical expressions including parentheses. Other features were the programmability that included being able to store up to 999 steps and 100 registers. Instructions included subroutine calls, conditional and flag tests, and looping capabilities. For the article I will submit a design for a DIY TI-59 Programmable Calculator that includes two keypads, pushbuttons, an LED display and an LCD display. In addition I will provide the firmware for the dsPIC30F6014 to emulate a subset of the TI-59 functions including the AOS system and some programming capabilities. The reader, using my article entry as a starting point could complete the remaining TI-59 functions and features. In addition it opens up the possibility of emulating modern TI and HP graphing calculators. User input and numeric key sequences are entered by means of the keypad or by initializing the Program Memory with an AOS expression or program, or through the serial port when it's configured for debugging. The TI-59 Programmable Calculator processes the selected operations by feeding data to the embedded dsPIC30F6014 micro-controller for evaluation, taking advantage of the double precision floating point math library for processing 64-Bit floating point operations, including arithmetic, trigonometric, scientific, and statistical and conversion functions. -

Microprocessor Or Microcontroller?

1/2/17 Microprocessor or Microcontroller? A little History n What is a computer? ¨ [Merriam-Webster Dictionary] one that computes; specifically : programmable electronic device that can store, retrieve, and process data. ¨ [Wikipedia] A computer is a machine that manipulates data according to a list of instructions. n Classification of Computers (power and price) ¨ Personal computers ¨ Mainframes ¨ Supercomputers ¨ Dedicated controllers – Embedded controllers 1 1/2/17 Mainframes IBM 9000 n Massive amounts of memory n Use large data words…64 bits or greater n Mostly used for military defense and large business data processing n Examples: IBM 4381, Honeywell DPS8 Personal Computers n Any general-purpose computer ¨ intended to be operated ¨ directly by an end user n Range from small microcomputers that work with 4-bit words to PCs working with 32-bit words or more n They contain a Processor - called different names ¨ Microprocessor – built using Very-Large-Scale Integration technology; the entire circuit is on a single chip ¨ Central Processing Unit (CPU) ¨ Microprocessor Unit (MPU) – similar to CPU http://en.wikipedia.org/wiki/Personal_computer 2 1/2/17 Supercomputers n Fastest and most powerful mainframes ¨ Contain multiple central processors (CPU) ¨ Used for scientific applications, and number crunching ¨ Now have petaflops performance n FLoating Point Operations Per Second (FLOPS) n Used to measure the speed f the computer n Examples of special-purpose supercomputers: ¨ Belle, Deep Blue, and Hydra, for playing chess ¨ Reconfigurable -

Team 3A 1961 to 1970 Professor Charles Bauer CS 485: Computers

Team 3A 1961 to 1970 Professor Charles Bauer CS 485: Computers & Society 24 January 2016 History of Computers 1961 to 1970 Significant developments of the period between 1961 and 1970 included both hardware and software. Important people like Gordon Moore, Ralph Baer and others played an important role in these developments, and these developments impacted society in more than one way. Hardware Development From factory robots to multitasking to the internet, this decade saw the rise of many innovations that were precursors to technologies today. As factories become more and more automated, we trace its roots back to 1961, where the first industrial robot “joined the assembly line at General Motors” (Robot). Named Unimate, this robot “took die castings from machines and performed welding on auto bodies”, tasks which were unpleasant for humans (Robot). Unimate had “six fully programmable axes of motion” and could handle weight of “up to 500 lbs” (Robot). Its “dedicated electronic control” set the stage to teach and operate future industrial robots (Robot). In 1964, the Dartmouth TimeSharing System (DTSS) was born. This system was comprised of two computers: the “General Electric Datanet30, which is used both as the remote console controller” and as the site for the “master executive program. It can control, through interrupts, the other computer, a General Electric GE235 , whose main functions is to compile 2 programs and to perform floatingpoint arithmetic” (Dartmouth). The DTSS serves as a precursor to a technology that all computers use today: multitasking. Although it has become an object of antiquity, the floppy disk was the first portable hardware that was an inexpensive and reliable way to “load instructions and install software updates into mainframe computers” (IBM). -

Arduino and Numerical Mathematics

Informatics in Education, 2020, Vol. 19, No. 2, 239–256 239 © 2020 Vilnius University DOI: 10.15388/infedu.2020.12 Arduino and Numerical Mathematics Đorđe HERCEG1, Dejana HERCEG2 1Department of Mathematics and Informaics, Faculty of Science, University of Novi Sad Novi Sad, Serbia 2Department of Power, Electronic and Telecommunication Engineering Faculty of Technical Sciences, University of Novi Sad Novi Sad, Serbia e-mail:[email protected], [email protected] Received: November 2019 Abstract. Connecting theory and practice in teaching is sometimes difficult, as it requires expen- sive or delicate equipment, thus limiting the teacher to giving demonstrations in which students are passive participants. Numerical mathematics, as an applied discipline, should be taught on real world examples. By using inexpensive Arduino hardware, we can create simple experiments that are easily reproduced by students. Furthermore, the experiments generate tangible data, which can be processed numerically. The choice of the software used for numerical processing is also an important issue. We present several exercises in numerical mathematics that are based on experiments in electrical engineering with Arduino, and show how to turn them into motivational examples. We also present our experiences in teaching using the developed exercises, as well as some important points and conclusions, which stem from discussions with the participating students and teachers. Keywords: interactive learning environments, numerical mathematics, Arduino, education, teaching. 1. Introduction Numerical mathematics is studied in some middle schools and in almost all mathe- matics courses at undergraduate level studies. Interpolation is introduced by means of Lagrange polynomial and Newton polynomials. The concept of definite integral is introduced as the Riemann integral, which is defined in terms of Riemann sums and its geometric interpretation. -

HP Calculator Programming Richard J

HP Calculator Programming Richard J. Nelson Introduction Do you use an HP calculator that has a programming capability, and do you actually use it? Of the 24 models, see Table 1 below, 23 are on the HP website 13, or 54.2%, are programmable. If the Home and Office machines are omitted, the numbers are: 17 models, and 13 or 76.5%, are programmable. What does this mean? A program is a sequence of instructions (functions and/or data) that are keyed (or loaded) into the calculator’s memory that will solve a particular problem or provide specific information. A program capability also includes special instructions that provide prompting for inputs and labeling for outputs. Another aspect of a program capability is the ability to perform decision logic so the particular parts of a program may be changed depending on the results of previous instructions. This capability provides “intelligence” to the program. The program capability of the 10 current models ranges from very simple such as the HP-12C to very complex (and very powerful) such as the HP 50g. Older HP calculators such as the HP-71B or HP-75C used a computer like programming language called BASIC. The HP-12C and HP-15C programing language is an RPN FOCAL(1) like language, and the HP 50g uses an RPL programming language. The algebraic calculators use what may be called an Aplet programming language. Table 1 – Current HP Calculator Products (24) # Financial Calculators Scientific & Graphing Home & Office 1 HP 10bII HP 10s HP Calcpad 100 2 HP 10bII+ HP-15C Limited Edition HP CalcPad 200 3 HP 20b HP 33s OfficeCalc 100 4 HP 30b HP 35s OfficeCalc 200 5 HP-12C HP 39gs OfficeCalc 300 6 HP-12C 30th Anniversary HP 39gII PrintCalc 100 7 HP-17bII+ HP 40gs QuickCalc 8 HP 48gII 9 HP 50g 10 SmartCalc HP 300s 5 of 7 = 71% programmable 8 of 10 = 80% programmable None programmable Note: Programmable calculators are in blue. -

Department of Chemical Engineering

DEPARTMENT OF CHEMICAL ENGINEERING TEL: -27-12-420-2475 Pretoria 0002 Republic of South Africa FAX: -27-12-420-5048 http://www.up.ac.za E-Mail: [email protected] THE ACQUISITION OF PERSONAL LAPTOPS/TABLETS/SMART PHONES AND POCKET CALCULATORS The Department of Chemical Engineering prescribes access to a laptop computer as a requirement for all students from the 2nd semester of the first year. Since access to and use of smart phones, tablets, e-readers and laptop computers are becoming standard practice, it will be appreciated if you could consider helping your bursar(s) in the acquisition of their own device(s). At minimum the Department expects a student to have his/her own laptop computer, since this will enable access to e-books, internet, UP-based repositories, prescribed software, etc. Apparatus: - Preferably a 15.6” Laptop Computer with Intel i5 or i7 CPU - 802.11a/b/g/n -enabled (preferably a/b/g/n/ac) WLAN and Gbit LAN and Bluetooth-enabled - At least 4 GB RAM Memory - Disk Drive > 500 GB HDD or > 256 GB SSD - Display resolution of 1440 x 900 or above (with VGA or HDMI or display port out) - Sufficient USB ports (e.g. 3 or 4) for printer & mouse & flash disk - 16 x DVD Multi Writer - Mouse - Carry bag - > 8 GB USB Memory Stick - Printer (confirm cost of printer vs cost of cartridges) Software: - At least the Windows 7 (64 bit) operating system. Please note that the Windows 10 operating system is current. - Word processing, Spreadsheet & Presentation combination (eg. MS Office or Office 365, or Office 2016 but there is a strong drive to use open access software, e.g. -

Programmable Calculator Programming Instructions Table of Contents

1151 PROGRAMMABLE CALCULATOR PROGRAMMING INSTRUCTIONS TABLE OF CONTENTS INTRODUCTION. • . • . • • . • . • . • . • • . • • . • • • . • . • . • 1 GENERAL.. • . • . • • • • • • . • . • . • . • • • . • • • • • • • . • • • • . • 1 Interchange Key . • • • . • . • . • . • • . • • • . • • . • • • . • . • • . 1 Learn Key . • • • . • . • • • . • • • . • . • . • . • . • . • . • . • . • • 1 Auto Key . • • • • • • • . • • . • . • • • • • . • . • . • . • • . • . • . • . 2 Progr am Reset Key. • . • • . • . • . • • . • . • . • • • • • . • . • . 2 Looping. • . • • • • • . • • . • . • . • . • • • . • . • • • • . • . • 3 Decimalization and Overcapacity. • . • • • . • • • . • . • • • . • • 4 Program Steps • • • • • . • . • • • . • . • . • • . • • • • . 4 BASIC PROGRM1MING. • • . • • • . • . • . • . • • • . • . • . • . • 5 Simple Programming. • . • . • . • . • • • • . • • . • . • . • • • . • . • . 5 Stack Constant • . • . • . • . • • . • . • . • . • . • .. • . • . • 5 Payroll Application. • . • . • . • . • . • . • . • . • . • . 6 Two Totals in the Stack • . • . • . • • • . • . • . • . • . • • • . • . • • . • 7 Cost/Sell Quotations . • . • • • • . • . • • • . • • • • • . • • • • . • 8 MULTIPLE AND ITERATIVE PROGRAMS. • . • . • • • . • . • 9 Looping at a Stop Command. • • . • . • • • • • • . • . • • . • . • • • 9 Invoicing. • . • . • . • • . • . • . • . • . • • . • . • . • • • • . • .. 11 Iterati ve Programs. • • . • . • • . • . • • . • . • • . • .• 12 Compound Interest. • • • . • . • • • . • . • . • . • • • . • . • . • . • . •. 13 Square Root. • • . • • •