Picosecond Pulse Generation Techniques & Pulser Capabilities

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The ZTX415 Avalanche Mode Transistor an Introduction to Characteristics, Performance and Applications

Application Note 8 Issue 2 January 1996 The ZTX415 Avalanche Mode Transistor An Introduction to Characteristics, Performance and Applications Neil Chadderton Introduction Avalanche mode devices can provide a few application circuit examples. extremely high switching speeds and (Please refer to Appendix A for a list of are capable of producing current outputs reference material). far in excess of that obtained from conventional circuits. These attributes lend themselves to many applications, including; laser diode drivers for ranging, measurement, and collision avoidance systems, Pockel cell drivers for laser Q switches, SAW device exciters, streak cameras and fast high voltage/ high current pulse generators. The Zetex Semiconductors ZTX415 is an avalanche transistor that ideally suits Figure 1 this mode of operation and application. Transistor Characteristics in the The device is available in the proven Avalanche Region. silicone E-Line package that assures excellent thermal properties to complement the high performance What Is An Avalanche avalanche characteristics. It is also Transistor? available in the SOT-23 surface mount Avalanche transistors are characterised package (as FMMT415) to enable very by a negative resistance region in their low inductance designs. V-I breakdown curve (usually called secondary breakdown) as illustrated in This Application Note outlines the Figure 1. This region permits controlled principle of avalanche mode operation, switching of very high currents in gives details on important parameter nanoseconds when appropriate external and operating conditions, and suggests AN 8 - 1 Application Note 8 Issue 2 January 1996 circuitry is employed. The output pulse reliability work. For example, devices on generated is limited by the primary a life test have produced current pulses breakdown BVCBO , the transistor’s ‘On- of 60A peak and 10ns pulse width for state’ voltage and the mean dissipation over 4 x 1011 times without failure. -

Speed of Light with Nanosecond Pulsed 650 Nm Diode Laser M

Speed of Light with Nanosecond Pulsed 650 nm Diode Laser M. Gallant May 23, 2008 The speed of light has been measured many different ways using many ingenious methods. The following note describes a method which is conceptually very easy to understand and fairly easy to implement. The technique is the simple time-of-flight optical pulse delay method using a fairly short (nanosecond) optical pulse and an oscilloscope with bandwidth between 50 - 100 MHz. THE LASER Common low power laser pointers, typically emit at a wavelength of 650 nm and operate from two to four 1.5 V button cells. Many of these lasers can be easily extracted from the pointer assembly and pulse-modulated to several hundred megahertz. The laser used here was removed from a low power (< 5mW) laser pointer assembly from a popular retail outlet. GENERATION OF SHORT OPTICAL PULSES The laser is prebiased below threshold, at 5 - 10 mA current (threshold current for the laser used here is 24 mA) using an inductor as a bias insertion element. A short (< 5 ns) electrical pulse modulates the laser. Since a very low duty cycle is used for pulsing the laser, fairly high current pulses are possible without degrading the laser. The actual forward current and voltage achieved during the drive pulse are dependent on the details of the I-V characteristic of the specific laser used, but are typically in the range of 50 - 100 mA and 6 - 10 V respectively. The short electrical pulse is generated using a simple avalanche transistor circuit. Due to the high frequency content of the short pulse, the actual shape of the current pulse driving the laser will depend on the circuit components (series resistors etc.) and parasitic electrical effects (series inductance of connection wires etc.) The circuit has been described by Jim Williams in a Linear Technology Measurement and Control Circuit Collection and has many other uses. -

AN79 F01 Cost While Saving Power

Application Note 79 September 1999 30 Nanosecond Settling Time Measurement for a Precision Wideband Amplifier Quantifying Prompt Certainty Jim Williams Introduction SETTLING TIME INPUT Instrumentation, waveform generation, data acquisition, feedback control systems and other application areas RING TIME utilize wideband amplifiers. New components (see page 2 “A Precision Wideband Dual Amplifier with 30ns Settling ALLOWABLE OUTPUT Time”) have introduced precision while maintaining high ERROR BAND speed operation. The amplifier’s DC and AC specifications SLEW OUTPUT approach or equal previous devices at significantly lower TIME DELAY TIME AN79 F01 cost while saving power. Figure 1. Settling Time Components Include Delay, Slew and Settling Time Defined Ring Times. Fast Amplifiers Reduce Slew Time, Although Amplifier DC specifications are relatively easy to verify. Longer Ring Time Usually Results. Delay Time is Normally a Small Term Measurement techniques are well understood, albeit often tedious. AC specifications require more sophisticated approaches to produce reliable information. In particular, pensation. Additionally, the architecture of very fast ampli- amplifier settling time is extraordinarily difficult to deter- fiers usually dictates trade-offs which degrade DC error mine. Settling time is the elapsed time from input applica- terms.1 tion until the output arrives at and remains within a Measuring anything at any speed requires care. Dynamic specified error band around the final value. It is usually measurement is particularly challenging. Reliable nano- specified for a full-scale transition. Figure 1 shows that second region settling time measurement constitutes a settling time has three distinct components. The delay high order difficulty problem requiring exceptional care time is small and is almost entirely due to amplifier in approach and experimental technique.2 propagation delay. -

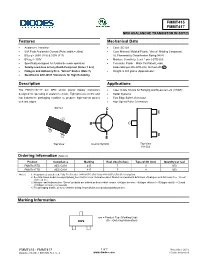

Fmmt415, Fmmt417

FMMT415 FMMT417 NPN AVALANCHE TRANSISTOR IN SOT23 Features Mechanical Data Avalanche Transistor Case: SOT23 60A Peak Avalanche Current (Pulse width = 20ns) Case Material: Molded Plastic. “Green” Molding Compound. BVCES > 260V (415) & 320V (417) UL Flammability Classification Rating 94V-0 BVCEO > 100V Moisture Sensitivity: Level 1 per J-STD-020 Specifically designed for Avalanche mode operation Terminals: Finish – Matte Tin Plated Leads. Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2) Solderable per MIL-STD-202, Method 208 e3 Halogen and Antimony Free. “Green” Device (Note 3) Weight: 0.008 grams (Approximate) Qualified to AEC-Q101 Standards for High Reliability Description Applications The FMMT415/417 are NPN silicon planar bipolar transistors Laser Diode Drivers for Ranging and Measurement (LIDAR) designed for operating in avalanche mode. Tight process control and Radar Systems low inductance packaging combine to produce high-current pulses Fast Edge Switch Generator with fast edges. High Speed Pulse Generators SOT23 C E B C B E Top View Device Symbol Top View Pin-Out Ordering Information (Note 4) Product Compliance Marking Reel size (inches) Tape width (mm) Quantity per reel FMMT415TD AEC-Q101 415 7 8 500 FMMT417TD AEC-Q101 417 7 8 500 Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant. 2. See http://www.diodes.com/quality/lead_free.html for more information about Diodes Incorporated’s definitions of Halogen- and Antimony-free, “Green” and Lead-free. 3. Halogen- and Antimony-free “Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds. -

A Fiber-Optically Triggered Avalanche Transistor Matic Test Equipment Involving Ac Bridges [8[

IEEE TRA~"SACTlO0:S ON INSTRU:vIEl\TATlON AND MEASUREMENT. VOL. 40. NO.3. JUl\E 1'191 25 Input signal ; 500 jJV 20 Amplifier gain ~ A Simulation result continuous curves Measured error points x x x A ; 200 o ::J 10 '"0 A 400 (f) ClJ 750 D:::: o 20 40 60 80 100 120 140 160 180 Phase difference <r (deg) Fig. 6. Extent of pha.'c compensation as a function of amplifier gain A. effcct [7 J. The schemc can also be successfully employed in auto A Fiber-Optically Triggered Avalanche Transistor matic test equipment involving ac bridges [8[. R. Jacob Baker, Gregory T. Perryman. and Phillip W. Watts Y. CONCLUSION It has been demonstrated that using feedback technique for phase Abstract-A silicon bipolar transistor operating in the avalanche re compensation in a PSD, the amplitudc of thc measurand can bc got gion is optically triggered into secondary breakdown, This transistor has been given the name fiber-optically triggered avalanche transistor directly without the need for a post-processing of the in-pha,e and (FOTAT), The FOTAT acts as an optical power discriminator. That quadrature components. Experimental results presented serve to is, secondar) breakdown occurs when the triggering optical power ex establish the easy applicability of the method to obtain a high de ceeds tbe triggering tbreshold of tbe FOT AT, This secondary break gree of phase compensation coupled with a fine resolution. Quan down is seen as a negative resistance between the collector and emitter. High voltage (> 100 V) nanosecond transition duration pulses arc gen titative comparison of the extent of compensation obtained exper erated using this negative resistance, imentally with that estimated by PC-simulation indicates good agreement. -

A Compact, Short-Pulse Laser for Near-Field, Range-Gated Imaging Fred J Zutavem, Wesley D

A Compact, Short-pulse Laser for Near-field, Range-gated Imaging Fred J Zutavem, Wesley D. Helgeson, and Guillermo M. Loubnel Sandia National Laboratories, Albuquerque, New Mexico, 87185-1 153 (505) 845-9128, FAX 845-3651, Email: [email protected] George J. Yates, Robert A. Gallegos, and Thomas E. McDonald Los Alamos National Laboratory, Los Alamos, New Mexico 87545 (505) 667-7529, FAX 665-4121, Email: [email protected] ABSTRACT This paper describes a compact laser, which produces high power, wide-angle emission for a near-field, range-gated, imaging system. The optical pulses are produced by a 100 element laser diode array (LDA) which is pulsed with a GaAs, photoconductive semiconductor switch (PCSS). The LDA generates 100 ps long, gain-switched, optical pulses at 904 nm when it is driven with 3 ns, 400 A, electrical pulses from a high gain PCSS. Gain switching is facilitated with this many lasers by using a low impedance circuit to drive an array of lasers, which are connected electrically in series. The total optical energy produced per pulse is 10 microjoules corresponding to a total peak power of 100 kW. The entire laser system, including prime power (a nine volt battery), pulse charging, PCSS, and LDA, is the size of a small, hand-held flashlight. System lifetime, which is presently limited by the high gain PCSS, is an active area of research and development. Present limitations and potential improvements will be discussed. The complete range-gated imaging system is based on complementary technologies: high speed optical gating with intensified charge coupled devices (ICCD) developed at Los Alamos National Laboratory (LANL)and high gain, PCSS-driven LDAs developed at Sandia National Laboratories (SNL). -

Avalanche Impedance Avalanche Transistor Avalanche Voltage Average Current

AVERAGE CURRENT 29 Avalanche breakdown in a particular diode might occur The exact value of the avalanche impedance for alternating with just a few volts of reverse bias, or it might take hundreds of current is the value of resistor that would be necessary to allow volts. Rectifier diodes do not undergo avalanche breakdown the same flow of reverse current. The average ZA for alternating until the voltage becomes quite large (see AVALANCHE current differs from the instantaneous value, which fluctuates VOLTAGE). A special type of diode, called the zener diode (see as the voltage rises and falls. Avalanche is usually undesirable ZENER DIODE), is designed to have a fairly low, and very pre- in alternating-current applications. cise, avalanche breakdown voltage. Such diodes are used as voltage regulators. Zener diodes are sometimes called avalanche diodes because of their low avalanche voltages. AVALANCHE TRANSISTOR The illustration shows graphically the current flow through An avalanche transistor is an npn or pnp transistor that is de- a diode as a function of reverse voltage. The current is so small, signed to operate with a high level of reverse bias at the emitter- for small reverse voltages, that it might be considered to be zero base junction. Normally, transistors are forward-biased at the for practical purposes. When the reverse voltage becomes suffi- emitter-base junction except when cutoff conditions are de- cient to cause avalanche breakdown, however, the current rises sired when there is no signal input. rapidly. Avalanche transistors are seen in some switching applica- tions. The emitter-base junction is reverse-biased almost to the point where avalanche breakdown occurs. -

An Overview of Pulsed Power System Design and Applications

PULSED POWER DESIGN AND APPLICATIONS 1 An Overview of Pulsed Power System Design and Applications Joshua Zaiter A Senior Thesis submitted in partial fulfillment of the requirements for graduation in the Honors Program Liberty University Spring 2021 PULSED POWER DESIGN AND APPLICATIONS 2 Acceptance of Senior Honors Thesis This Senior Honors Thesis is accepted in partial fulfillment of the requirements for graduation from the Honors Program of Liberty University. ______________________________ Carl Pettiford, Ph.D. Thesis Chair ______________________________ Kyung Kyoon Bae, Ph.D. Committee Member ______________________________ David Schweitzer, Ph.D. Assistant Honors Director ______________________________ Date PULSED POWER DESIGN AND APPLICATIONS 3 Abstract Pulsed power is the delivery of energy to a load in very short time frames. By reducing the time component, massive instantaneous power magnitudes are achieved, scaling up to the high terawatt range in some modern applications. The study of general system design and its applications have great academic merit. By analyzing the structure and breakdown of such a system, uses in various fields have been discovered, including cancer treatment and manufacturing. Liberty hopes to gain access to this research field by replicating two existing systems (with permission) and conducting tests to aid in societal progress. Results of high voltage pulse generators with nanosecond fall times can be expected in the future. PULSED POWER DESIGN AND APPLICATIONS 4 An Overview of Pulsed Power System Design and Applications Introduction The study of pulsed power and its applications is a growing topic of study within the scientific and engineering communities, with state-of-the-art technologies and systems revolutionizing processes in many different fields. -

Miniature High-Power Nanosecond Laser Diode Transmitters Utilizing Simplest Avalanche Drivers

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2018.2853563, IEEE Transactions on Power Electronics Miniature high-power nanosecond laser diode transmitters using the simplest possible avalanche drivers Sergey Vainshtein1, Valery Zemlyakov2, Vladimir Egorkin2, Andrey Maslevtsov3 and Alexey Filimonov3 1CAS group, University of Oulu, P.O. Box 4500, FIN-90014 Oulu, Finland 2National Research University of Electronic Technology – MIET, Bld. 1, Shokin Square, 124498, Zelenograd, Moscow, Russia 3Peter the Great St. Petersburg Polytechnic University, Polytechnicheskaya 29, 195251, St.-Petersburg, Russia Abstract. The-state-of-the-art in long-distance ten nanoseconds or so. The transmitter in all these near-infrared optical radars is the use of laser-diode- examples, however, cannot be considered either low-cost based miniature pulsed transmitters producing optical or miniature (i.e. comparable in price and size with an pulses of 3-10 ns in duration and peak power typically encapsulated laser diode), and these are the criteria of below 40W. The duration of the transmitted optical principal importance for most large market applications. pulses becomes a bottleneck in the task of improving The competing state-of-the-art solutions that satisfy these the radar ranging precision, particularly due to the criteria are pulsed switches based on the latest progress made in developing single photon avalanche -

An Accurate and Compact High Power Monocycle Pulse Transmitter for Microwave Ultra-Wideband Radar Sensors with an Enhanced SRD M

ADVANCED ELECTROMAGNETICS, VOL.8, NO. 3, SEPTEMBER 2019 An Accurate and Compact High Power Monocycle Pulse Transmitter for Microwave Ultra-Wideband Radar Sensors with an enhanced SRD model: Applications for Distance Measurement for lossy Materiel Younes AHAJJAM1;3, Otman AGHZOUT1;2, Jose` M. CATALA-CIVERA3, Felipe PENARANDA-FOIX˜ 3, and Abdellah DRIOUACH1 1 Dept. of Physics, Faculty of Science, Abdelmalek Essaadi University, Tetouan, Morocco. 2 Department of Telecommunication, ENSA. LabSIT-FS, UAE Univertisy, Tetouan, Morocco 3 Instituto ITACA. Universitat Politecnica` de Valencia.` Camino de Vera s/n. 46022 Valencia, Espana.˜ *corresponding author, E-mail: [email protected] Abstract and high penetration capability. Instead of higher frequen- cies, which the losses are enormous, Lower frequencies up In This paper, a high power sub-nanosecond pulse trans- to 3.5 GHz are preferred for the application radar in lossy mitter for Ultra-wideband radar sensor is presented. The material. The corresponding pulse width of the generated backbone of the generator is considered as a step recov- baseband pulses is approximately 200 ps. There are vari- ery diode and unique pulse injected into the circuit, which ous techniques to generate UWB pulses around this range. gives rise to an ultra-wideband Gaussian pulse. The tran- The basis of a classical UWB short pulse generator is a sistor driver and transmission line pulse forming the whole driver, a pulse sharpener and a pulse forming network. The network are investigated in detail. The main purpose of this driver converts the step-like waveform in Gaussian pulses, work is to transform a square waveform signal to a driv- and the pulse sharpener converts slow rise time waveform ing pulse with the timing and the amplitude parameters re- edge to a faster one. -

An Ultrashort Electric Field Pulse Generator Using Avalanche Breakdown Transistors and the Open Circuit Transmission Line Techni

An Ultrashort Electric Field Pulse Generator using Avalanche Breakdown Transistors and the Open Circuit Transmission Line Technique for Nanosecond Electroporation Ilan Wyn Davies*+ and Christopher Paul Hancock*+ *School of Computer Science and Electronic Engineering, Bangor University, Bangor, United Kingdom. +Creo Medical Group PLC. Chepstow, United Kingdom. Abstract— An ultrashort electric field pulse generator based on II. THEORY OF OPERATION relatively slow charging and ultrafast discharging of a co-axial transmission line in conjunction with a stack of low-cost A. Open Circuit Co-axial Transmission Line Technique avalanche breakdown transistors which operate as a fast Pulse generation is possible by using an open circuit CTL switching element has been designed and built. This low-cost circuit design produces well defined ultrashort electric field as a low-cost high Q storage element consisting of distributed pulses with symmetrical rise and fall times of less than 2 ns. The series inductors and shunt capacitors with minimal series pulse duration is determined by the length of the open-circuit resistance and shunt conductance. Discharging an open- transmission line. Initial results indicate that the circuit is ended delay line through a fast switching element, provides a capable of generating well defined nanosecond electroporation means of producing ‘flat-top’ rectangular pulse with steep pulses to support nanosecond-pulse-based applications in rise and fall times of less than 2 ns in a simple and affordable biology, medicine and/or in a cost-effective manner. manner [8]-[11]. Index Terms— Ultrashort Electric-Field Pulse, Transmission The CTL with a characteristic impedance Z0, and a length, Lines, Avalanche Breakdown Transistors, Circuit Design & l, and dielectric constant, ε , is charged to a voltage level, V , Applications. -

Drive Electronics for Pulsed Laser Diodes Power Where It Matters

Laser Diodes Drive Electronics for Pulsed Laser Diodes Power where it Matters Winfried Reeb, Laser Components GmbH, Olching In portable optoelectronic measurement technology laser sources are getting smaller and more affordable in areas such as distance and speed measurement, laser scanners, and medical and military techno- logy. Suitable drive electronics are required for high-power or pulsed laser diodes – being the heart of the emitter – to deliver an optimal performance. It should have been a successful product presentation. When the big potential client pushed the button on the laser rangefinder, however, no measurement was taken and the display remained dark. As it turned out, too much of a current destroyed the laser diode. This case left behind a disappointed customer – and a lost business opportunity. In other cases, for example, in security or medical technology, incorrect circuits can have far more serious implications! 1 Time-of-flight Measurement – Operating Principle Optical sensors for rangefinding from several meters to kilometers usually employ the time-of-flight (TOF) principle. The working principle is simple: a temporally modulated light pulse is sent out, sharply collimated by the emitter optics. From the arrival time of the reflected light the time of flight Dt can be determined. Using the speed of light, c, the distance l can be calculated. Since the light travels the distance twice, the result has to be divided by two. The refractivity of the surrounding medium, n, reduces the speed of light. c · Dt l= (Eq. 1) 2 · n 02/19 / V03 IF lc/application-reports/lc-electronics/drive-electronics-pulsed-laser-diodes 1 Germany & Other Countries France United Kingdom Nordic Countries USA Laser Components GmbH Laser Components S.A.S.