5Th-Gen-Core-Family-Datasheet-Vol-1.Pdf

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Heater Element Specifications Bulletin Number 592

Technical Data Heater Element Specifications Bulletin Number 592 Topic Page Description 2 Heater Element Selection Procedure 2 Index to Heater Element Selection Tables 5 Heater Element Selection Tables 6 Additional Resources These documents contain additional information concerning related products from Rockwell Automation. Resource Description Industrial Automation Wiring and Grounding Guidelines, publication 1770-4.1 Provides general guidelines for installing a Rockwell Automation industrial system. Product Certifications website, http://www.ab.com Provides declarations of conformity, certificates, and other certification details. You can view or download publications at http://www.rockwellautomation.com/literature/. To order paper copies of technical documentation, contact your local Allen-Bradley distributor or Rockwell Automation sales representative. For Application on Bulletin 100/500/609/1200 Line Starters Heater Element Specifications Eutectic Alloy Overload Relay Heater Elements Type J — CLASS 10 Type P — CLASS 20 (Bul. 600 ONLY) Type W — CLASS 20 Type WL — CLASS 30 Note: Heater Element Type W/WL does not currently meet the material Type W Heater Elements restrictions related to EU ROHS Description The following is for motors rated for Continuous Duty: For motors with marked service factor of not less than 1.15, or Overload Relay Class Designation motors with a marked temperature rise not over +40 °C United States Industry Standards (NEMA ICS 2 Part 4) designate an (+104 °F), apply application rules 1 through 3. Apply application overload relay by a class number indicating the maximum time in rules 2 and 3 when the temperature difference does not exceed seconds at which it will trip when carrying a current equal to 600 +10 °C (+18 °F). -

JOEL H. WESTRA, PH.D. ◊ Calvin University 3201 Burton St SE Grand Rapids, MI 49546 ◊ Tel: 616/526–6727 Email: [email protected] ◊ 24 May 2021

JOEL H. WESTRA, PH.D. ◊ Calvin University 3201 Burton St SE Grand Rapids, MI 49546 ◊ Tel: 616/526–6727 Email: [email protected] ◊ 24 May 2021 ACADEMIC APPOINTMENTS Associate Professor 2012–present Department of Politics and Economics – Calvin University Assistant Professor 2007–2012 Department of Politics and Economics – Calvin University Postdoctoral Fellow 2005–2007 John G. Tower Center for Political Studies – Southern Methodist University Visiting Lecturer 2004–2005 Committee on International Relations – The University of Chicago ADMINISTRATIVE APPOINTMENTS Department Chair 2016–present Department of Politics and Economics (co-chair) – Calvin University (2021–present) Department of Political Science – Calvin University (2016–2021) Program Director 2008–present Pre-Law Program – Calvin University Program Coordinator 2001–2003 Program on International Politics, Economics and Security (PIPES) – The University of Chicago EDUCATION Ph.D., Political Science 2004 Department of Political Science – The University of Chicago Subfields: International Relations, Political Theory, and Research Methods Dissertation Title: “Law, Power, and Argumentation: The UN Charter and Uses of Armed Force by Major Powers since 1945” Dissertation Committee: Duncan J. Snidal (chair), Robert A. Pape, Jack L. Goldsmith III M.A., Social Sciences 2000 Division of the Social Sciences – The University of Chicago Thesis Title: “Morality beyond the Polity: Political Realism and International Society from an Augustinian Perspective” Thesis Committee: Jean Bethke Elshtain (advisor), Lloyd Rudolph B.A., Political Science (Summa Cum Laude) 1998 Department of Political Science and the Honors College – University of Houston University Honors and Honors in Political Science Minors in Chemistry and Mathematics Thesis Title: “On the Moral Dilemma of Strategic Nuclear Weapons Targeting: An Exhumation of Jus in Bello Theory” Thesis Committee: Ross M. -

Keyword Index

Neuropsychopharmacology (2014) 39, S692–S709 & 2014 American College of Neuropsychopharmacology. All rights reserved 0893-133X/14 www.neuropsychopharmacology.org Keyword Index 10q24.32 . ............... ................T156 Adolescent Depression . .M198 22q11....................................T37 adolescent development . M100, W223, M133 4-Chlorokynurenine . ....................... W226 adolescent stress . .........................M21 5-HT2A receptor . ....................... W196 ADRA1A . ........................T262 5-HT2C . ................................M130 adrenergic receptor . ....................... W205 5-HT3 receptors........................... W246 adult....................................W82 5-HT7 . ................................ M93 Adversity. ........................M199 5C-CPT . ................................W62 aerobic . ........................M163 5HT5A receptor antagonist....................W191 affective disorders . ........................W80 [11C]carfentanil............................M143 affective neuroscience . M167 affective priming . ........................M112 A African American . ........................T197 aggression . ........... M78, M211, T154, W74 aging..........W31, M181, M223, T54, W30, W31, W227, ABCB gene . ............................ W75 M141, M156, M232, W5, W104 ABCB1 . ................................T254 Agomelatine . ........................W210 Abuse Liability ........................... W160 Agonist . ....................... M266 Abuse Potential ............................W165 agoraphobia -

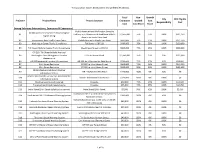

Draft Project List 2017-04-24

Transportation System Development Charge (TSDC) Project List Total Non- Growth City SDC Eligible Project # Project Name Project Location Estimated Growth Cost Responsibility Cost Cost Cost Share Share Driving Solutions (Intersections, Extensions & Expansions) Molalla Avenue from Washington Street to Molalla Avenue/ Beavercreek Road Adaptive D1 Gaffney Lane; Beavercreek Road from Molalla $1,565,000 75% 25% 100% $391,250 Signal Timing Avenue to Maple Lane Road D2 Beavercreek Road Traffic Surveillance Molalla Avenue to Maple Lane Road $605,000 75% 25% 100% $151,250 D3 Washington Street Traffic Surveillance 7th Street to OR 213 $480,000 75% 25% 100% $120,000 D4 7th Street/Molalla Avenue Traffic Surveillance Washington Street to OR 213 $800,000 75% 25% 100% $200,000 OR 213/ 7th Street-Molalla Avenue/ D5 Washington Street Integrated Corridor I-205 to Henrici Road $1,760,000 75% 25% 30% $132,000 Management D6 OR 99E Integrated Corridor Management OR 224 (in Milwaukie) to 10th Street $720,000 75% 25% 30% $54,000 D7 14th Street Restriping OR 99E to John Adams Street $845,000 74% 26% 100% $216,536 D8 15th Street Restriping OR 99E to John Adams Street $960,000 80% 20% 100% $192,000 OR 213/Beavercreek Road Weather D9 OR 213/Beavercreek Road $120,000 100% 0% 30% $0 Information Station Warner Milne Road/Linn Avenue Road Weather D10 Warner Milne Road/Linn Avenue $120,000 100% 0% 100% $0 Information Station D11 Optimize existing traffic signals Citywide $50,000 75% 25% 100% $12,500 D12 Protected/permitted signal phasing Citywide $65,000 75% 25% 100% -

F. Bertinelli, Presentation 01-Sep-06

TCC, 1 September 2006 AT-CRI Progress and Outlook for Interconnections F. Bertinelli / AT-CRI (10 minutes) (on behalf of IC Team) • recent “news” since MARIC 2nd August • restart sector 4-5 • sector 7-8 1 SomeSome recentrecent newsnews…… AT-CRI Organisational: • internal AT reorganisation, IC project consolidation • already reinforcement of QA (D. Tommasini/MAS, R. Lopez/CRI) • F523: 4th full team contractually implemented, effective starting week 39/06 • Workflow: developed detailed workflow of activities, including: • pre-inspection and reflectometry • VAC and MEL tests (with recently introduced extended tests MPAQ and MHVQN) • ACR instrumentation • Planning: developed detailed planning, by activities, slots and weeks, extending to closure of W bellows and sector VAC testing TCC – September 2006 – F. Bertinelli 2 RestartRestart sectorsector 44--55 AT-CRI • IC work restarted this week 35/06 • IC work now in 4-5, continuing to 3-4 • detailed planning set up (activities, slots, weeks) for 4-5; 3-4 will follow • 2 full teams (at the moment BR, US, TIG: V, E, X, C’) • until week 39/06 will work Monday to Thursday, then extend to Saturday • 3rd large team starting week 39 • “forfait” (“lump sum”) invoicing • expected average productivity: 8 activities / week-team (but prepare work up to 10 - 12) • first partial results from week 35/06: • V1/V2 & E: 19 •BR: 16 •US: 11 • X: 12, C’: 21 TCC – September 2006 – F. Bertinelli 3 WorkflowWorkflow ICIC AT-CRI from P. Fessia TCC – September 2006 – F. Bertinelli 4 SectorSector 44--5:5: detaileddetailed planningplanning AT-CRI Planning sector 4-5 version 0.2 P. -

Likely to Be Funded Transportation System

Table 2: Likely to be Funded Transportation System Project # Project Description Project Extent Project Elements Priority Further Study Identify and evaluate circulation options to reduce motor OR 213/Beavercreek Road Refinement OR 213 from Redland Road to Molalla D0 vehicle congestion along the corridor. Explore alternative Short-term Plan Avenue mobility targets. Identify and evaluate circulation options to reduce motor I-205 at the OR 99E and OR 213 Ramp vehicle congestion at the interchanges. Explore alternative D00 I-205 Refinement Plan Short-term Terminals mobility targets, and consider impacts related to a potential MMA Designation for the Oregon City Regional Center. Driving Solutions (Intersection and Street Management- see Figure 16) Molalla Avenue from Washington Street to Molalla Avenue/ Beavercreek Road Deploy adaptive signal timing that adjusts signal timings to D1 Gaffney Lane; Beavercreek Road from Molalla Short-term Adaptive Signal Timing match real-time traffic conditions. Avenue to Maple Lane Road Option 1: Convert 14th Street to one-way eastbound between McLoughlin Boulevard and John Adams Street: • Convert the Main Street/14th Street intersection to all-way stop control (per project D13). • From McLoughlin Boulevard to Main Street, 14th Street would be restriped to include two 12-foot eastbound travel lanes, a six-foot eastbound bike lane, a six-foot westbound contra-flow bike lane, and an eight-foot landscaping buffer on the north side • From Main Street to Washington Street, 14th Street would be restriped to include -

Keyword Index

Neuropsychopharmacology (2012) 38, S479–S521 & 2012 American College of Neuropsychopharmacology. All rights reserved 0893-133X/12 www.neuropsychopharmacology.org S479 Keyword Index 10b-Hydroxyestra-14-diene-3-one . W87 M114, M115, M116, M119, M123, M130, M131, M132, M134, M140, M142, 13C magnetic resonance spectroscopy . W34 M143, M144, M145, M146, M149, M150, M151, M152, M154, M155, M156, M157, M158, M159, M166, M168, M172, M174, M178, M179, M181, M182, 22q11 deletion . T123 M185, M186, M187, M188, M193, M197, M198, M199, M200, M201, M202, 2-AG . .23.2, 23.3, M145, T69, T161 M205, M212, T3, T5, T8, T13, T16, T17, T20, T22, T24, T25, T27, T31, T35, 3-MT . M182 T44, T49, T51, T58, T60, T66, T67, T72, T75, T77, T79, T80, T82, T83, T86, T88, T91, T95, T98, T99, T103, T109, T111, T113, T114, T116, T117, T119, 5-HT . 14.2, 17.4, 44.2, 52, M19, M45, M64, M72, M75, M91, T121, T125, T126, T128, T138, T140, T144, T147, T148, T151, T153, T154, M115, M144, M147, M154, M157, M161, M162, M183, M185, M186, T17, T49, T158, T161, T166, T167, T171, T173, T176, T177, T179, T181, T185, T188, T53, T120, T163, T194, W54, W125, W165, W176, W191 T189, T192, T194, T197, T198, T202, T203, T209, T210, W3, W5, W8, W10, 5-HT6 . .W125 W18, W20, W31, W32, W45, W46, W53, W54, W57, W64, W71, W72, W75, W76, W81, W83, W84, W87, W93, W94, W97, W100, W103, W104, W105, A W106, W107, W115, W116, W117, W118, W120, W124, W129, W137, W138, W143, W154, W158, W159, W160, W169, W172, W173, W176, W177, W186, W188, W195, W197, W199, W201, W203, W208, W214, W218 AAV . -

Bibliography of Tritium Studies Related to Hydrology Through 1966

Bibliography of Tritium Studies Related to Hydrology Through 1966 GEOLOGICAL SURVEY WATER-SUPPLY PAPER 1900 Bibliography of Tritium Studies Related to Hydrology Through 1966 By EDWARD C. RHODEHAMEL, VERONICA B. KRON, and VERDA M. DOUGHERTY GEOLOGICAL SURVEY WATER-SUPPLY PAPER 1900 A contribution to the International Hydrological Decade UNITED STATES GOVERNMENT PRINTING OFFICE, WASHINGTON : 1971 UNITED STATES DEPARTMENT OF THE INTERIOR WALTER J. HICKEL, Secretary GEOLOGICAL SURVEY William T. Pecora, Director Library of Congress catalog-card No. 70-608171 For sale by the Superintendent of Documents, U.S. Government Printing Office Washington, D.C. 20402 Price 75 cents (paper cover) CONTENTS Page Abstract 1 Introduction ___________________ 1 Purpose and scope _ ___ 1 General nature, sources, and abundance of tritium _ 2 Possible applications of tritium in hydrology ___ _ 5 Description of the bibliography _____ _ 6 Serial publications cited in bibliography of tritium ___ _ 8 Classification index principal topics and subject code __________ 21 Main bibliography bibliography and author index ____________ 27 Classification index principal subject index ________________ 147 Auxiliary reference list __________________________ ___ 161 Analytical methods _______________________________ 161 Atmosphere __________________________________ 162 Biology _________________________________________ 164 Geologic abundance _____________________________ 164 Ground water ________________________________ 165 Handling, health, and storage ________________________ -

Wind Speed Guide

DESIGN FACTORS WIND CLASSIFICATION, Wind speeds have been determined using the following factors, in accordance with AS/NZS1170.2:2011 500 year design return period and an average fi ve metre structure height. WE'LL BRING THE Note: A 5% allowance has been used when allocating the wind classifi cation. TERRAIN CATEGORIES (MZ,cat) SHIELDING FACTOR (MS) TOPOGRAPHIC EFFECT (MT) Terrain Category Regions A, B, C & D Shielding Classifi cation Factor Topographic Classifi cation Factor 1 1.05 T0 1.00 Full Shielding (FS) 0.85 1.5 0.98 T1 1.10 T2 1.20 2 0.91 Partial Shielding (PS) 0.95 T3 1.30 2.5 0.87 No Shielding (NS) 1.00 DIRECTION MULTIPLIER (M ) 3 0.83 D In All Cases a factor of 1.00 NOTE The method used for calculating the design gust wind speeds Stratco does not accept liability for any loss or damage has been developed by Stratco with the assistance of suitably su ered as a result of any errors in the interpretation or qualifi ed engineers in order to comply with the requirements application of this design guide. Any person wishing to check of AS/NZS1170.2:2011 and classifi ed in accordance with the any calculations made by them pursuant to this method may wind classifi cations allocated in AS4055:2012. wish to seek independent engineering advice. WIND SPEED EXAMPLES The examples below show typical applications of the rationalised gust wind speeds. For a full analysis refer to AS/NZS1170.2:2011. REGION A - N1 (W28), REGION B - N2 (W33) AND REGION C - C1 (W41) REGION A - N3 (W41), REGION B - N4 (W50) AND REGION C - C3 (W60) FLAT SUBURBIA STRUCTURE SITED IN UNDULATING SPARSELY POPULATED TERRAIN PREVAILING WIND PREVAILING WIND REGION A - N2 (W33), REGION B - N3 (W41) AND REGION C - C2 (W50) REGION A - N3 (W41) REGION B - N4 (W50) AND REGION C - C3 (W60) STRUCTURES BUILT ADJACENT TO AN OVAL OR LARGE VACANT LOT SUBJECT TO PREVAILING WINDS. -

Online NC K-12 Championship Charlotte Chess Center

3/18/2021 Online NC K-12 Championship ~ Charlotte Chess Center 2021 North Carolina Online K-12 Championship K-12 Championship, K-8 Championship, K-5 Championship, K-3 Championship, K-1 Championship, K-12 U1500, K-8 U1200 and Blitz Championship sections Saturday-Sunday, March 6-7, 2021 INFO REGISTER ENTRIES PAIRINGS STANDINGS TEAMS GAMES HOW TO PLAY LIVE HELP FAQ PRIZES Individual Standings K-12 CHAMPIONSHIP K-12 U1500 K-8 CHAMPIONSHIP K-8 U1200 K-5 CHAMPIONSHIP K-3 CHAMPIONSHIP K-1 CHAMPIONSHIP K-12 BLITZ K-6 BLITZ PLAYOFF Standings Round 6/6 ~ Current live games: 0 No. Team Player's Name Rating Rnd1 Rnd2 Rnd3 Rnd4 Rnd5 Rnd6 Score Tb1 Tb2 Tb3 Tb4 Award 1 NCKOONTZT VIR DATT 1121 W65 D23 W46 W24 W8 W3 5.5 19 21 18.5 81 1st 2 NCGREYF ENZO RESTELLI 1559 W33 W5 W35 W4 L3 W12 5 22 25 19 91 2nd 3 NCMETRO SMAYAN AMMASANI 1614 W58 W34 W16 W11 W2 L1 5 21.5 23.5 20 87.5 3rd 4 NCELON ETHAN LIU 1790 W32 W50 W26 L2 W22 W7 5 19.5 22 18 85 4th 5 NCMORRIS AARNA GUPTA 882 W36 L2 W59 W48 W11 W15 5 18 20 16 75 5th 6 NCHUNTR AARAV TRIVEDI 1089 L22 W62 W61 W56 W37 W14 5 15 17 15 66 6th 7 NCWESLEY SAHASRA RALLABANDI 1336 W19 W12 D25 W10 W9 L4 4.5 22 25.5 18 89 7th 8 NCGHOES LILLIAN YANG 1268 W15 W14 D22 W45 L1 W13 4.5 21 23.5 17 92 8th 9 NCDA JUDSON ROEDERER 1212 H W47 W23 W25 L7 W24 4.5 17.5 17.5 15.5 70.5 9th 10 NCELON NAMISH KONDABATHINI 1076 W39 D45 W27 L7 W46 W23 4.5 17 19.5 15.5 76 10th 11 NCDA LINGAA VENKATARAJA 1352 W72 W28 W13 L3 L5 W37 4 21 22 16 81 11th 12 NCBARR ISHAN SUNDARAM 841 W71 L7 W51 W26 W21 L2 4 19.5 20.5 15 76 12th 13 NCHUNTR EMMETT WALLS -

Deterrence in the Twenty-First Century

House of Commons Defence Committee Deterrence in the twenty-first century Eleventh Report of Session 2013–14 Volume II Written evidence Ordered by the House of Commons to be published 11 March 2014 Published on 27 March 2014 by authority of the House of Commons London: The Stationery Office Limited The Defence Committee The Defence Committee is appointed by the House of Commons to examine the expenditure, administration, and policy of the Ministry of Defence and its associated public bodies. Current membership Rt Hon James Arbuthnot MP (Conservative, North East Hampshire) (Chair) Mr Julian Brazier MP (Conservative, Canterbury) Rt Hon Jeffrey M. Donaldson MP (Democratic Unionist, Lagan Valley) Mr James Gray MP (Conservative, North Wiltshire) Mr Dai Havard MP (Labour, Merthyr Tydfil and Rhymney) Adam Holloway MP (Conservative, Gravesham) Mrs Madeleine Moon MP (Labour, Bridgend) Sir Bob Russell MP (Liberal Democrat, Colchester) Bob Stewart MP (Conservative, Beckenham) Ms Gisela Stuart MP (Labour, Birmingham, Edgbaston) Derek Twigg MP (Labour, Halton) John Woodcock MP (Labour/Co-op, Barrow and Furness) The following Members were also members of the Committee during this inquiry. Thomas Docherty MP (Labour, Dunfermline and West Fife) Penny Mordaunt MP (Conservative, Portsmouth North) Sandra Osborne MP (Labour, Ayr, Carrick and Cumnock) Powers The Committee is one of the departmental select committees, the powers of which are set out in House of Commons Standing Orders, principally in SO No 152. These are available on the internet via www.parliament.uk. Publications The Reports and evidence of the Committee are published by The Stationery Office by Order of the House. All publications of the Committee (including press notices) are on the internet at www.parliament.uk/parliament.uk/defcom. -

Mamaroneck Ave

Mamaroneck Ave First Name Last Name School 10:00-11:15 12:45-2:00 2:15-3:30 Francesca Acocella-Lilien MAS W7 W25 W2 Gina Ahearn MAS W7 W50 W26 Carrie Amon MAS W9 W11 W49 Nicole Bautista MAS W7 W2 W49 Danielle Beshar MAS W51 W25 W49 Alice Borsella MAS W27 W25 W53 Audrey Bruno MAS W9 W40 W49 Diane Campbell MAS W1 W16 W10 Donna Carella MAS W29 W46 W24 Laura Caterino MAS W8 W48 W48 Jennifer Cereola MAS W55 W2 W24 Elise Chipley MAS W5 W2 W42 Christina Ciraco MAS W17 W45 W19 Kari Cooke MAS W1 W35 W10 James Cunningham MAS W27 W25 W10 Carolyn Day MAS W1 W43 W19 Michelle Desjardin MAS W20 W34 W19 Trevor Dimmie MAS W47 W34 W2 Lori Dressler MAS W38 W11 W43 Meryl Elkin MAS W55 W3 W28 Maria Ellin MAS W21 W34 W49 Kerri Fay MAS W9 W3 W46 Amanda Franco MAS W17 W25 W50 Mindy Friedman MAS W20 W2 W42 Madeline Gilbert MAS W18 W2 W28 Iris Hernandez MAS W12 W44 W40 Jeannine Horan MAS W7 W25 W49 Dorene Hoyt MAS W7 W25 W49 Alison Ivler MAS W55 W25 W2 Jeanette Jimenez MAS W8 W45 W49 Marcus Jones MAS W47 W50 W46 Ellen Katz MAS W30 W43 W28 Alison Kelly MAS W30 W11 W42 Christine Kenny MAS W4 W43 W19 Janet Knight MAS W30 W50 W35 Chris Kumrow MAS W55 W25 W49 Helen Lauber MAS W30 W25 W40 Frank LoCurto MAS W13 W25 W46 Madeline Lukas MAS W8 W23 W46 Susan MacMurdy MAS W9 W16 W40 Stacey Magrone MAS W30 W2 W42 Julie Marconi MAS W30 W25 W50 Mickey Mariash MAS W55 W40 W28 Colleen Melnyk MAS W30 W22 W24 Kathleen Melvin MAS W18 W25 W28 Jim Monaco MAS W1 W16 W46 Dawn Moriwaki MAS W38 W41 W13 Ann Mosquera MAS W47 W50 W28 Janice O'Byrne MAS W18 W16 W41 Shannon O'Donnell (MAS)