Nanowire Transistors Physics of Devices and Materials in One Dimension

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Nanowire-Based Light-Emitting Diodes: a New Path Towards High-Speed Visible Light Communication." (2017)

University of New Mexico UNM Digital Repository Physics & Astronomy ETDs Electronic Theses and Dissertations Fall 9-30-2017 NANOWIRE-BASED LIGHT-EMITTING DIODES: A NEW PATH TOWARDS HIGH- SPEED VISIBLE LIGHT COMMUNICATION Mohsen Nami University of New Mexico Follow this and additional works at: https://digitalrepository.unm.edu/phyc_etds Part of the Astrophysics and Astronomy Commons, Electromagnetics and Photonics Commons, Nanoscience and Nanotechnology Commons, Nanotechnology Fabrication Commons, Physics Commons, and the Semiconductor and Optical Materials Commons Recommended Citation Nami, Mohsen. "NANOWIRE-BASED LIGHT-EMITTING DIODES: A NEW PATH TOWARDS HIGH-SPEED VISIBLE LIGHT COMMUNICATION." (2017). https://digitalrepository.unm.edu/phyc_etds/168 This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at UNM Digital Repository. It has been accepted for inclusion in Physics & Astronomy ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact [email protected]. Mohsen Nami Candidate Physics and Astronomy Department This dissertation is approved, and it is acceptable in quality and form for publication: Approved by the Dissertation Committee: Professor: Daniel. F. Feezell, Chairperson Professor: Steven. R. J. Brueck Professor: Igal Brener Professor: Sang. M. Han i NANOWIRE-BASED LIGHT-EMITTING DIODES: A NEW PATH TOWARDS HIGH-SPEED VISIBLE LIGHT COMMUNICATION by MOHSEN NAMI B.S., Physics, University of Zanjan, Zanjan, Iran, 2003 M. Sc., Photonics, Shahid Beheshti University, Tehran, Iran, 2006 M.S., Optical Science Engineering, University of New Mexico, Albuquerque, USA, 2012 DISSERTATION Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy Engineering The University of New Mexico Albuquerque, New Mexico December, 2017 ii ©2017, Mohsen Nami iii Dedication To my parents, my wife, and my daughter for their endless love, support, and encouragement. -

Nanowire Sensors for Medicine and the Life Sciences

For reprint orders, please contact: EVIEW [email protected] R Nanowire sensors for medicine and the life sciences Fernando Patolsky, The interface between nanosystems and biosystems is emerging as one of the broadest and Gengfeng Zheng & most dynamic areas of science and technology, bringing together biology, chemistry, Charles M Lieber† physics and many areas of engineering, biotechnology and medicine. The combination of †Author for correspondence Harvard University, these diverse areas of research promises to yield revolutionary advances in healthcare, Department of Chemistry and medicine and the life sciences through, for example, the creation of new and powerful Chemical Biology, and tools that enable direct, sensitive and rapid analysis of biological and chemical species, Division of Engineering and Applied Sciences, 12 Oxford ranging from the diagnosis and treatment of disease to the discovery and screening of new Street, Cambridge, drug molecules. Devices based on nanowires are emerging as a powerful and general MA 02138, USA platform for ultrasensitive, direct electrical detection of biological and chemical species. Tel.: +1 617 496 3169; Here, representative examples where these new sensors have been used for detection of a Fax: +1 617 496 5442; E-mail: cml@ wide-range of biological and chemical species, from proteins and DNA to drug molecules cmliris.harvard.edu and viruses, down to the ultimate level of a single molecule, are discussed. Moreover, how advances in the integration of nanoelectronic devices enable multiplexed -

Pros and Cons of Nanowire Fabrication Techniques for Sensor Arrays

NANOFUNCTION Beyond CMOS Nanodevices for Adding Functionalities to CMOS Network of Excellence Nanosensing with Si based nanowires Deliverable D1.1: Pros and cons of nanowire fabrication techniques for sensor arrays Main Author(s): T. Baron, P.-E. Hellström, L. Latu-Romain, M. Mongillo, L. Montès, M. Mouis,L. Poupinet, J.-P. Raskin, B. Salem and M. Schmidt. Due date of deliverable: 31 August 2011 Actual submission date: 1 September 2011 Project funded by the European Commission under grant agreement n°257375 NANOFUNCTION D1.1 Date of submission: 01/09/2011 NANOFUNCTION D1.1 Date of submission: 01/09/2011 LIST OF CONTRIBUTORS Part. Nr. Acronym Organisation name Name of contact 2 INP Grenoble Institute Polytechnique de Grenoble M. Mouis 5 KTH Kungliga Tekniska Hoegskolan P.-E. Hellström 8 UCL Université catholique de Louvain J.-P. Raskin 14 AMO-GMBH Gesellschaft fuer angewandte mikro- M. Schmidt und optoelektronik mit beschrankter haftung 15 CEA Commissariat à l‟Energie Atomique L. Poupinet 3 NANOFUNCTION D1.1 Date of submission: 01/09/2011 TABLE OF CONTENTS Deliverable summary ............................................................................................................. 5 1. Introduction .................................................................................................................... 6 2. Fabrication techniques ................................................................................................... 6 2.1 Bottom-up fabrication ............................................................................................. -

Silver Nanowire Purification and Separation by Size and Shape Using Multi-Pass Filtration

This is a repository copy of Silver nanowire purification and separation by size and shape using multi-pass filtration. White Rose Research Online URL for this paper: http://eprints.whiterose.ac.uk/89569/ Version: Accepted Version Article: Jarrett, R and Crook, R (2016) Silver nanowire purification and separation by size and shape using multi-pass filtration. Materials Research Innovations, 20 (2). pp. 86-91. ISSN 1432-8917 https://doi.org/10.1179/1433075X15Y.0000000016 Reuse Unless indicated otherwise, fulltext items are protected by copyright with all rights reserved. The copyright exception in section 29 of the Copyright, Designs and Patents Act 1988 allows the making of a single copy solely for the purpose of non-commercial research or private study within the limits of fair dealing. The publisher or other rights-holder may allow further reproduction and re-use of this version - refer to the White Rose Research Online record for this item. Where records identify the publisher as the copyright holder, users can verify any specific terms of use on the publisher’s website. Takedown If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing [email protected] including the URL of the record and the reason for the withdrawal request. [email protected] https://eprints.whiterose.ac.uk/ Silver nanowire purification and separation by size and shape using multi-pass filtration. R. Jarretta*, R. Crooka a: Energy Research Institute, University of Leeds, Leeds, LS2 9JT. *Corresponding author: [email protected], +447860850687 Abstract Silver Nanowire (AgNW) meshes produced by soft solution polyol synthesis offer a low-cost low-temperature solution deposited alternative to indium tin oxide transparent conductors for use in solar cells. -

Recent Advances in Vertically Aligned Nanowires for Photonics Applications

micromachines Review Recent Advances in Vertically Aligned Nanowires for Photonics Applications Sehui Chang, Gil Ju Lee and Young Min Song * School of Electrical Engineering and Computer Science, Gwangju Institute of Science and Technology (GIST), 123 Cheomdangwagi-ro, Buk-gu, Gwangju 61005, Korea; [email protected] (S.C.); [email protected] (G.J.L.) * Correspondence: [email protected]; Tel.: +82-62-715-2655 Received: 29 June 2020; Accepted: 25 July 2020; Published: 26 July 2020 Abstract: Over the past few decades, nanowires have arisen as a centerpiece in various fields of application from electronics to photonics, and, recently, even in bio-devices. Vertically aligned nanowires are a particularly decent example of commercially manufacturable nanostructures with regard to its packing fraction and matured fabrication techniques, which is promising for mass-production and low fabrication cost. Here, we track recent advances in vertically aligned nanowires focused in the area of photonics applications. Begin with the core optical properties in nanowires, this review mainly highlights the photonics applications such as light-emitting diodes, lasers, spectral filters, structural coloration and artificial retina using vertically aligned nanowires with the essential fabrication methods based on top-down and bottom-up approaches. Finally, the remaining challenges will be briefly discussed to provide future directions. Keywords: nanowires; photonics; LED; nanowire laser; spectral filter; coloration; artificial retina 1. Introduction In recent years, nanowires originated from a wide variety of materials have arisen as a centerpiece for optoelectronic applications such as sensors, solar cells, optical filters, displays, light-emitting diodes and photodetectors [1–12]. Tractable but outstanding, optical features of nanowire arrays achieved by modulating its physical properties (e.g., diameter, height and pitch) allow to confine and absorb the incident light considerably, albeit its compact configuration. -

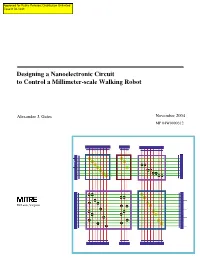

Designing a Nanoelectronic Circuit to Control a Millimeter-Scale Walking Robot

Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 McLean, Virginia Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 MITRE Nanosystems Group e-mail: [email protected] WWW: http://www.mitre.org/tech/nanotech Sponsor MITRE MSR Program Project No. 51MSR89G Dept. W809 Approved for public release; distribution unlimited. Copyright © 2004 by The MITRE Corporation. All rights reserved. Gates, Alexander Abstract A novel nanoelectronic digital logic circuit was designed to control a millimeter-scale walking robot using a nanowire circuit architecture. This nanoelectronic circuit has a number of benefits, including extremely small size and relatively low power consumption. These make it ideal for controlling microelectromechnical systems (MEMS), such as a millirobot. Simulations were performed using a SPICE circuit simulator, and unique device models were constructed in this research to assess the function and integrity of the nanoelectronic circuit’s output. It was determined that the output signals predicted for the nanocircuit by these simulations meet the requirements of the design, although there was a minor signal stability issue. A proposal is made to ameliorate this potential problem. Based on this proposal and the results of the simulations, the nanoelectronic circuit designed in this research could be used to begin to address the broader issue of further miniaturizing circuit-micromachine systems. i Gates, Alexander I. Introduction The purpose of this paper is to describe the novel nanoelectronic digital logic circuit shown in Figure 1, which has been designed by this author to control a millimeter-scale walking robot. -

Room Temperature Gas Nanosensors Based on Individual and Multiple

Room temperature gas nanosensors based on individual and multiple networked Au-modified ZnO nanowires Oleg Lupan, Vasile Postica, Thierry Pauporté, Bruno Viana, Maik-Ivo Terasa, Rainer Adelung To cite this version: Oleg Lupan, Vasile Postica, Thierry Pauporté, Bruno Viana, Maik-Ivo Terasa, et al.. Room tem- perature gas nanosensors based on individual and multiple networked Au-modified ZnO nanowires. Sensors and Actuators B: Chemical, Elsevier, 2019, 299, 10.1016/j.snb.2019.126977. hal-02999566 HAL Id: hal-02999566 https://hal.archives-ouvertes.fr/hal-02999566 Submitted on 10 Nov 2020 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Please cite this article as: Oleg Lupan,1,2,3,* Vasile Postica,2 Thierry Pauporté,3 Bruno Viana,3 Maik-Ivo Terasa,1 Rainer Adelung,1 Room temperature gas nanosensors based on individual and multiple networked Au-modified ZnO nanowires. Sensors & Actuators: B. Chemical 299 (2019) 126977 DOI: 10.1016/j.snb.2019.126977 1 Functional Nanomaterials, Faculty of Engineering, Institute for Materials Science, Kiel University, Kaiserstr. 2, D-24143, Kiel, Germany 2 Center for Nanotechnology and Nanosensors, Department of Microelectronics and Biomedical Engineering, Technical University of Moldova, 168 Stefan cel Mare Av., MD-2004 Chisinau, Republic of Moldova 3 PSL Université, Institut de Recherche de Chimie Paris, ChimieParisTech, UMR CNRS 8247, 11 rue Pierre et Marie Curie 75231 Paris cedex 05, France *Corresponding authors Prof. -

Kinetic Monte Carlo Model of Breakup of Nanowires Into Chains of Nanoparticles

Kinetic Monte Carlo Model of Breakup of Nanowires into Chains of Nanoparticles Vyacheslav Gorshkova and Vladimir Privmanb,* a National Technical University of Ukraine “Igor Sikorsky Kyiv Polytechnic Institute”, Kyiv 03056, Ukraine b Department of Physics, Clarkson University, Potsdam, NY 13699, USA * [email protected] J. Appl. Phys. 122 (20), Article 204301, 10 pages (2017) DOI link http://doi.org/10.1063/1.5002665 ABSTRACT A kinetic Monte Carlo approach is applied to studying shape instability of nanowires that results in their breaking up into chains of nanoparticles. Our approach can be used to explore dynamical features of the process that correspond to experimental findings, but that cannot be interpreted by continuum mechanisms reminiscent of the description of the Plateau-Rayleigh instability in liquid jets. For example, we observe long-lived dumbbell-type fragments and other typical non-liquid-jet characteristics of the process, as well as confirm the observed lattice- orientation dependence of the breakup process of single-crystal nanowires. We provide snapshots of the process dynamics, and elaborate on the nanowire-end effects, as well as on the morphology of the resulting nanoparticles. KEYWORDS nanowire; nanoparticle; shape instability; surface diffusion; kinetic Monte Carlo - 1 - 1. INTRODUCTION In synthesis of nanoparticles and nanostructures, stability of the products in rather important in many applications. Therefore, breakup of nanowires at temperatures below melting into small fragments that are typically isomeric (even-proportioned) nanoparticles, has recently attracted substantial interest. Experimental1-9 and theoretical10-13 works have been published studying this phenomenon, and it has also been argued that the resulting nanoparticle chains can find their own applications, such as in design of optical waveguides.1 It is tempting to associate this process with Plateau-Rayleigh instability14,15 that spontaneously develops in liquid jets. -

Highly Sensitive and Selective Hydrogen Single-Nanowire Nanosensor

Sensors and Actuators B 173 (2012) 772–780 Contents lists available at SciVerse ScienceDirect Sensors and Actuators B: Chemical j ournal homepage: www.elsevier.com/locate/snb Highly sensitive and selective hydrogen single-nanowire nanosensor a,b,c,∗ a,∗∗ b a a a O. Lupan ,L.Chow , Th. Pauporté , L.K. Ono , B. Roldan Cuenya , G. Chai a Department of Physics, University of Central Florida, Orlando, FL 32816-2385, USA b Chimie-Paristech, Laboratoire d’Électrochimie, Chimie des Interfaces et Modélisation pour l’Énergie (LECIME), UMR-CNRS 7575, 11 rue P. et M. Curie, 75231, Paris, cedex 05, France c Department of Microelectronics and Semiconductor Devices, Technical University of Moldova, 168 Stefan cel Mare Blvd., Chisinau MD-2004, Republic of Moldova a r t i c l e i n f o a b s t r a c t Article history: Metal oxides such as ZnO have been used as hydrogen sensors for a number of years. Through doping, Received 12 April 2012 the gas response of zinc oxide to hydrogen has been improved. Cadmium-doped ZnO nanowires (NWs) Received in revised form 25 July 2012 with high aspect ratio have been grown by electrodeposition. Single doped ZnO NWs have been iso- Accepted 28 July 2012 lated and contacted to form a nanodevice. Such nanosystem demonstrates an enhanced gas response Available online 3 August 2012 and selectivity for the detection of hydrogen at room temperature compared to previously reported H2 nanosensors based on pure single-ZnO NWs or multiple NWs. A dependence of the gas response of a single PACS: Cd–ZnO nanowire on the NW diameter and Cd content was observed. -

Polymeric Nanowires for Diagnostic Applications

micromachines Review Polymeric Nanowires for Diagnostic Applications Hendrik Hubbe , Eduardo Mendes and Pouyan E. Boukany * Department of Chemical Engineering, Delft University of Technology, Van der Maasweg 9, 2629HZ Delft, The Netherlands; [email protected] (H.H.); [email protected] (E.M.) * Correspondence: [email protected]; Tel.: +31-15-278-9981 Received: 26 December 2018; Accepted: 15 March 2019; Published: 29 March 2019 Abstract: Polymer nanowire-related research has shown considerable progress over the last decade. The wide variety of materials and the multitude of well-established chemical modifications have made polymer nanowires interesting as a functional part of a diagnostic biosensing device. This review provides an overview of relevant publications addressing the needs for a nanowire-based sensor for biomolecules. Working our way towards the detection methods itself, we review different nanowire fabrication methods and materials. Especially for an electrical signal read-out, the nanowire should persist in a single-wire configuration with well-defined positioning. Thus, the possibility of the alignment of nanowires is discussed. While some fabrication methods immanently yield an aligned single wire, other methods result in disordered structures and have to be manipulated into the desired configuration. Keywords: Affordable biosensor; polymeric nanowire; bio-microfluidics; biosensor; bioelectronics; bio-diagnostics 1. Introduction One-dimensional nanostructured materials, namely nanowires, have a strong potential to provide a valuable platform for sensing of biomolecules and pathogens when integrated in affordable devices. To date, the search for one-dimensional nanostructures of high quality materials with control of the diameter, length, composition, and phase has enabled some strong advances with their incorporation as functional parts of integrated devices [1–5]. -

Site-Specific Magnetic Assembly of Nanowires for Sensor Arrays Fabrication 253

IEEE TRANSACTIONS ON NANOTECHNOLOGY, VOL. 7, NO. 3, MAY 2008 251 Site-Specific Magnetic Assembly of Nanowires for Sensor Arrays Fabrication Youngwoo Rheem, Carlos M. Hangarter, Eui-Hyeok (EH) Yang, Senior Member, IEEE, Deok-Yong Park, Nosang V. Myung, and Bongyoung Yoo Abstract—The effect of variation in local magnetic field on heterostructures for segmented, superlattice, and core/shell con- magnetic assembly of 30 and 200 nm diameter Ni nanowires figurations. These features may also enable a high enough sen- synthesized by template directed electrodeposition was investi- sitivity to realize single molecule detection in chemical and gated with different materials (Ni–Ni and Ni–Au) and shapes of electrodes. Ni–Au paired electrodes improved confinement of the biological sensors [2], [3]. assembled Ni nanowires across the electrode gap because of the Various 1-D nanostructures have been synthesized using dif- narrower distribution of magnetic field around the gap between ferent processes, including chemical vapor deposition (CVD), the two electrodes. Simulation results indicated a local magnetic high-temperature catalytic processes, pulse-laser ablation, field strength at the electrode tip increased by a factor of 2.5 with vapor–solid–liquid (VLS) growth processes, molecular beam the use of a needle-shape electrode as compared to rectangular- shape electrode. The resistance of nanowire interconnects epitaxy (MBE), and wet-chemical synthesis [4]. As increasing increased as the applied voltage was raised, and under the same emphasis is placed on nanomanufacturing (i.e., high volume, applied voltage, the increase in resistance is further enhanced at low cost, high throughput, and low capital cost), template lower temperatures because of higher current density. -

The Burgeoning Field of Nanotechnology Has Arisen from An

1 Chapter 1 Thesis overview 1.1 Nanotechnology and nanoelectronics The rapidly expanding fields of nanoscience and nanotechnology are within the midst of an extraordinary period of scientific and technological productivity, due in no small part to the unprecedented collaboration of researchers from across the physical, chemical, biological, and life sciences. The promise of functional systems at the nanometer (nm) length scale (1–100 nm) has spurred researchers in diverse disciplines to engage in fruitful collaborations across traditional academic boundaries and between academia, industry, and government1. The result has been a modern-day scientific renaissance as the talents of chemists, physicists, biologists and engineers are simultaneously leveraged to understand and exploit novel phenomena and functionality particular to the nanometer size regime. Emerging applications of nanotechnology range from ultra-dense information storage2 to sustainable water purification3, to in-vivo biological sensors and intelligent drug delivery systems4, to ‘smart materials’ capable of sensing changes to their external environment and responding accordingly5. An exciting sub-field of nanotechnology is nanoelectronics and, in particular, molecular electronics6. Interest in this field has been fueled by the realization that the 2 technologies and materials systems currently in use by the semiconductor microelectronics industry cannot sustain the forty-year-old trend of device miniaturization into the coming decades. Indeed, the microelectronics industry had to overcome significant technical barriers to achieve the sub-100-nanometer dimensions of today’s transistors, and such barriers are becoming increasingly numerous and more difficult to overcome as device dimensions continue to shrink. This is highlighted by a recent assessment7 of the technology requirements for future generations of integrated circuits, which forewarns the emergence of insurmountable technical barriers (either physical or economical) by as early as the year 2010.