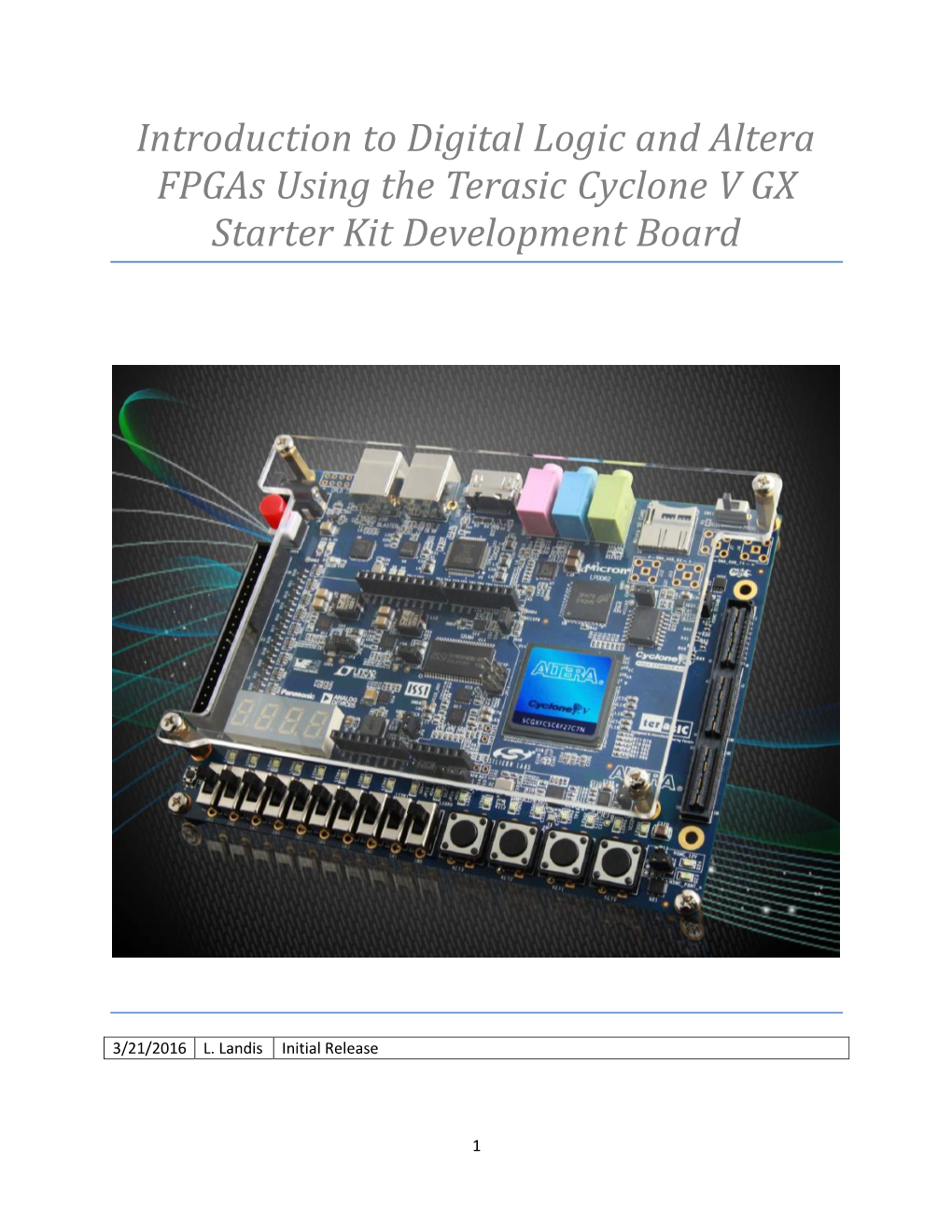

Introduction to Digital Logic and Altera Fpgas Using the Terasic Cyclone V GX Starter Kit Development Board

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Everi Games' Display at 2017 Global Gaming Expo to Feature

NEWS RELEASE Everi Games’ Display at 2017 Global Gaming Expo to Feature Company’s Most Expansive Portfolio of New Hardware Platforms, Game Content and Game Features 9/28/2017 G2E Highlights Include Debut of All-New Empire 5527 Premium Cabinet; Expanded Portfolio of Licensed Content with New Themes such as The Brady Bunch, Willie Nelson, Buffy The Vampire Slayer, Knight Rider, Singin’ in the Rain and Discovery Channel’s Shark Week Company to Celebrate Blockbuster Finale of 6th Annual TournEvent of Champions LAS VEGAS, Sept. 28, 2017 (GLOBE NEWSWIRE) -- Everi Holdings Inc. (NYSE:EVRI) (“Everi” or the “Company”), will demonstrate its position as the only gaming technology provider that can deliver a comprehensive portfolio of gaming entertainment and payments solutions to help casino operators deliver a winning experience for their players at the 17th annual Global Gaming Expo (G2E®), to be held at the Sands Expo and Convention Center (Booth #1116) in Las Vegas, Nevada from October 3-5. Alongside a deep lineup of new, innovative Payments solutions, Everi Games will display the most diverse set of gaming entertainment products in its history, including more than 90 unique game themes and seven new licensed titles, new hardware and game innovations, an exciting upgrade for the award-winning TournEvent® slot tournament solution and, for the sixth consecutive year, the thrilling conclusion to the 2017 TournEvent of Champions®. Michael Rumbolz, President and Chief Executive Officer of Everi, commented, “By leveraging our growing talent base and customer-centric development strategy, the Games team’s expertise and focus continues to establish Everi as a leading full-service gaming equipment provider. -

With Mattel at 2012 San Diego Comic-Con Booth #3029

July 11, 2012 Fanboys and Fangirls "Collect and Connect®" with Mattel at 2012 San Diego Comic-Con Booth #3029 Immersive Fan Panels, Hot Toy Exclusives and Celebratory Events Round out Confab Collector Experience SAN DIEGO--(BUSINESS WIRE)-- Mattel, Inc. (NASDAQ:MAT) brings San Diego Comic-Con (SDCC) fans the ultimate pop- culture, comic inspired celebration with exclusive toy collectibles, giveaways and fan-atic events at booth #3029. From the hottest classic brands to new entertainment collectibles, Mattel has something for every fanboy and fangirl. "This year heralds significant milestones for Mattel as we commemorate our decade long presence at SDCC creating unique show exclusives. We take great pride in bringing forth the very best in detailed collectibles and fan events by utilizing our timeless brands," said Doug Wadleigh, Senior Vice President, Global Brands Marketing, Mattel. "We also look forward to celebrating the 30th anniversary of our iconic action hero brand, Masters of the Universe at the show." A "Masterful" 30 Year Legacy: What began as an "Eternian" action-hero property in the 1980s, Masters of the Universe® (MOTU), has grown into a robust Mattel, Inc. San Diego Comic-Con Masters of the Universe(R) Classics Vykron(TM) franchise that has spanned three-decades. Ultimate Eternian Champion(TM) (Photo: Business Wire) The MOTU brand has had six lines of action figures, four animated television series, several comic series and a feature film all of which have received fanfare around the world. SDCC patrons can ring in the MOTU anniversary at the Mattypalooza panel on Friday, July 13th with several top-secret reveals and an in-depth discussion on all things MOTU. -

CURRICULUM VITAE January, 2012

PHILIP J. TAYLOR 7451 E. VISAO DRIVE, SCOTTSDALE, AZ 85266-2747 phone 480.575.9513 fax 480.575.9516 [email protected] CURRICULUM VITAE January, 2012 CAREER SUMMARY Broad and diverse background of teaching at prominent universities. A seasoned television writer/producer of network, cable and syndicated product, both series and movies. In-depth experience in all aspects of television production the creative process, casting and personnel selection, budgeting, supervision, negotiating, new media technologies, and the crucible of down-to-the-wire spontaneity. 100 produced television and feature scripts, including a Writers Guild of America Award nomination. Extensive experience in many facets of Theatre, including acting and/or directing assignments with many world class theatre companies. EDUCATION Royal Academy of Dramatic Art, London, England 1964-1966 Honors Graduate, 1966 Rose Bruford College of Speech and Drama, Sidcup, Kent, England 1963 Oxford University General Certificate of Education, Scholarship Level Chemistry, Physics, Pure Mathematics, 1962 Oxford University General Certificate of Education, Ordinary Level Chemistry, Comparative Religion, English, English Literature, French, Geography, History, Latin, Mathematics, Physics – Highest grades in County of Devonshire, 1960 Tiverton Grammar School, Tiverton, Devon, England 1955-1962 AWARDS Writers Guild of America Best Comedy nominee, 1980 Mork and Mindy Royal Academy of Dramatic Art Best Actor, 1966 Poetry Society of Great Britain Winner, Best Recital, 1965 PHILIP TAYLOR/2 AFFILIATIONS -

ISBN: 978-1-63140-311-8 18 17 16 15 1 2 3 4 Ted Adams, CEO & Publisher Facebook: Facebook.Com/Idwpublishing Greg Goldstein, President & COO Robbie Robbins, EVP/Sr

$14.99 • www.idwpublishing.com ISBN: 978-1-63140-311-8 18 17 16 15 1 2 3 4 Ted Adams, CEO & Publisher Facebook: facebook.com/idwpublishing Greg Goldstein, President & COO Robbie Robbins, EVP/Sr. Graphic Artist Twitter: @idwpublishing Chris Ryall, Chief Creative Officer/Editor-in-Chief YouTube: youtube.com/idwpublishing Matthew Ruzicka, CPA, Chief Financial Officer Alan Payne, VP of Sales Instagram: instagram.com/idwpublishing Dirk Wood, VP of Marketing deviantART: idwpublishing.deviantart.com www.IDWPUBLISHING.com Lorelei Bunjes, VP of Digital Services IDW founded by Ted Adams, Alex Garner, Kris Oprisko, and Robbie Robbins Jeff Webber, VP of Digital Publishing & Business Development Pinterest: pinterest.com/idwpublishing/idw-staff-faves KNIGHT RIDER, VOLUME 1, published May, 2015 by The Lion Forge, LLC. First printing. KNIGHT RIDER is a trademark and copyright of Universal Studios. Licensed by NBC Universal Television Consumer Products Group 2015. All Rights Reserved. LION FORGE™ and the associated distinctive designs are trademarks of The Lion Forge, LLC (www.lionforge.com). No similarity between any of the names, characters, persons, and/or institutions in this issue with those of any living or dead person or institution is intended and any such similarity which may exist is purely coincidental. IDW Publishing, a division of Idea and Design Works, LLC. Editorial offices: 5080 Santa Fe St., San Diego, CA 92109. IDW Publishing does not read or accept unsolicited submissions of ideas, stories, or artwork. The IDW logo is registered in the U.S. Patent and Trademark Office. Printed in Korea. Originally published digitally by Lion Forge Comics as KNIGHT RIDER issues #1–8. -

Dag Kittlaus -- Software Visionary…And Storm Chaser by Rick A

THE TM 911 Franklin Street Weekly Newspaper Michigan City, IN 46360 Volume 28, Number 19 Thursday, May 17, 2012 Dag Kittlaus -- Software Visionary…and Storm Chaser by Rick A. Richards Dag Kittlaus and his mother, Liv Markle of Michigan City. (Photo by Rick A. Richards) Software visionary Dag Kittlaus, the man who When Siri was acquired by Apple in one of Steve was instrumental in creating the iPhone app Siri, Jobs’ last acquisitions before he died, Kittlaus found didn’t hesitate when asked what he would do if he himself thrust into the public eye. It was a place he wasn’t designing software for the future. wasn’t entirely comfortable. “A storm chaser,” he said. “I love the weather.” “I grew up in Duneland Beach and we spent a And so he does. He showed off weather app he lot of time on the beach sailing,” said Kittlaus. “My developed for his iPhone that gives him real time brothers (Erik and Aaron) and I were on the tennis weather information on the conditions at his Bar- team. There’s a lot to like about living in Michigan rington, Ill., home. City.” Kittlaus, a 1985 graduate of Elston High School Kittlaus was the guest speaker for the 2012 Busi- in Michigan City, is quiet and soft spoken. He looks a ness Investment and Anniversary Awards Celebra- decade younger than his 45 years. When he speaks, tion hosted by the Michigan City Economic Devel- he makes sure he’s unambiguous. opment Corp. at Blue Chip Casino on April 25. Part of it may be because of some uncomfortable “Before I came here today,” said Kittlaus, “I had dealings with the media following Siri’s acquisition lunch at Redamak’s.” With that, a smile crossed by Apple. -

Rev Your Engines for This Quiz

The Post and Courier Thursday, May 28, 2020: D7 HEAD2HEADTRIVIA Questions 6. A 1958 Plymouth Fury 1. What type of car was used served as what possessed, killer as the time machine in the car in a 1983 movie that was “Back to the Future” franchise? adapted from a Stephen King 2. Ian Fleming, best known for novel? creating the character James 7. One of the most famous Bond, delved into children’s TV cars of all time is the orange fiction with what 1964 novel Dodge Charger known as The about a magical car? General Lee from “The Dukes 3. What was the name of the of Hazzard.” What country artificially intelligent, crime singer performed a song for fighting car that was “driven” by “The Dukes of Hazzard” TV David Hasselhoff on the 1980’s soundtrack that was sung from TV series “Knight Rider”? the perspective of the car? 4. What famous fictional car 8. What character from the made its debut in a 1969 live- 1960’s racing cartoon “Wacky action Disney movie? In the Races” drove a vehicle known as movie the car is given its now The Compact Pussycat and was world famous name by Buddy referred to as “The Glamour Gal Hackett’s character, who names of the Gas Pedal”? it after his middleweight boxer 9. In what animated 1960’s TV uncle whose nose began to show will you see a high tech look more and more like a Volk- car called The Mach 5? swagen Beetle over the course 10. According to the song, of his fighting career. -

Knight Rider K.I.T.T

KNIGHT RIDER K.I.T.T. the "Knight Industries Two Thousand" and his driver Michael Knight are back to battle the forces of evil on behalf of the Foundation of Law and Constitution. Catch gangsters successfully and you will have the possibility to drive into the F.L.A.G. Mobile Unit to get new sophistications like the Turbo Boost or accelerate your speed with the Super Pursuit Mode which will allow you to fight more efficiently against injustice. But be careful - you have to be aware of your greatest enemy - K.A.R.R. Knight Rider GAME CONTROLS KNIGHT RIDER is designed to be played with the built-in control panel only. The functions of the controls are: Button 1 Button 2 Joystick Action Turbo Boost Steer K.I.T.T. to left or right Activate action mode Evade K.A.R.R. with and step on the gas to catch gangsters the Turbo Boost HOW TO PLAY PLAYER SELECTION Knight Rider is a single-player game. OPTION SELECTION You can´t choose options as you have to catch gangsters successfully to get feature upgrades like the Turbo Boost and the Super Pursuit Mode. So you have to try hard to reach the next step to a full-featured Knight Industries Two Thousand. GAME PLAY Catch gangsters successfully and be aware of your biggest enemy – K.A.R.R. the prototype version of K.I.T.T. POWER UP You have the chance to drive into the F.L.A.G. Mobile Unit to get the Turbo Boost and the Super Pursuit Mode. -

There I Go Again William Daniels

University of Nebraska - Lincoln DigitalCommons@University of Nebraska - Lincoln University of Nebraska Press -- Sample Books and University of Nebraska Press Chapters 2017 There I Go Again William Daniels Follow this and additional works at: http://digitalcommons.unl.edu/unpresssamples Daniels, William, "There I Go Again" (2017). University of Nebraska Press -- Sample Books and Chapters. 374. http://digitalcommons.unl.edu/unpresssamples/374 This Article is brought to you for free and open access by the University of Nebraska Press at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in University of Nebraska Press -- Sample Books and Chapters by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln. T H E R E I G O AG A I N Buy the Book Buy the Book WILLIAM DANIELS There I Go Again | How I Came to Be Mr. Feeny, John Adams, Dr. Craig, KITT, and Many Others Potomac Books AN IMPRINT OF THE UNIVERSITY OF NEBRASKA PRESS Buy the Book © 2017 by William Daniels “The Legacy of 1776” was originally published in March 2016 in New York City Center’s Playbill and is reprinted courtesy of Playbill. All rights reserved. Potomac Books is an imprint of the University of Nebraska Press. Manufactured in the United States of America. Library of Congress Cataloging- in- Publication Data Names: Daniels, William, 1927– author. Title: There I go again: how I came to be Mr. Feeny, John Adams, Dr. Craig, Kitt, and many others / William Daniels. Description: Lincoln: Potomac Books, 2017. Identifiers: LCCN 2016035738 ISBN 9781612348520 (cloth: alk. paper) ISBN 9781612349022 (epub) ISBN 9781612349039 (mobi) ISBN 9781612349046 (pdf) Subjects: LCSH: Daniels, William, 1927– | Actors— United States— Biography. -

Knight Rider 2008 the Complete Series Dvd

Knight rider 2008 the complete series dvd Knight Rider - The Complete Series DVD Knight Rider - Season Four DVD From to ; Knight Rider - Legacy; Knight Rider Commentary With. : Knight Rider: The Complete Series: David Hasselhoff, Edward Home Entertainment; DVD Release Date: October 21, ; Run Time: Find great deals on eBay for Knight Rider DVD in DVDs and Movies for DVD and Blu-ray Disc Knight Rider - The Complete Series (DVD, , Disc Set). Find great deals for Knight Rider - The Complete Series (DVD, , Disc Set). Shop with confidence on eBay! Knight Rider - The Complete Box Set ( Repackage) [DVD] [] DVD Episodes comprise; 'Knight Rider Feature Length Pilot', 'A Knight in Shining. Shop Knight Rider - The Complete Box Set [DVD]. Everyday low prices and Synopsis. Contains all four series of the hugely popular '80s show Knight Rider. Back in , Universal Studios first released Knight Rider - The Complete Series on DVD in a gift set which has been discontinued. Now Mill. The Series: In a young man named Michael Knight (played by a big Reviews» DVD Video Reviews» Knight Rider: The Complete Series. Knight Rider: The Complete Series. Universal // Unrated // October 21, Review: Knight Rider Series One DVD scripts had been requested by NBC, and by Oct 21st they had approved a full season order. Knight Rider: The Complete Series DVD was released on July 28, on a four disc set with bonus material. Highlights. Knight Rider-complete Series [dvd/16 Disc] (Mill Creek Entertainment). Read more. Video Release Date: Animated: Live- action. Episodes: 1. Knight Rider []: A Knight in Shining Armor (Season 1: Ep. -

Film and Television Projects Made in Texas (1910 – 2021) Page 1 of 36

Film and Television Projects Made in Texas (1910 – 2021) Page 1 of 36 PROJECT NAME TYPE PRODUCTION COMPANY PRODUCTION DATE(S) CITY/TOWN SHOT IN MAGNOLIA TABLE - SEASON 4 TV Series (Network/Cable/Digital) Blind Nil LLC 2021-06-14 – 2021-07-02 Valley Mills; Waco MAGNOLIA TABLE - SEASON 3 TV Series (Network/Cable/Digital) Blind Nil LLC 2021-04-06 – 2021-04-23 Valley Mills Austin; College Station; Fredericksburg; San QUEER EYE - SEASON 6 TV Series (Network/Cable/Digital) Netflix / LWT Enterprises 2021-03-22 – 2021-07-02 Antonio BBQ BRAWL - SEASON 3 TV Series (Network/Cable/Digital) Rock Shrimp Productions 2021-02-22 – 2021-04-02 Austin; Bee Cave; Buda; Cedar Park; Manor Bee Cave; Driftwood; Dripping Springs; BBQ BRAWL - SEASON 2 TV Series (Network/Cable/Digital) Rock Shrimp Productions 2021-02-22 – 2021-04-01 Fredericksburg; Luckenbach Highland Haven; South Padre Island; LAKEFRONT BARGAIN HUNT - SEASON 12 TV Series (Network/Cable/Digital) Magilla Entertainment 2021-01-27 – 2021-06-10 Surfside Beach Rebel 6 Films / TLG Motion FREE DEAD OR ALIVE Feature (Independent) Pictures 2021-01-24 – 2021-03-03 Alpine; Austin; Buda; Lajitas; Terlingua READY TO LOVE - SEASON 3 TV Series (Network/Cable/Digital) Light Snack Media, LLC 2021-01-20 – 2021-03-27 Houston MAGNOLIA TABLE - SEASON 2 TV Series (Network/Cable/Digital) Blind Nil LLC 2021-01-18 – 2021-01-28 Valley Mills VAN GO TV Series (Network/Cable/Digital) Rabbit Foot Studios 2020-11-17 – 2021-05-12 Austin Austin; Bartlett; Bastrop; Lockhart; WALKER - SEASON 1 TV Series (Network/Cable/Digital) CBS -

A Top 150 of Sci Fi (Horror and Fantasy) TV from IMDB. Sorted by Score (A Combination of Rating and Votes)

A Top 150 of Sci Fi (Horror and Fantasy) TV from IMDB. Sorted by Score (a combination of Rating and Votes) # Name Year Rating Votes Score 1 Firefly 2002 9.5 39,178 372,191.00 2 Battlestar Galactica (new) 2004 9.0 35,128 316,152.00 3 Lost 2004 8.7 33,481 291,284.70 4 Futurama 1999 9.2 30,597 281,492.40 5 X-Files 1993 9.0 27,823 250,407.00 6 Buffy the Vampire Slayer 1997 8.5 28,520 242,420.00 7 Smallville 2001 7.8 25,968 202,550.40 8 It 1990 6.8 26,523 180,356.40 9 Walking Dead 2010 9.2 19,140 176,088.00 10 Hercules 1997 6.8 23,000 156,400.00 11 Jericho 2006 8.2 16,411 134,570.20 12 Stargate SG-1 1997 8.6 15,439 132,775.40 13 Doctor Who (new) 2005 8.8 14,897 131,093.60 14 Star Trek: TNG 1987 8.8 13,964 122,883.20 15 Angel 1999 8.5 14,376 122,196.00 16 Supernatural 2005 9.0 13,124 118,116.00 17 Dead Like Me 2003 8.7 11,015 95,830.50 18 Carnivale 2003 9.0 9,940 89,460.00 19 Star Trek (org) 1966 8.6 10,402 89,457.20 20 Cowboy Bebop 1998 9.3 8,840 82,212.00 21 Lost Room 2006 8.3 9,500 78,850.00 22 Batman: TAS 1992 9.2 8,454 77,776.80 23 Star Trek: Voyager 1995 7.5 9,553 71,647.50 24 Twilight Zone (org) 1959 9.5 7,416 70,452.00 25 Third Rock from the Sun 1996 8.0 8,802 70,416.00 26 Life on Mars 2006 8.9 7,768 69,135.20 27 The 4400 2004 7.9 8,593 67,884.70 28 Star Trek: DS9 1993 8.1 8,357 67,691.70 29 Terminator: Sarah Conner Chron 2008 7.7 8,316 64,033.20 30 Babylon 5 1994 8.7 6,542 56,915.40 31 Farscape 1999 8.7 6,499 56,541.30 32 Red Dwarf 1988 9.0 6,257 56,313.00 33 Star Trek: Enterprise 2001 7.4 7,549 55,862.60 34 MST3K 1988 9.4 5,829 54,792.60 -

Knight Rider Movie 2008

Knight rider movie 2008 click here to download Knight Rider is a American made-for-television action film which was created to serve as a backdoor pilot for the new Knight Rider television series. Justin Bruening and Deanna Russo in Knight Rider: Knight Rider () Deanna put into in the movie Knight Rider () (TV), the new K.I.T.T. is a third. Photos. Knight Rider () Justin Bruening in Knight Rider () Knight Rider (TV Movie ) . Charles Graiman 13 episodes, Knight Rider () starred Justin Bruening as Michael Knight and Val Kilmer as On the heels of NBC's hit movie, the iconic s television classic comes. Knight Rider (): Season 1 . Despite an onscreen benediction from the Hoff himself, the two-hour pilot movie admittedly clunks a bit, with a few too many. Rent Knight Rider () () starring Justin Bruening and Deanna Russo on DVD and Blu-ray. Get unlimited DVD Movies & TV Shows delivered to your door . Knight Rider is a new movie which will continue the stories started in Knight Rider. However there is a new generation of characters. K.I.T.T.'s creator Charles . Everything you need to know about Knight Rider (). Articles. Trailers. Reviews. Images. Arrested Development's Copeland to Rev Up Knight Rider Movie. Sep 23, There are reasons for the existence of “Knight Rider” (7 p.m. Wednesday, WMAQ- Ch. 5). Reason 5: Network television is going the way of the film world, I like the original KR, but I am willing to give the series a shot. On the heels of NBC's hit movie, the iconic s television classic comes roaring back to life as a reinvented, updated and super-charged action series.