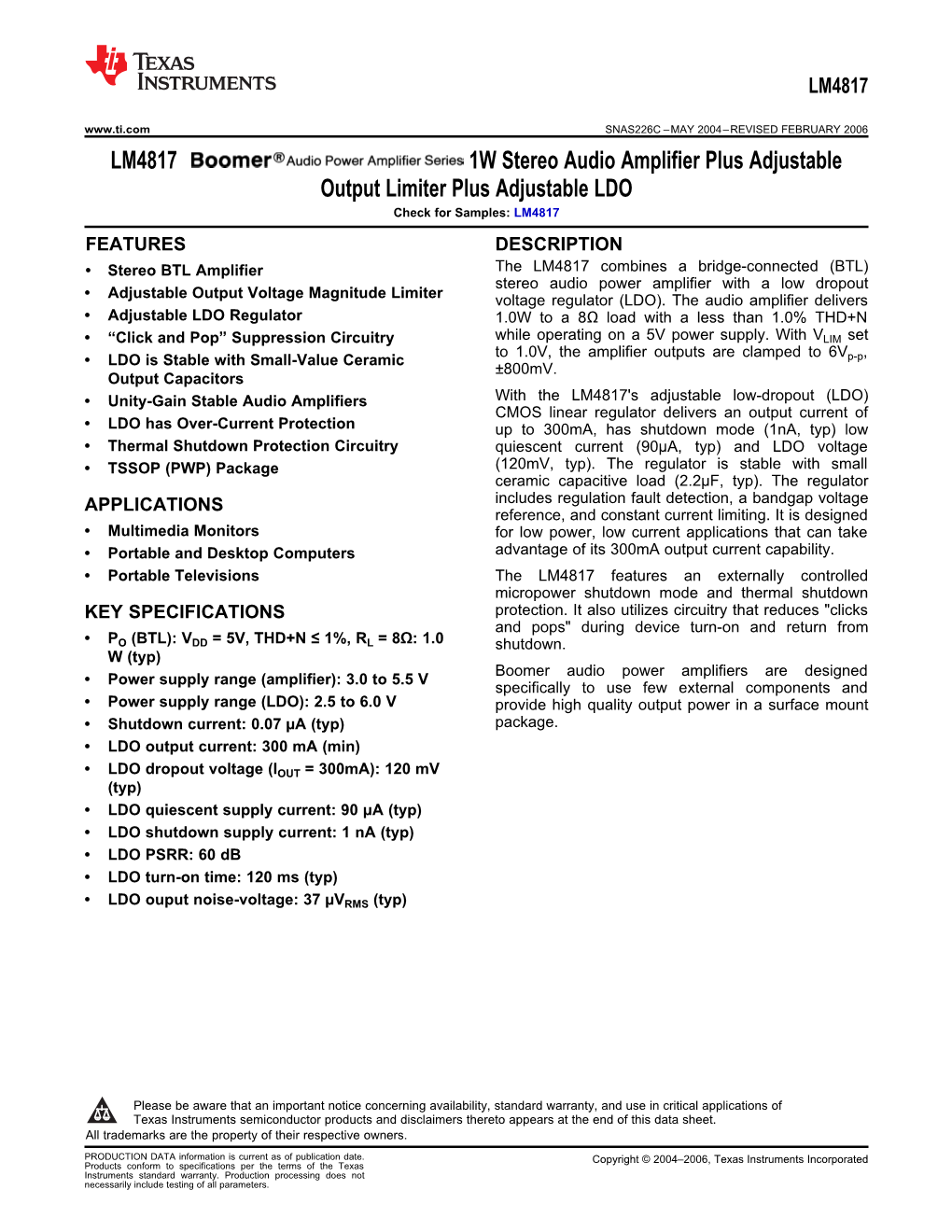

LM4817 1W Stereo Audio Amplifier Plus Adjustable Output Limiter Plus Adjustable LDO Check for Samples: LM4817

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Expert Podcasting Practices for Dummies (ISBN

01_149263 ffirs.qxp 10/25/07 9:07 PM Page iii Expert Podcasting Practices FOR DUMmIES‰ by Tee Morris, Evo Terra, and Ryan Williams 01_149263 ffirs.qxp 10/25/07 9:07 PM Page ii 01_149263 ffirs.qxp 10/25/07 9:07 PM Page i Expert Podcasting Practices FOR DUMmIES‰ 01_149263 ffirs.qxp 10/25/07 9:07 PM Page ii 01_149263 ffirs.qxp 10/25/07 9:07 PM Page iii Expert Podcasting Practices FOR DUMmIES‰ by Tee Morris, Evo Terra, and Ryan Williams 01_149263 ffirs.qxp 10/25/07 9:07 PM Page iv Expert Podcasting Practices For Dummies® Published by Wiley Publishing, Inc. 111 River Street Hoboken, NJ 07030-5774 www.wiley.com Copyright © 2008 by Wiley Publishing, Inc., Indianapolis, Indiana Published by Wiley Publishing, Inc., Indianapolis, Indiana Published simultaneously in Canada No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 646-8600. Requests to the Publisher for permission should be addressed to the Legal Department, Wiley Publishing, Inc., 10475 Crosspoint Blvd., Indianapolis, IN 46256, (317) 572-3447, fax (317) 572-4355, or online at http://www.wiley.com/go/permissions. Trademarks: Wiley, the Wiley Publishing logo, For Dummies, the Dummies Man logo, A Reference for the Rest of Us!, The Dummies Way, Dummies Daily, The Fun and Easy Way, Dummies.com, and related trade dress are trade- marks or registered trademarks of John Wiley & Sons, Inc. -

Compressor/Limiter

® 162SL Compressor/Limiter User Manual IMPORTANT SAFETY INSTRUCTIONS WARNING FOR YOUR PROTECTION CAUTION READ THE FOLLOWING: RISK OF ELECTRIC SHOCK DO NOT OPEN ATTENTION: RISQUE DE CHOC ELECTRIQUE - NE PAS OUVRIR KEEP THESE INSTRUCTIONS WARNING: TO REDUCE THE RISK OF FIRE OR ELECTRIC SHOCK DO NOT EXPOSE THIS EQUIPMENT TO RAIN OR MOISTURE HEED ALL WARNINGS The symbols shown above are internationally accepted FOLLOW ALL INSTRUCTIONS symbols that warn of potential hazards with electrical products. The lightning flash with arrowpoint in an equi- DO NOT USE THIS APPARATUS NEAR WATER lateral triangle means that there are dangerous voltages present within the unit. The exclamation point in an equi- CLEAN ONLY WITH A DRY CLOTH. lateral triangle indicates that it is necessary for the user to refer to the owner’s manual. DO NOT BLOCK ANY OF THE VENTILATION OPENINGS. INSTALL IN ACCORDANCE WITH THE MANUFACTURER’S INSTRUCTIONS. These symbols warn that there are no user serviceable parts inside the unit. Do not open the unit. Do not DO NOT INSTALL NEAR ANY HEAT SOURCES SUCH AS RADIATORS, HEAT REGISTERS, attempt to service the unit yourself. Refer all servicing to STOVES, OR OTHER APPARATUS (INCLUDING AMPLIFIERS) THAT PRODUCE HEAT. qualified personnel. Opening the chassis for any reason will void the manufacturer’s warranty. Do not get the unit ONLY USE ATTACHMENTS/ACCESSORIES SPECIFIED BY THE MANUFACTURER. wet. If liquid is spilled on the unit, shut it off immediately and take it to a dealer for service. Disconnect the unit UNPLUG THIS APPARATUS DURING LIGHTNING STORMS OR WHEN UNUSED FOR LONG during storms to prevent damage. -

Shure EMEA Brochure

INTEGRATED SYSTEMS FOR INSTALLED APPLICATIONS QUALITY, RELIABILITY, WIRED CONFERENCING SOLUTIONS AV CONFERENCING & COLLABORATION EXCELLENCE. When the microphone is on, quality and performance matter most. Whether it’s national leaders debating on the world stage, 6 8 12 14 panel members conversing across a room, or an AV conference CENTRAVERSE™ MICROFLEX® MICROFLEX® MICROFLEX® INSTALLED SOUND MICROPHONES WIRELESS SYSTEMS ADVANCE™ ARRAY that requires pristine speech intelligibility, the expectation is MICROPHONES MICROPHONES Audio simplicity, Unmatched flexibility Vivid, lifelike audio Intelligent networked flawless audio. realized and performance for conferencing microphones Since developing our first products in 1925, Shure has pursued PRESENTATION audio perfection with an uncompromising commitment to continuously innovating and improving product performance. That has meant countless hours of engineering, testing, re-tooling, and re-testing to ensure that the most important audio moments are captured effortlessly – whatever the environment. 18 18 19 20 24 BLX-R™ WIRELESS SLX® WIRELESS QLX-D® DIGITAL ULX-D™ DIGITAL AXIENT® DIGITAL SYSTEMS SYSTEMS WIRELESS SYSTEMS WIRELESS SYSTEMS WIRELESS SYSTEMS Wireless freedom made Smart, hard-working Secure digital wireless Uncompromising digital Accessible, scalable, simple wireless wireless, Dante-enabled powerful NETWORKED CONFERENCE AUDIO PROCESSING & DISCUSSION SOFTWARE 28 30 31 34 40 SIGNAL AUDIO NETWORK DIGITAL AUDIO CONFERENCE SOFTWARE PROCESSORS INTERFACES MIXERS AND DISCUSSION SOLUTIONS Perfectly -

Signature 10/12/12MTK User Guide

User Guide For Soundcraft Signature 10, 12 & 12MTK 10, 12, 12MTK User Manual INFORMATION INFORMATION IMPORTANT Please read this manual carefully before using your mixer for the first time. This equipment complies with the EMC directive 2004/108/EC and LVD 2006/95/EC. This product is approved to safety standards: IEC 60065:2005 (Seventh Edition) +A1:2005 EN60065:2006 +A1:2006 +A1:2008 UL60065 2012 7th Edition CAN/CSA-E60065-03 + A1: 2006 And EMC standards EN55103-1: 2009 (E2) EN55103-2: 2009 (E2) Warning: Any modification or changes made to this device, unless explicitly approved by Harman, will invalidate the authorisation of this device. Operation of an unauthorised device is prohibited under Section 302 of the Communications act of 1934, as amended, and Subpart 1 of Part 2 of Chapter 47 of the Code of Federal Regulations. NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures: * Reorient or relocate the receiving antenna. -

Learning to Mix with Neural Audio Effects in the Waveform Domain

Master thesis on Sound and Music Computing Universitat Pompeu Fabra Learning to mix with neural audio effects in the waveform domain Christian J. Steinmetz Supervisor: Joan Serrà Co-Supervisor: Frederic Font September 2020 Copyright © 2020 by Christian J. Steinmetz Licensed under Creative Commons Attribution 4.0 International Acknowledgements I would like to express my deepest gratitude to my supervisor, Joan Serrà, for provid- ing continuous encouragement and a belief in work. Throughout the process he has shared his extensive knowledge and provided invaluable guidance, all of which has had a significant impact in my development as a researcher. I am also grateful to my fellow collaborators, Jordi Pons and Santiago Pascual, whose expertise and insight greatly facilitated my investigations through our many discussions. This project was carried out over a six month period during my internship in the Barcelona office of Dolby Laboratories. This fruitful collaboration provided the resources, space, and collaborations necessary to successfully carry out my work. This project would not have been possible without the resources and support Dolby Laboratories provided. I am also greatly indebted to the Audio Engineering Society Education Foundation, who provided financial support, first in my undergraduate education, and now in collaboration with Genelec, through the Ilpo Martikainen Audio Visionary Schol- arship. This generous funding has played a major role in supporting my studies while completing my master at Universitat Pompeu Fabra. I want to also thank my fellow classmates in the Sound and Music Computing master at Universitat Pom- peu Fabra, for their collaboration and fruitful discussions in this shared endeavor throughout this process. -

Technology Review of Dynamic Range Compression

ASSIGNMENT 1: TECHNOLOGY REVIEW OF DYNAMIC RANGE COMPRESSION Chris Stedman 420066431 Digital Audio Systems, DESC9115, Semester 1 2012 Graduate Program in Audio and Acoustics Faculty of Architecture, Design and Planning, The University of Sydney ABSTRACT Compressors and limiters are audio hardware / software devices, which fall under the broader category of dynamics processors. In their various forms, they find use in all aspects of sound production and system engineering. They produce at their output a copy of the input with some level dependent gain attenuation applied. The user typically has some control over the amount of attenuation and the manner in which it is applied. This report will cover the various forms and uses of these devices, along with an investigation of the mathematical basis upon which one may emulate an analogue hardware compressor in a programming environment. 1. INTRODUCTION A compressor is used to reduce the dynamic range of some input signal. They work by inspecting the input signal for amplitude peaks above a user-defined point termed the THRESHOLD. These peaks are reduced by a user-defined Figure 1. The input/output behaviour of a compressor. RATIO. The gain ratio is applied for input above the threshold. For a given input signal x, the compressor output y is given by: The ratio may vary between 1:1 and infinity:1, with 2:1 illustrated as a typical case. For input below threshold: y(n) = x(n) (1) 2. COMPRESSORS IN USE For input above threshold: Compressors find use in all areas of live sound, recording, mastering, broadcast and system engineering. -

Restoring the Dynamics of Clipped Audio Material by Inversion of Dynamic Range Compression Stanislaw Gorlow, Joshua Reiss, Elodie Duru

Restoring the Dynamics of Clipped Audio Material by Inversion of Dynamic Range Compression Stanislaw Gorlow, Joshua Reiss, Elodie Duru To cite this version: Stanislaw Gorlow, Joshua Reiss, Elodie Duru. Restoring the Dynamics of Clipped Audio Material by Inversion of Dynamic Range Compression. 2014 IEEE International Symposium on Broadband Multimedia Systems and Broadcasting, Jun 2014, Pékin, China. pp.1. hal-01015633 HAL Id: hal-01015633 https://hal.archives-ouvertes.fr/hal-01015633 Submitted on 27 Jun 2014 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Restoring the Dynamics of Clipped Audio Material by Inversion of Dynamic Range Compression Stanislaw Gorlow Joshua D. Reiss Elodie Duru LaBRI, UMR 5800 C4DM, Queen Mary Aquitaine Science Transfert University of Bordeaux University of London 33600 Pessac, France 33400 Talence, France London E1 4NS, UK http://ast-innovations.com Abstract—In this work, a novel approach for the restoration there is the competition factor. The use of over- or hyper- of clipped audio alias declipping is presented. It is based on the compression to boost the apparent loudness is a popular trick inversion of a nonlinear dynamic system varying over time. -

Podcasting Second Edition

Podcast Solutions The Complete Guide to Audio and Video Podcasting Second Edition Michael W. Geoghegan and Dan Klass Podcast Solutions: The Complete Guide to Audio and Video Podcasting, Second Edition Copyright © 2007 by Michael W. Geoghegan and Dan Klass All rights reserved. No part of this work may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage or retrieval system, without the prior written permission of the copyright owner and the publisher. ISBN-13 (pbk): 978-1-59059-905-1 ISBN-10 (pbk): 1-59059-905-5 Printed and bound in the United States of America 9 8 7 6 5 4 3 2 1 Trademarked names may appear in this book. Rather than use a trademark symbol with every occurrence of a trademarked name, we use the names only in an editorial fashion and to the benefit of the trademark owner, with no intention of infringement of the trademark. Distributed to the book trade worldwide by Springer-Verlag New York, Inc., 233 Spring Street, 6th Floor, New York, NY 10013. Phone 1-800-SPRINGER, fax 201-348-4505, e-mail [email protected], or visit www.springeronline.com. For information on translations, please contact Apress directly at 2855 Telegraph Avenue, Suite 600, Berkeley, CA 94705. Phone 510-549-5930, fax 510-549-5939, e-mail [email protected], or visit www.apress.com. The information in this book is distributed on an “as is” basis, without warranty. Although every precaution has been taken in the preparation of this work, neither the author(s) nor Apress shall have any liability to any person or entity with respect to any loss or damage caused or alleged to be caused directly or indirectly by the information contained in this work. -

When Mastering Electronic Dance Music, Can Two Limiters in the Mastering Chain Create a More Desirable Sound Than a Single Limiter?

When mastering Electronic Dance Music, can two limiters in the mastering chain create a more desirable sound than a single limiter? Viktor Nilsson Audio Technology, bachelor's level 2020 Luleå University of Technology Department of Arts, Communication and Education Viktor Nilsson Luleå University of Technology 2020 Abstract The loudness war has been a widely discussed topic for many years. Loudness normalization has begun to slow down the range of genres affected by this war, but Electronic Dance Music is one of the genres that is still affected. Because some genres are still in this war, there are still reasons to achieve a loud master while simultaneously trying to sound good. Claims have been made by different mastering engineers that using two limiters in a chain can create a more transparent loudness. To investigate the reliability of this claim, listening tests using different limiter configurations was performed. 12 trained listeners would give their subjective preference over one and two limiters in the master chain. The results showed no significant difference in subjective preference. However, the subjects were able to describe some attributes that made a distinction between the limiter configurations. 1 Viktor Nilsson Luleå University of Technology 2020 Table of Contents ABSTRACT ........................................................................................................................................................ 1 1. INTRODUCTION....................................................................................................................................... -

Increasing Effective Amplifier Output Power Using Audio Compression

INCREASING EFFECTIVE AMPLIFIER OUTPUT POWER USING AUDIO COMPRESSION By: Joel Bump, President/Director of Engineering, RDL INTRODUCTION The power rating for audio power amplifiers used in commercial installations must deliver the average speech or music power plus reserve power headroom sufficient to handle audio peaks. The average power demanded from an amplifier is only ever a fraction of the total rated power because the average power in either speech or music signals is much less than the peak power. This article examines the relationship between required amplifier power and the dynamic content of speech. Amplifiers used in commercial installations are typically rated in Watts RMS, a term that describes the essentially unclipped RMS voltage an amplifier can deliver continuously into a resistive load. This is commonly referred to as RMS power. RDL produces several audio power amplifiers that are rated for a specific RMS power “plus compression”. The qualifier “plus compression” is used to indicate that the continuous average usable output power will be greater than that available from a conventional amplifier (without compression). The amount of additional power the compressor makes available can substantially reduce the required amplifier power output. The amplifier used for the measurements in this report is the RDL FP-PA20. The integral compressor, using only a nominal amount of compression, will increase the output power of speech by 2.2 times. Therefore, the FP-PA20 type amplifiers, rated for 20 Watts (RMS) “plus compression” will deliver the same unclipped output power on dynamic speech content as a standard power amplifier rated at 2.2 x 20 W, or 44 Watts RMS. -

Fft-Based Dynamic Range Compression

Proceedings of the 14th Sound and Music Computing Conference, July 5-8, Espoo, Finland FFT-BASED DYNAMIC RANGE COMPRESSION Leo McCormack and Vesa Valim¨ aki¨ Acoustics Lab, Dept. of Signal Processing and Acoustics Aalto University, FI-02150, Espoo, Finland leo.mccormack, [email protected] ABSTRACT ample, side-chain compression can be used to reduce the amplitude of a bass guitar signal to coincide with a kick Many of the dynamic range compressor (DRC) designs drum transient. This temporally dependent “ducking” in that are deployed in the marketplace today are constrained the bass guitar signal may then allow the two instruments to operate in the time-domain; therefore, they offer only to better complement one another. In the production of temporally dependent control of the amplitude envelope of dance music, this technique is commonly utilised in the a signal. Designs that offer an element of frequency de- more extreme case, by allowing the kick drum transient to pendency, are often restricted to perform specific tasks in- conspicuously carve out temporally dependent holes in the tended by the developer. Therefore, in order to realise a amplitude of other signals; resulting in a pumping effect more flexible DRC implementation, this paper proposes a that pulses in time with the music [10]. generalised time-frequency domain design that accommo- Serial and parallel compression techniques have also be- dates both temporally-dependent and frequency-dependent come widely used, as they allow for even greater control dynamic range control; for which an FFT-based imple- of the amplitude envelope of signals by utilising multiple mentation is also presented. -

Basic Digital Audio Effects

Digital Audio Effects Having learned to make basic waveforms and basic filtering lets CM0268 see how we can add some digital audio effects. These may be applied: MATLAB DSP GRAPHICS As part of the audio creation/synthesis stage — to be subsequently 332 • filtered, (re)synthesised At the end of the audio chain — as part of the production/mastering • phase. Effects can be applied in different orders and sometimes in a • parallel audio chain. The order of applying the same effects can have drastic differences 1 • in the output audio. Selection of effects and the ordering is a matter for the sound you JJ • wish to create. There is no absolute rule for the ordering. II J I Back Close Effect Types and Parameters Effect Types and Parameters IPATCH LEVEL Typical Guitar (and other) Effects Pipeline PATCH LEVEL (Prm) illustration below. You can use all effect Determines the overall volume level of the patch. SomeLinking ordering Effects is standard for some audiomodule processing,s together or seE.glecti:vely set certain 2 1 0 Sets the patch level in the range from 2 – 98, 1.0. A setting of 80 corresponds to unity gain (input level Compression Distortion EQ modulesNoise to on Redux or off. Amp Sim and output level are equal). The patches of the! G1/G1X consist of! eight ! ! ! Modulation Delay Reverb CM0268 serially linked effect modules, as shown in the MATLAB ! ! DSP ICOMP/EFX (Compressor/EFX) module GRAPHICS Common for some guitar effects pedal: This module comprises the effects that control the level dynamics such as compressor, and Effect modules 333 modulation effects such as tremolo and phaser.