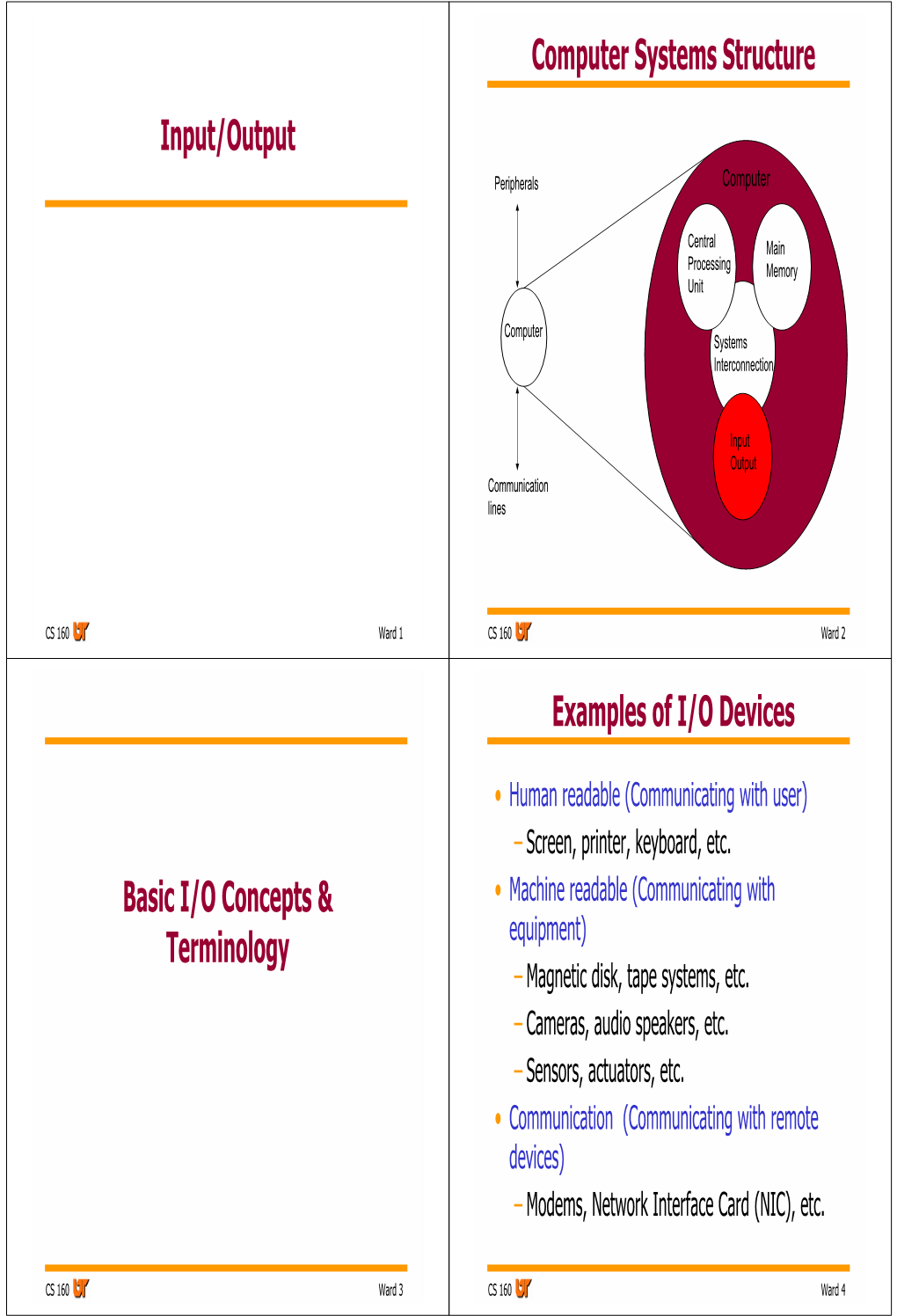

Input/Output Computer Systems Structure Basic I/O

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Processes Process States

Processes • A process is a program in execution • Synonyms include job, task, and unit of work • Not surprisingly, then, the parts of a process are precisely the parts of a running program: Program code, sometimes called the text section Program counter (where we are in the code) and other registers (data that CPU instructions can touch directly) Stack — for subroutines and their accompanying data Data section — for statically-allocated entities Heap — for dynamically-allocated entities Process States • Five states in general, with specific operating systems applying their own terminology and some using a finer level of granularity: New — process is being created Running — CPU is executing the process’s instructions Waiting — process is, well, waiting for an event, typically I/O or signal Ready — process is waiting for a processor Terminated — process is done running • See the text for a general state diagram of how a process moves from one state to another The Process Control Block (PCB) • Central data structure for representing a process, a.k.a. task control block • Consists of any information that varies from process to process: process state, program counter, registers, scheduling information, memory management information, accounting information, I/O status • The operating system maintains collections of PCBs to track current processes (typically as linked lists) • System state is saved/loaded to/from PCBs as the CPU goes from process to process; this is called… The Context Switch • Context switch is the technical term for the act -

Chapter 3: Processes

Chapter 3: Processes Operating System Concepts – 9th Edition Silberschatz, Galvin and Gagne ©2013 Chapter 3: Processes Process Concept Process Scheduling Operations on Processes Interprocess Communication Examples of IPC Systems Communication in Client-Server Systems Operating System Concepts – 9th Edition 3.2 Silberschatz, Galvin and Gagne ©2013 Objectives To introduce the notion of a process -- a program in execution, which forms the basis of all computation To describe the various features of processes, including scheduling, creation and termination, and communication To explore interprocess communication using shared memory and message passing To describe communication in client-server systems Operating System Concepts – 9th Edition 3.3 Silberschatz, Galvin and Gagne ©2013 Process Concept An operating system executes a variety of programs: Batch system – jobs Time-shared systems – user programs or tasks Textbook uses the terms job and process almost interchangeably Process – a program in execution; process execution must progress in sequential fashion Multiple parts The program code, also called text section Current activity including program counter, processor registers Stack containing temporary data Function parameters, return addresses, local variables Data section containing global variables Heap containing memory dynamically allocated during run time Operating System Concepts – 9th Edition 3.4 Silberschatz, Galvin and Gagne ©2013 Process Concept (Cont.) Program is passive entity stored on disk (executable -

CS 450: Operating Systems Sean Wallace <[email protected]>

Deadlock CS 450: Operating Systems Computer Sean Wallace <[email protected]> Science Science deadlock |ˈdedˌläk| noun 1 [ in sing. ] a situation, typically one involving opposing parties, in which no progress can be made: an attempt to break the deadlock. –New Oxford American Dictionary 2 Traffic Gridlock 3 Software Gridlock mutex_A.lock() mutex_B.lock() mutex_B.lock() mutex_A.lock() # critical section # critical section mutex_B.unlock() mutex_B.unlock() mutex_A.unlock() mutex_A.unlock() 4 Necessary Conditions for Deadlock 5 That is, what conditions need to be true (of some system) so that deadlock is possible? (Not the same as causing deadlock!) 6 1. Mutual Exclusion Resources can be held by process in a mutually exclusive manner 7 2. Hold & Wait While holding one resource (in mutex), a process can request another resource 8 3. No Preemption One process can not force another to give up a resource; i.e., releasing is voluntary 9 4. Circular Wait Resource requests and allocations create a cycle in the resource allocation graph 10 Resource Allocation Graphs 11 Process: Resource: Request: Allocation: 12 R1 R2 P1 P2 P3 R3 Circular wait is absent = no deadlock 13 R1 R2 P1 P2 P3 R3 All 4 necessary conditions in place; Deadlock! 14 In a system with only single-instance resources, necessary conditions ⟺ deadlock 15 P3 R1 P1 P2 R2 P2 Cycle without Deadlock! 16 Not practical (or always possible) to detect deadlock using a graph —but convenient to help us reason about things 17 Approaches to Dealing with Deadlock 18 1. Ostrich algorithm (Ignore it and hope it never happens) 2. -

Sched-ITS: an Interactive Tutoring System to Teach CPU Scheduling Concepts in an Operating Systems Course

Wright State University CORE Scholar Browse all Theses and Dissertations Theses and Dissertations 2017 Sched-ITS: An Interactive Tutoring System to Teach CPU Scheduling Concepts in an Operating Systems Course Bharath Kumar Koya Wright State University Follow this and additional works at: https://corescholar.libraries.wright.edu/etd_all Part of the Computer Engineering Commons, and the Computer Sciences Commons Repository Citation Koya, Bharath Kumar, "Sched-ITS: An Interactive Tutoring System to Teach CPU Scheduling Concepts in an Operating Systems Course" (2017). Browse all Theses and Dissertations. 1745. https://corescholar.libraries.wright.edu/etd_all/1745 This Thesis is brought to you for free and open access by the Theses and Dissertations at CORE Scholar. It has been accepted for inclusion in Browse all Theses and Dissertations by an authorized administrator of CORE Scholar. For more information, please contact [email protected]. SCHED – ITS: AN INTERACTIVE TUTORING SYSTEM TO TEACH CPU SCHEDULING CONCEPTS IN AN OPERATING SYSTEMS COURSE A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science By BHARATH KUMAR KOYA B.E, Andhra University, India, 2015 2017 Wright State University WRIGHT STATE UNIVERSITY GRADUATE SCHOOL April 24, 2017 I HEREBY RECOMMEND THAT THE THESIS PREPARED UNDER MY SUPERVISION BY Bharath Kumar Koya ENTITLED SCHED-ITS: An Interactive Tutoring System to Teach CPU Scheduling Concepts in an Operating System Course BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQIREMENTS FOR THE DEGREE OF Master of Science. _____________________________________ Adam R. Bryant, Ph.D. Thesis Director _____________________________________ Mateen M. Rizki, Ph.D. Chair, Department of Computer Science and Engineering Committee on Final Examination _____________________________________ Adam R. -

The Big Picture So Far Today: Process Management

The Big Picture So Far From the Architecture to the OS to the User: Architectural resources, OS management, and User Abstractions. Hardware abstraction Example OS Services User abstraction Processor Process management, Scheduling, Traps, Process protection, accounting, synchronization Memory Management, Protection, virtual memory Address spaces I/O devices Concurrency with CPU, Interrupt Terminal, mouse, printer, handling system calls File System File management, Persistence Files Distributed systems Networking, security, distributed file Remote procedure calls, system network file system System calls Four architectures for designing OS kernels Computer Science CS377: Operating Systems Lecture 4, page 1 Today: Process Management • A process as the unit of execution. • How are processes represented in the OS? • What are possible execution states and how does the system move from one state to another? • How are processes created in the system? • How do processes communicate? Is this efficient? Computer Science CS377: Operating Systems Lecture 4, page 2 What's in a Process? • Process: dynamic execution context of an executing program • Several processes may run the same program, but each is a distinct process with its own state (e.g., MS Word). • A process executes sequentially, one instruction at a time • Process state consists of at least: ! the code for the running program, ! the static data for the running program, ! space for dynamic data (the heap), the heap pointer (HP), ! the Program Counter (PC), indicating the next instruction, ! an execution stack with the program's call chain (the stack), the stack pointer (SP) ! values of CPU registers ! a set of OS resources in use (e.g., open files) ! process execution state (ready, running, etc.). -

Lecture 4: September 13 4.1 Process State

CMPSCI 377 Operating Systems Fall 2012 Lecture 4: September 13 Lecturer: Prashant Shenoy TA: Sean Barker & Demetre Lavigne 4.1 Process State 4.1.1 Process A process is a dynamic instance of a computer program that is being sequentially executed by a computer system that has the ability to run several computer programs concurrently. A computer program itself is just a passive collection of instructions, while a process is the actual execution of those instructions. Several processes may be associated with the same program; for example, opening up several windows of the same program typically means more than one process is being executed. The state of a process consists of - code for the running program (text segment), its static data, its heap and the heap pointer (HP) where dynamic data is kept, program counter (PC), stack and the stack pointer (SP), value of CPU registers, set of OS resources in use (list of open files etc.), and the current process execution state (new, ready, running etc.). Some state may be stored in registers, such as the program counter. 4.1.2 Process Execution States Processes go through various process states which determine how the process is handled by the operating system kernel. The specific implementations of these states vary in different operating systems, and the names of these states are not standardised, but the general high-level functionality is the same. When a process is first started/created, it is in new state. It needs to wait for the process scheduler (of the operating system) to set its status to "new" and load it into main memory from secondary storage device (such as a hard disk or a CD-ROM). -

Execution Architecture for Real-Time Systems by Ton Kostelijk

Execution Architecture for Real-Time Systems Dr. A.P. Kostelijk (Ton) Version 0.1 Ton Kostelijk - Philips Digital 1 Systems Labs Content • Discussion on You: performance issues • Discussion • Introductory examples • OS: process context switch, process- creation, thread, co-operative / • Various scheduling preemptive multi-tasking, exercises scheduling, EDF, RMS, RMA. • How to design concur- rency / multi-tasking • RMA exercise Version 0.1 Ton Kostelijk - Philips Digital 2 Systems Labs Discussion on performance issues SW HW Version 0.1 Ton Kostelijk - Philips Digital 3 Systems Labs Model: Levels of execution Execution architecture 1. Task and priority assignment Execution architecture SW 2. Algorithms, source code Compiler 3. Machine code, CPU HW arch, settings HW 4. Busses and buffering: data comm. HW arch, settings 5. Device access Version 0.1 Ton Kostelijk - Philips Digital 4 Systems Labs Content • Discussion on You: performance issues • Discussion • Introductory examples • OS: process context switch, process- creation, thread, preemptive • Various scheduling multi-tasking, scheduling, EDF, exercises RMS, RMA. • How to design concur- rency / multi-tasking • RMA exercise Version 0.1 Ton Kostelijk - Philips Digital 5 Systems Labs Example 1: a coffee machine a = place new filter; 1 b = add new coffee; 1 ED c = fill water reservoir; 2 D DL DI d = heat water and pour; 2 D F G PDLQ ^D E F G ` W PDLQ ^F D E G ` W PDLQ ^DBL FBL DBI E FBI G ` W Version 0.1 Ton Kostelijk - Philips Digital 6 Systems Labs Observations • Timing requirements of actions are determined by dependency relations and deadlines. • Hard-coded schedule of actions: + Reliable, easy testable + For small systems might be the best choice. -

CS 162 Operating Systems and Systems Programming Lecture 3

CS 162 Operating Systems and Systems Programming Answer: Decompose hard problem into simpler ones. Instead of dealing with Professor: Anthony Joseph everything going on at once, separate into logical abstractions that we can deal Spring 2004 with one at a time. Lecture 3: 3.2 Processes Concurrency: Processes, Threads, and Address Spaces The notion of a “process” is a central concept for Operating Systems. 3.0 Main point: What are processes? Process: Operating system abstraction to represent what is needed to run a single How are they related to threads and address spaces? program (this is the traditional UNIX definition) Formally, a process is a sequential stream of execution in its own address space. 3.1 Concurrency 3.1.1 Definitions: 3.2.1 Two parts to a (traditional Unix) process: Uniprogramming: one process at a time (e.g., MS/DOS, early Macintosh) 1. Sequential program execution: the code in the process is executed as a single, sequential stream of execution (no concurrency inside a process). This Easier for operating system builder: get rid of problem of concurrency by defining is known as a thread of control. it away. For personal computers, idea was: one user does only one thing at a 2. State Information: everything specific to a particular execution of a program: time. Encapsulates protection: address space • CPU registers Harder for user: can’t work while waiting for printer • Main memory (contents of address space) • I/O state (in UNIX this is represented by file descriptors) Multiprogramming: more than one process at a time (UNIX, OS/2, Windows NT). -

Operating Systems Processes and Threads

Operating Systems Processes and Threads [2] Process in the Operating System Process - an abstraction of a running program with its computing environment. Process is a basic dynamic object in the operating system. Requirements to be met by the operating system with reference to processes: • interleaving the execution of multiple processes to maximize processor uti- lization while providing reasonable response time, • allocating resources to processes in conformance with a specified policy, while at the same time avoiding deadlock, • supporting interprocess communication, • supporting user creation of processes. [3] Multiprogramming One program counter Four program counters Process A switch D B C Process C A BCD B A D Time (a) (b) (c) • process must not be programmed with built-in assumptions about timing, • the difference between a process and a program, • processes sequential, concurrent, parallel and distributed, [4] Process Creation and Termination Four principal events that cause processes to be created: • system initialization, Processes and Threads • execution of a process creation system call by a running process, • a user request to create a new process, • initiation of a batch job. Process may terminate due to one of the following conditions: • normal exit (voluntary), • error exit (voluntary), • fatal error (involuntary), • killed by another process (involuntary). [5] Process States Running 1. Process blocks for input 13 2 2. Scheduler picks another process 3. Scheduler picks this process 4. Input becomes available Blocked Ready 4 The basic states of a process: • running - actually using the CPU at that instant, • ready - runnable, temporarily stopped to let another process run, • blocked - unable to run until some external event happens. -

Process and Kernel • OS Provides Execution Environment to Run User

Process and Kernel OS provides execution environment to run user processes • { Basic framework for code execution { Services like file management and I/O, and interface to the same Process • { Single sequence of instructions in user address space { Control point or program counter { Multiple control points or threads Virtual machine and multiprogramming • { Each process has its own registers and address space { Process gets global services (I/O) from the OS { Kernel stores address space in different memory objects, including physical memory, disk, swap areas { Memory management subsystem shuffles pages between physical memory and other storage objects { Every process needs registers but there is only one set of hardware registers Kernel keeps process registers updated and loads and stores them into hardware registers for currently ∗ running process Resources • { Processes contend for each resource, including cpu time, memory, peripherals { OS acts as a resource manager, distributing the resources fairly as well as optimally { Processes that do not get a resource (but need it) are blocked Processes can also get blocked on cpu ∗ Processes get cpu for short bursts of time, called a quantum, typically about 10 milliseconds ∗ Time slicing ∗ OS provides a number of facilities to application programmers, such as use of I/O devices • { Users do not have to write code to control these devices { OS provides high-level abstract programming interface to access these devices (such as fopen(3)) { OS also provides access synchronization and error recovery -

Process States and Memory Management

Process States and Memory Management Learning Objectives At the end of this lab you should be able to: Demonstrate three main states of processes Identify allowed and disallowed process state transitions Show entry in and exit from waiting state on two types of events Demonstrate three placement strategies used in memory management Demonstrate virtual memory activity as part of memory management Tutorial Exercises Initial Preparation This tutorial uses the CPU‐OS Simulator software which simulates the functions of a typical modern CPU and a typical Operating System (OS). To start the simulator, double‐click on the simulator icon or name. This starts up the CPU simulator’s main window. Next go to the OS simulator’s main window by first selecting the Advanced tab and then clicking on the OS 0… button. Please read the instructions carefully before you attempt the exercises using the simulator. If at any point the simulator crashes, restart it and carry on from where you left. LO 1: Investigating Process States and State Transitions In this section we’ll look at different process states and the transitions from one state to another. Some of these transitions are allowed and some are not, i.e. illegal transitions. In the OS Simulator window select the Views tab. Click on the VIEW PROCESS STATES… button. You’ll see the Process States window displayed. This window shows a graphical representation of the Ready Queue where the process is in Ready State. It also shows a representation of the CPU where the process is in Running State. Also shown is the representation of the Waiting Queue where the process is in Waiting State. -

The Operating System Kernel: Implementing Processes and Threads

“runall” 2002/9/23 page 105 CHAPTER 4 The Operating System Kernel: Implementing Processes and Threads 4.1 KERNEL DEFINITIONS AND OBJECTS 4.2 QUEUE STRUCTURES 4.3 THREADS 4.4 IMPLEMENTING PROCESSES AND THREADS 4.5 IMPLEMENTING SYNCHRONIZATION AND COMMUNICATION MECHANISMS 4.6 INTERRUPT HANDLING The process model is fundamental to operating system (OS) design, implementation, and use. Mechanisms for process creation, activation, and termination, and for synchroniza- tion, communication, and resource control form the lowest level or kernel of all OS and concurrent programming systems. Chapters 2 and 3 described these mechanisms abstractly from a user’s or programmer’s view, working at the application level of a higher level of an OS. However, these chapters did not provide details of the internal structure, representations, algorithms, or hardware interfaces used by these mechanisms. In this chapter, we present a more complete picture, discussing, for example, how a process is blocked and unblocked. We start with an overview of possible kernel functions, objects, and organizations. The remaining sections are concerned with implementation aspects of the kernel. First, we outline the various queue data structures that are pervasive throughout OSs. The next two sections elaborate on the most widely used adaptation of processes, namely, threads, and show how processes and threads are built. Internal representations and code for important interaction objects, including semaphores, locks, monitors, and messages are then discussed; a separate subsection on the topic of timers also appears. The last section presents the lowest-level kernel task, interrupt handling, and illustrates how this error-prone, difficult function can be made to fit naturally into the process model.