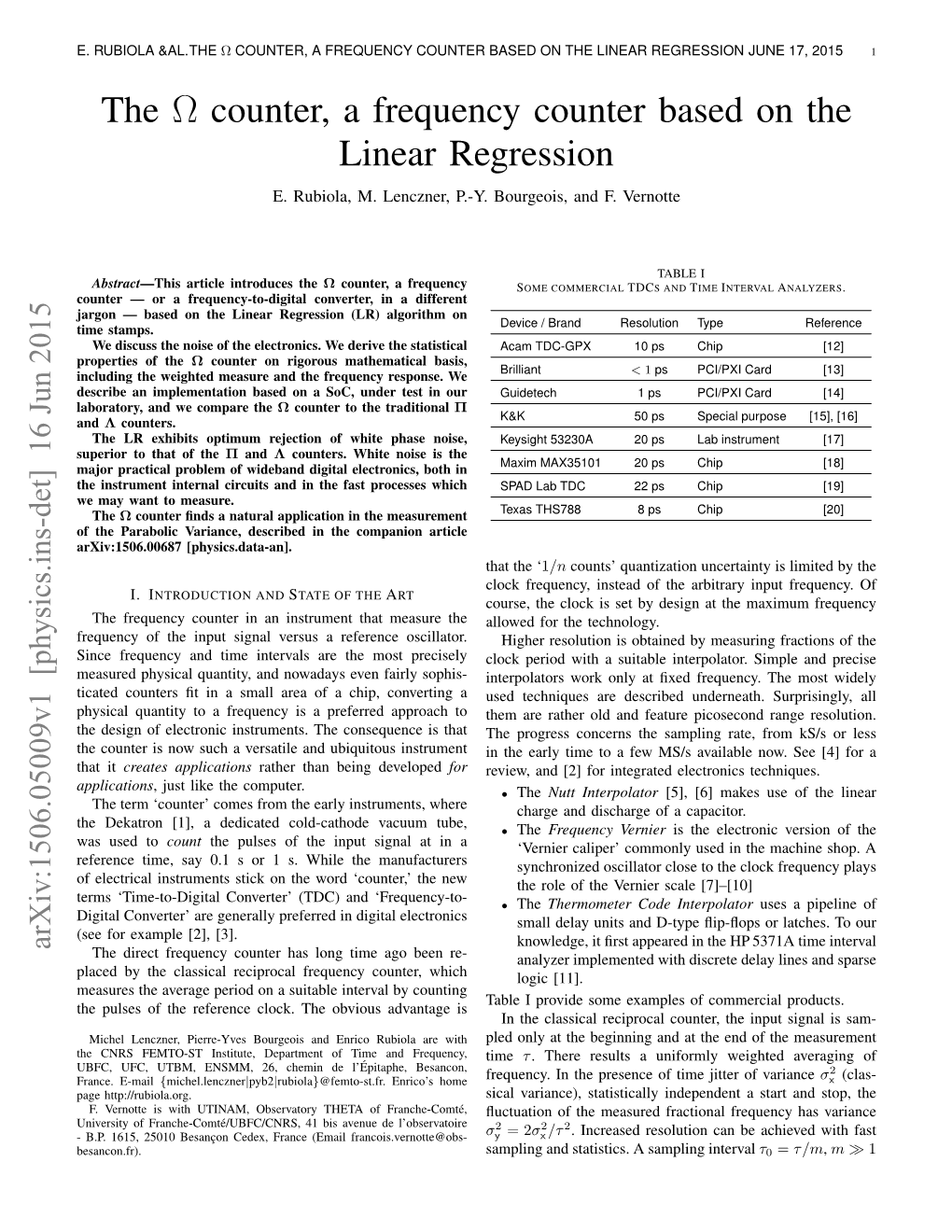

THE Ω COUNTER, a FREQUENCY COUNTER BASED on the LINEAR REGRESSION JUNE 17, 2015 1 the Ω Counter, a Frequency Counter Based on the Linear Regression E

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Hybrid Drowsy SRAM and STT-RAM Buffer Designs for Dark-Silicon

This article has been accepted for inclusion in a future issue of this journal. Content is final as presented, with the exception of pagination. IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS 1 Hybrid Drowsy SRAM and STT-RAM Buffer Designs for Dark-Silicon-Aware NoC Jia Zhan, Student Member, IEEE, Jin Ouyang, Member, IEEE,FenGe,Member, IEEE, Jishen Zhao, Member, IEEE, and Yuan Xie, Fellow, IEEE Abstract— The breakdown of Dennard scaling prevents us MCMC MC from powering all transistors simultaneously, leaving a large fraction of dark silicon. This crisis has led to innovative work on Tile link power-efficient core and memory architecture designs. However, link link RouterRouter the research for addressing dark silicon challenges with network- To router on-chip (NoC), which is a major contributor to the total chip NI power consumption, is largely unexplored. In this paper, we Core link comprehensively examine the network power consumers and L1-I$ L2 L1-D$ the drawbacks of the conventional power-gating techniques. To overcome the dark silicon issue from the NoC’s perspective, we MCMC MC propose DimNoC, a dim silicon scheme, which leverages recent drowsy SRAM design and spin-transfer torque RAM (STT-RAM) Fig. 1. 4 × 4 NoC-based multicore architecture. In each node, the local technology to replace pure SRAM-based NoC buffers. processing elements (core, L1, L2 caches, and so on) are attached to a router In particular, we propose two novel hybrid buffer architectures: through an NI. Routers are interconnected through links to form an NoC. 1) a hierarchical buffer architecture, which divides the input Four memory controllers are attached at the four corners, which will be used buffers into a set of levels with different power states and 2) a for off-chip memory access. -

An Analysis of Data Corruption in the Storage Stack

An Analysis of Data Corruption in the Storage Stack Lakshmi N. Bairavasundaram∗, Garth R. Goodson†, Bianca Schroeder‡ Andrea C. Arpaci-Dusseau∗, Remzi H. Arpaci-Dusseau∗ ∗University of Wisconsin-Madison †Network Appliance, Inc. ‡University of Toronto {laksh, dusseau, remzi}@cs.wisc.edu, [email protected], [email protected] Abstract latent sector errors, within disk drives [18]. Latent sector errors are detected by a drive’s internal error-correcting An important threat to reliable storage of data is silent codes (ECC) and are reported to the storage system. data corruption. In order to develop suitable protection Less well-known, however, is that current hard drives mechanisms against data corruption, it is essential to un- and controllers consist of hundreds-of-thousandsof lines derstand its characteristics. In this paper, we present the of low-level firmware code. This firmware code, along first large-scale study of data corruption. We analyze cor- with higher-level system software, has the potential for ruption instances recorded in production storage systems harboring bugs that can cause a more insidious type of containing a total of 1.53 million disk drives, over a pe- disk error – silent data corruption, where the data is riod of 41 months. We study three classes of corruption: silently corrupted with no indication from the drive that checksum mismatches, identity discrepancies, and par- an error has occurred. ity inconsistencies. We focus on checksum mismatches since they occur the most. Silent data corruptionscould lead to data loss more of- We find more than 400,000 instances of checksum ten than latent sector errors, since, unlike latent sector er- mismatches over the 41-month period. -

Understanding Real World Data Corruptions in Cloud Systems

Understanding Real World Data Corruptions in Cloud Systems Peipei Wang, Daniel J. Dean, Xiaohui Gu Department of Computer Science North Carolina State University Raleigh, North Carolina {pwang7,djdean2}@ncsu.edu, [email protected] Abstract—Big data processing is one of the killer applications enough to require attention, little research has been done to for cloud systems. MapReduce systems such as Hadoop are the understand software-induced data corruption problems. most popular big data processing platforms used in the cloud system. Data corruption is one of the most critical problems in In this paper, we present a comprehensive study on the cloud data processing, which not only has serious impact on characteristics of the real world data corruption problems the integrity of individual application results but also affects the caused by software bugs in cloud systems. We examined 138 performance and availability of the whole data processing system. data corruption incidents reported in the bug repositories of In this paper, we present a comprehensive study on 138 real world four Hadoop projects (i.e., Hadoop-common, HDFS, MapRe- data corruption incidents reported in Hadoop bug repositories. duce, YARN [17]). Although Hadoop provides fault tolerance, We characterize those data corruption problems in four aspects: our study has shown that data corruptions still seriously affect 1) what impact can data corruption have on the application and system? 2) how is data corruption detected? 3) what are the the integrity, performance, and availability -

The 4 States QRP Group HF Test Set Construction Manual

Copyright 2006, NB6M - Unauthorized Copying or Publication Prohibited The 4 States QRP Group HF Test Set Construction Manual Containing several key pieces of simple Test Equipment that are used to either test or troubleshoot radio circuitry By Wayne McFee, NB6M Revision 0.2 October 21, 2007 Copyright 2006, NB6M - Unauthorized Copying or Publication Prohibited 1 THE HF TEST SET .....................................................................................................................................3 INTRODUCTION............................................................................................................................................3 HF TEST SET SCHEMATIC ...........................................................................................................................5 BOARD LAYOUT..........................................................................................................................................6 PARTS LIST .................................................................................................................................................7 TOOLS AND EQUIPMENT NEEDED................................................................................................................9 PC BOARD, PARTS SIDE ...........................................................................................................................10 PC BOARD, TRACE SIDE...........................................................................................................................11 STARTING -

Keysight 53147A/148A/149A Microwave Frequency Counter/Power Meter/DVM

Keysight 53147A/148A/149A Microwave Frequency Counter/Power Meter/DVM Assembly Level Service Guide Notices U.S. Government Rights Warranty The Software is “commercial computer THE MATERIAL CONTAINED IN THIS Copyright Notice software,” as defined by Federal Acqui- DOCUMENT IS PROVIDED “AS IS,” sition Regulation (“FAR”) 2.101. Pursu- AND IS SUBJECT TO BEING © Keysight Technologies 2001 - 2017 ant to FAR 12.212 and 27.405-3 and CHANGED, WITHOUT NOTICE, IN No part of this manual may be repro- Department of Defense FAR Supple- FUTURE EDITIONS. FURTHER, TO THE duced in any form or by any means ment (“DFARS”) 227.7202, the U.S. MAXIMUM EXTENT PERMITTED BY (including electronic storage and government acquires commercial com- APPLICABLE LAW, KEYSIGHT DIS- retrieval or translation into a foreign puter software under the same terms CLAIMS ALL WARRANTIES, EITHER language) without prior agreement and by which the software is customarily EXPRESS OR IMPLIED, WITH REGARD written consent from Keysight Technol- provided to the public. Accordingly, TO THIS MANUAL AND ANY INFORMA- ogies as governed by United States and Keysight provides the Software to U.S. TION CONTAINED HEREIN, INCLUD- international copyright laws. government customers under its stan- ING BUT NOT LIMITED TO THE dard commercial license, which is IMPLIED WARRANTIES OF MER- Manual Part Number embodied in its End User License CHANTABILITY AND FITNESS FOR A 53147-90010 Agreement (EULA), a copy of which can PARTICULAR PURPOSE. KEYSIGHT be found at http://www.keysight.com/ SHALL NOT BE LIABLE FOR ERRORS Edition find/sweula. The license set forth in the OR FOR INCIDENTAL OR CONSE- Edition 3, November 1, 2017 EULA represents the exclusive authority QUENTIAL DAMAGES IN CONNECTION by which the U.S. -

Keysight U1251B and U1252B Handheld Digital Multimeter

Keysight U1251B and U1252B Handheld Digital Multimeter User’s and Service Guide Notices U.S. Government Rights Warranty The Software is “commercial computer THE MATERIAL CONTAINED IN THIS Copyright Notice software,” as defined by Federal DOCUMENT IS PROVIDED “AS IS,” AND Acquisition Regulation (“FAR”) 2.101. IS SUBJECT TO BEING CHANGED, © Keysight Technologies 2009 – 2019 Pursuant to FAR 12.212 and 27.405-3 WITHOUT NOTICE, IN FUTURE No part of this manual may be and Department of Defense FAR EDITIONS. FURTHER, TO THE reproduced in any form or by any Supplement (“DFARS”) 227.7202, the MAXIMUM EXTENT PERMITTED BY means (including electronic storage U.S. government acquires commercial APPLICABLE LAW, KEYSIGHT and retrieval or translation into a computer software under the same DISCLAIMS ALL WARRANTIES, EITHER foreign language) without prior terms by which the software is EXPRESS OR IMPLIED, WITH REGARD agreement and written consent from customarily provided to the public. TO THIS MANUAL AND ANY Keysight Technologies as governed by Accordingly, Keysight provides the INFORMATION CONTAINED HEREIN, United States and international Software to U.S. government INCLUDING BUT NOT LIMITED TO THE copyright laws. customers under its standard IMPLIED WARRANTIES OF commercial license, which is embodied MERCHANTABILITY AND FITNESS FOR Manual Part Number in its End User License Agreement A PARTICULAR PURPOSE. KEYSIGHT U1251-90036 (EULA), a copy of which can be found at SHALL NOT BE LIABLE FOR ERRORS http://www.keysight.com/find/sweula. OR FOR INCIDENTAL OR Edition The license set forth in the EULA CONSEQUENTIAL DAMAGES IN Edition 24, July 26, 2019 represents the exclusive authority by CONNECTION WITH THE FURNISHING, which the U.S. -

MRAM Technology Status

National Aeronautics and Space Administration MRAM Technology Status Jason Heidecker Jet Propulsion Laboratory Pasadena, California Jet Propulsion Laboratory California Institute of Technology Pasadena, California JPL Publication 13-3 2/13 National Aeronautics and Space Administration MRAM Technology Status NASA Electronic Parts and Packaging (NEPP) Program Office of Safety and Mission Assurance Jason Heidecker Jet Propulsion Laboratory Pasadena, California NASA WBS: 104593 JPL Project Number: 104593 Task Number: 40.49.01.09 Jet Propulsion Laboratory 4800 Oak Grove Drive Pasadena, CA 91109 http://nepp.nasa.gov i This research was carried out at the Jet Propulsion Laboratory, California Institute of Technology, and was sponsored by the National Aeronautics and Space Administration Electronic Parts and Packaging (NEPP) Program. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement by the United States Government or the Jet Propulsion Laboratory, California Institute of Technology. ©2013. California Institute of Technology. Government sponsorship acknowledged. ii TABLE OF CONTENTS 1.0 Introduction ............................................................................................................................................................ 1 2.0 MRAM Technology ................................................................................................................................................ 2 2.1 -

53200A Series RF/Universal Frequency Counter/Timers

Keysight Technologies 53200A Series RF/Universal Frequency Counter/Timers Data Sheet Imagine Your Counter Doing More! Introduction Frequency counters are depended on in R&D and in manufacturing for the fastest, most accurate frequency and time interval measurements. The 53200 Series of RF and universal frequency counter/timers expands on this expectation to provide you with the most information, connectivity and new measurement capabilities, while building on the speed and accuracy you’ve depended on with Keysight Technologies, Inc. time and frequency measurement expertise. Three available models offer resolution capabilities up to 12 digits/sec frequency resolution on a one second gate. Single- shot time interval measurements can be resolved down to 20 psec. All models offer new built-in analysis and graphing capabilities to maximize the insight and information you receive. More bandwidth Measurement by model Measurements Model Standard Opt MW Inputs – 350 MHz baseband frequency 350 MHz Input (53210A: Ch 2, – 6 or 15 GHz optional microwave Channel(s) 53220A/30A: Ch 3) channels Frequency 53210A, ● ● More resolution & speed 53220A, – 12 digits/sec 53230A – 20 ps single-shot time resolution Frequency ratio 53210A, ● ● – Up to 75,000 and 90,000 53220A, readings/sec (frequency and 53230A time interval) Period 53210A, ● ● More insight 53220A, 53230A – Datalog trend plot Minimum/maximum/ 53210A, ● – Cumulative histogram peak-to-peak input 53220A, – Built-in math analysis and voltage 53230A statistics – 1M reading memory and RF signal strength -

The Effects of Repeated Refresh Cycles on the Oxide Integrity of EEPROM Memories at High Temperature by Lynn Reed and Vema Reddy Tekmos, Inc

The Effects of Repeated Refresh Cycles on the Oxide Integrity of EEPROM Memories at High Temperature By Lynn Reed and Vema Reddy Tekmos, Inc. 4120 Commercial Center Drive, #400, Austin, TX 78744 [email protected], [email protected] Abstract Data retention in stored-charge based memories, such as Flash and EEPROMs, decreases with increasing temperature. Compensation for this shortening of retention time can be accomplished by refreshing the data using periodic erase-write refresh cycles, although the number of these cycles is limited by oxide integrity. An alternate approach is to use refresh cycles consisting of a rewrite only cycles, without the prior erase cycle. The viability of this approach requires that this refresh cycle induces less damage than an erase-write cycle. This paper studies the effects of repeated refresh cycles on oxide integrity in a high temperature environment and makes comparisons to the damage caused by erase-write cycles. The experiment consisted of running a large number of refresh cycles on a selected byte. The control group was other bytes which were not subjected to refresh only cycles. The oxide integrity was checked by performing repeated erase-write cycles on each of the two groups to determine if the refresh cycles decreased the number of erase-write cycles before failure. Data was collected from multiple parts, with different numbers of refresh cycles, and at temperatures ranging from 25C to 190C. The experiment was conducted on microcontrollers containing embedded EEPROM memories. The microcontrollers were programmed to test and measure their own memories, and to report the results to an external controller. -

Chapter 26 Oscillator Is Sufficient for Most of Our Needs and Most Amateur Equipment Relies on This Technique

Test Procedures and Projects 26 his chapter, written by ARRL Technical Advisor Doug Millar, K6JEY, covers the test equipment and measurement techniques common to Amateur Radio. With the increasing complexity of T amateur equipment and the availability of sophisticated test equipment, measurement and test procedures have also become more complex. There was a time when a simple bakelite cased volt-ohm meter (VOM) could solve most problems. With the advent of modern circuits that use advanced digital techniques, precise readouts and higher frequencies, test requirements and equipment have changed. In addition to the test procedures in this chapter, other test procedures appear in Chapters 14 and 15. TEST AND MEASUREMENT BASICS The process of testing requires a knowledge of what must be measured and what accuracy is required. If battery voltage is measured and the meter reads 1.52 V, what does this number mean? Does the meter always read accurately or do its readings change over time? What influences a meter reading? What accuracy do we need for a meaningful test of the battery voltage? A Short History of Standards and Traceability Since early times, people who measured things have worked to establish a system of consistency between measurements and measurers. Such consistency ensures that a measurement taken by one person could be duplicated by others — that measurements are reproducible. This allows discussion where everyone can be assured that their measurements of the same quantity would have the same result. In most cases, and until recently, consistent measurements involved an artifact: a physical object. If a merchant or scientist wanted to know what his pound weighed, he sent it to a laboratory where it was compared to the official pound. -

On the Effects of Data Corruption in Files

Just One Bit in a Million: On the Effects of Data Corruption in Files Volker Heydegger Universität zu Köln, Historisch-Kulturwissenschaftliche Informationsverarbeitung (HKI), Albertus-Magnus-Platz, 50968 Köln, Germany [email protected] Abstract. So far little attention has been paid to file format robustness, i.e., a file formats capability for keeping its information as safe as possible in spite of data corruption. The paper on hand reports on the first comprehensive research on this topic. The research work is based on a study on the status quo of file format robustness for various file formats from the image domain. A controlled test corpus was built which comprises files with different format characteristics. The files are the basis for data corruption experiments which are reported on and discussed. Keywords: digital preservation, file format, file format robustness, data integ- rity, data corruption, bit error, error resilience. 1 Introduction Long-term preservation of digital information is by now and will be even more so in the future one of the most important challenges for digital libraries. It is a task for which a multitude of factors have to be taken into account. These factors are hardly predictable, simply due to the fact that digital preservation is something targeting at the unknown future: Are we still able to maintain the preservation infrastructure in the future? Is there still enough money to do so? Is there still enough proper skilled manpower available? Can we rely on the current legal foundation in the future as well? How long is the tech- nology we use at the moment sufficient for the preservation task? Are there major changes in technologies which affect the access to our digital assets? If so, do we have adequate strategies and means to cope with possible changes? and so on. -

Exploiting Asymmetry in Edram Errors for Redundancy-Free Error

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TETC.2019.2960491, IEEE Transactions on Emerging Topics in Computing IEEE TRANSACTIONS ON EMERGING TOPICS IN COMPUTING 1 Exploiting Asymmetry in eDRAM Errors for Redundancy-Free Error-Tolerant Design Shanshan Liu (Member, IEEE), Pedro Reviriego (Senior Member, IEEE), Jing Guo, Jie Han (Senior Member, IEEE) and Fabrizio Lombardi (Fellow, IEEE) Abstract—For some applications, errors have a different impact on data and memory systems depending on whether they change a zero to a one or the other way around; for an unsigned integer, a one to zero (or zero to one) error reduces (or increases) the value. For some memories, errors are also asymmetric; for example, in a DRAM, retention failures discharge the storage cell. The tolerance of such asymmetric errors would result in a robust and efficient system design. Error Control Codes (ECCs) are one common technique for memory protection against these errors by introducing some redundancy in memory cells. In this paper, the asymmetry in the errors in Embedded DRAMs (eDRAMs) is exploited for error-tolerant designs without using any ECC or parity, which are redundancy-free in terms of memory cells. A model for the impact of retention errors and refresh time of eDRAMs on the False Positive rate or False Negative rate of some eDRAM applications is proposed and analyzed. Bloom Filters (BFs) and read-only or write-through caches implemented in eDRAMs are considered as the first case studies for this model.