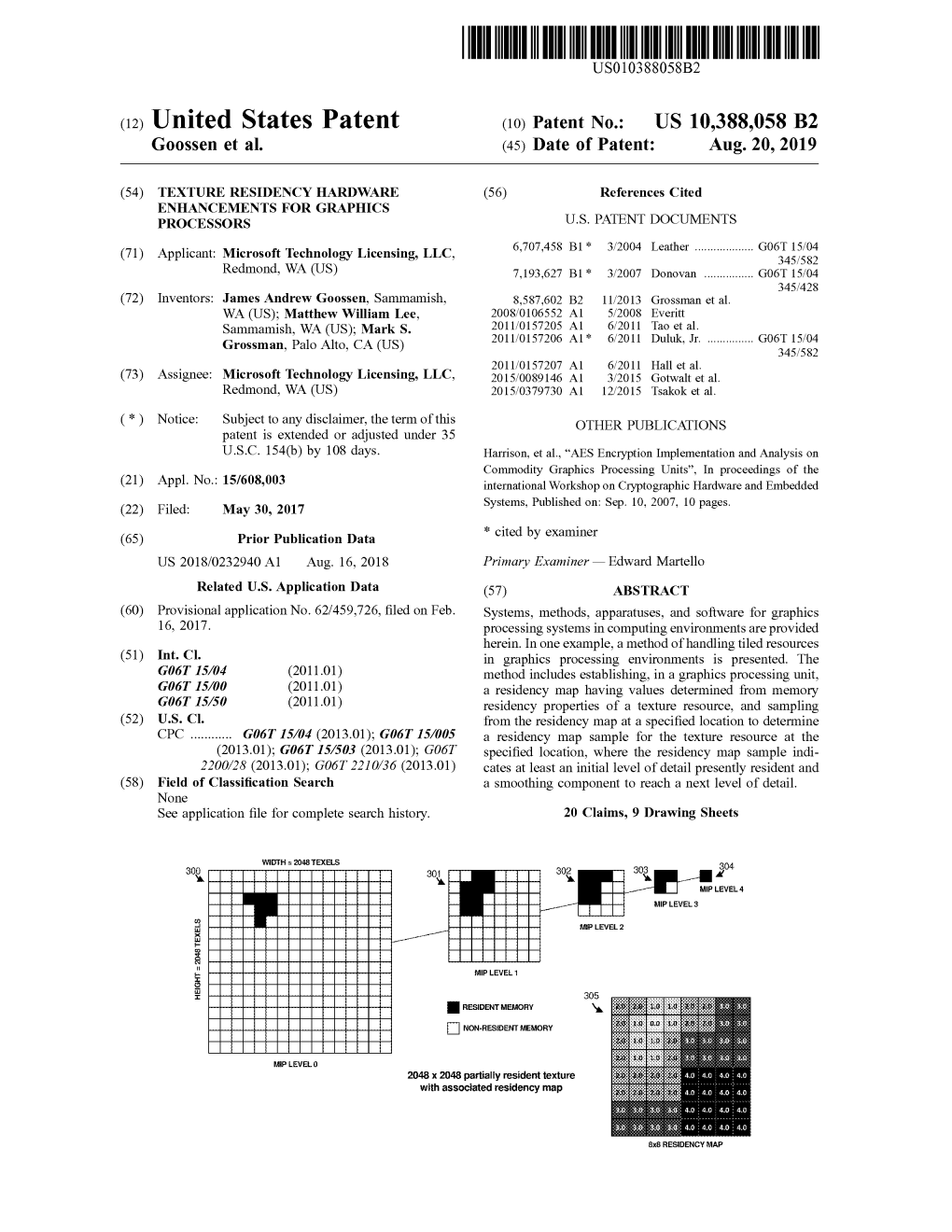

( 12 ) United States Patent ( 10) Patent No

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Real-Time Rendering Techniques with Hardware Tessellation

Volume 34 (2015), Number x pp. 0–24 COMPUTER GRAPHICS forum Real-time Rendering Techniques with Hardware Tessellation M. Nießner1 and B. Keinert2 and M. Fisher1 and M. Stamminger2 and C. Loop3 and H. Schäfer2 1Stanford University 2University of Erlangen-Nuremberg 3Microsoft Research Abstract Graphics hardware has been progressively optimized to render more triangles with increasingly flexible shading. For highly detailed geometry, interactive applications restricted themselves to performing transforms on fixed geometry, since they could not incur the cost required to generate and transfer smooth or displaced geometry to the GPU at render time. As a result of recent advances in graphics hardware, in particular the GPU tessellation unit, complex geometry can now be generated on-the-fly within the GPU’s rendering pipeline. This has enabled the generation and displacement of smooth parametric surfaces in real-time applications. However, many well- established approaches in offline rendering are not directly transferable due to the limited tessellation patterns or the parallel execution model of the tessellation stage. In this survey, we provide an overview of recent work and challenges in this topic by summarizing, discussing, and comparing methods for the rendering of smooth and highly-detailed surfaces in real-time. 1. Introduction Hardware tessellation has attained widespread use in computer games for displaying highly-detailed, possibly an- Graphics hardware originated with the goal of efficiently imated, objects. In the animation industry, where displaced rendering geometric surfaces. GPUs achieve high perfor- subdivision surfaces are the typical modeling and rendering mance by using a pipeline where large components are per- primitive, hardware tessellation has also been identified as a formed independently and in parallel. -

9.Texture Mapping

OpenGL_PG.book Page 359 Thursday, October 23, 2003 3:23 PM Chapter 9 9.Texture Mapping Chapter Objectives After reading this chapter, you’ll be able to do the following: • Understand what texture mapping can add to your scene • Specify texture images in compressed and uncompressed formats • Control how a texture image is filtered as it’s applied to a fragment • Create and manage texture images in texture objects and, if available, control a high-performance working set of those texture objects • Specify how the color values in the image combine with those of the fragment to which it’s being applied • Supply texture coordinates to indicate how the texture image should be aligned with the objects in your scene • Generate texture coordinates automatically to produce effects such as contour maps and environment maps • Perform complex texture operations in a single pass with multitexturing (sequential texture units) • Use texture combiner functions to mathematically operate on texture, fragment, and constant color values • After texturing, process fragments with secondary colors • Perform transformations on texture coordinates using the texture matrix • Render shadowed objects, using depth textures 359 OpenGL_PG.book Page 360 Thursday, October 23, 2003 3:23 PM So far, every geometric primitive has been drawn as either a solid color or smoothly shaded between the colors at its vertices—that is, they’ve been drawn without texture mapping. If you want to draw a large brick wall without texture mapping, for example, each brick must be drawn as a separate polygon. Without texturing, a large flat wall—which is really a single rectangle—might require thousands of individual bricks, and even then the bricks may appear too smooth and regular to be realistic. -

Antialiasing

Antialiasing CSE 781 Han-Wei Shen What is alias? Alias - A false signal in telecommunication links from beats between signal frequency and sampling frequency (from dictionary.com) Not just telecommunication, alias is everywhere in computer graphics because rendering is essentially a sampling process Examples: Jagged edges False texture patterns Alias caused by under-sampling 1D signal sampling example Actual signal Sampled signal Alias caused by under-sampling 2D texture display example Minor aliasing worse aliasing How often is enough? What is the right sampling frequency? Sampling theorem (or Nyquist limit) - the sampling frequency has to be at least twice the maximum frequency of the signal to be sampled Need two samples in this cycle Reconstruction After the (ideal) sampling is done, we need to reconstruct back the original continuous signal The reconstruction is done by reconstruction filter Reconstruction Filters Common reconstruction filters: Box filter Tent filter Sinc filter = sin(πx)/πx Anti-aliased texture mapping Two problems to address – Magnification Minification Re-sampling Minification and Magnification – resample the signal to a different resolution Minification Magnification (note the minification is done badly here) Magnification Simpler to handle, just resample the reconstructed signal Reconstructed signal Resample the reconstructed signal Magnification Common methods: nearest neighbor (box filter) or linear interpolation (tent filter) Nearest neighbor bilinear interpolation Minification Harder to handle The signal’s frequency is too high to avoid aliasing A possible solution: Increase the low pass filter width of the ideal sinc filter – this effectively blur the image Blur the image first (using any method), and then sample it Minification Several texels cover one pixel (under sampling happens) Solution: Either increase sampling rate or reduce the texture Frequency one pixel We will discuss: Under sample artifact 1. -

Texture Mapping Opengl Has a Pixel Pipeline Along with the Geometry Pipeline (From Processor Memory to Frame Buffer)

Pixel pipeline Texture Mapping OpenGL has a pixel pipeline along with the geometry pipeline (from processor memory to frame buffer) Tom Shermer Richard (Hao) Zhang There is a whole set of OpenGL functions on pixel Introduction to Computer Graphics manipulation, see OpenGL reference cards CMPT 361 – Lecture 18 Many functions for texture mapping and manipulation 1 2 Texture mapping Texture mapping in OpenGL How to map an image (texture) onto a surface In older versions, 1D and 2D texture mapping Now 3D/solid textures are supported in OpenGL Basic steps of texture mapping, see Chapter 7 in text 1. Generate a texture image and place it in texture memory on the GPU, e.g., glGenTextures(), glBindTexture(), etc. 2. Assign texture coordinates (references to texture image) to Image-related (2D) but also incorporating 3D data each fragment (pixel) in-between, texture mapping between Textures are assigned by texture coordinates image to surface (then fragments) associated with points on a surface 3. Apply texture to each fragment 3 4 1 Why texture mapping? Effect of texture mapping Real-world objects often have complex surface details even of a stochastic nature, e.g., the surface of an orange, patterns on a wood table, etc. Using many small polygons and smooth shading them to capture the details is too expensive A “cheat” : use an image (it is easy to take a photo and digitize it) to capture the details and patterns and paint it onto simple surfaces 5 6 Effect of texture mapping Textures Textures are patterns e.g., stripes, checkerboard, -

A Digital Rights Enabled Graphics Processing System

Graphics Hardware (2006) M. Olano, P. Slusallek (Editors) A Digital Rights Enabled Graphics Processing System Weidong Shi1, Hsien-Hsin S. Lee2, Richard M. Yoo2, and Alexandra Boldyreva3 1Motorola Application Research Lab, Motorola, Schaumburg, IL 2School of Electrical and Computer Engineering 3College of Computing Georgia Institute of Technology, Atlanta, GA 30332 Abstract With the emergence of 3D graphics/arts assets commerce on the Internet, to protect their intellectual property and to restrict their usage have become a new design challenge. This paper presents a novel protection model for commercial graphics data by integrating digital rights management into the graphics processing unit and creating a digital rights enabled graphics processing system to defend against piracy of entertainment software and copy- righted graphics arts. In accordance with the presented model, graphics content providers distribute encrypted 3D graphics data along with their certified licenses. During rendering, when encrypted graphics data, e.g. geometry or textures, are fetched by a digital rights enabled graphics processing system, it will be decrypted. The graph- ics processing system also ensures that graphics data such as geometry, textures or shaders are bound only in accordance with the binding constraints designated in the licenses. Special API extensions for media/software de- velopers are also proposed to enable our protection model. We evaluated the proposed hardware system based on cycle-based GPU simulator with configuration in line with realistic implementation and open source video game Quake 3D. Categories and Subject Descriptors (according to ACM CCS): I.3.3 [Computer Graphics]: Digital Rights, Graphics Processor 1. Introduction video players, mobile devices, etc. -

The Rasterizer Stage Texturing, Lighting, Testing and Blending 2

1 The Rasterizer Stage Texturing, Lighting, Testing and Blending 2 Triangle Setup, Triangle Traversal and Back Face Culling From Primitives To Fragments Post Clipping 3 . In the last stages of the geometry stage, vertices undergo the following: . They are projected into clip space by multiplication with the projection matrix . They are then clipped against the canonical view volume (unit cube), only vertices within the view volume are kept. After clipping vertices are then converted into screen space coordinates. Due to the canonical view volume all vertices‟ depth (Z) values are between 0 and 1. It is these screen space vertices that are received by the triangle setup stage. Triangle (primitive) Setup 4 . Triangle Setup links up the screen space vertices to form triangles (can form lines as well). This linking is done according to the topology specified for the set of vertices (triangle list, triangle strip, triangle fan, etc) . Once the linking is complete, backface culling is applied (if enabled). Triangles that are not culled are sent to the triangle traversal stage. Backface Culling 5 . Backface culling is a technique used to discard polygons facing away from the camera. This lessens the load on the rasterizer by discarding polygons that are hidden by front facing ones. It is sometimes necessary to disable backface culling to correctly render certain objects. Image courtesy of http://www.geometricalgebra.net/screenshots.html Backface Culling 6 V0 N N V0 V2 V1 V1 V2 Clockwise Anti-clockwise . Triangle Winding order is extremely important for backface culling. Backface culling determines whether a polygon is front facing or not by the direction of the Z value of the primitive‟s normal vector (why the Z value?). -

CSE 167: Introduction to Computer Graphics Lecture #8: Texture Mapping

CSE 167: Introduction to Computer Graphics Lecture #8: Texture Mapping Jürgen P. Schulze, Ph.D. University of California, San Diego Spring Quarter 2015 Announcements Homework 4 due Friday at 1pm Midterms to be returned on Thursday answers given in class 2 Lecture Overview Texture Mapping Overview Wrapping Texture coordinates Anti-aliasing 3 Large Triangles Pros: Often sufficient for simple geometry Fast to render Cons: Per vertex colors look boring and computer-generated 4 Texture Mapping Map textures (images) onto surface polygons Same triangle count, much more realistic appearance 5 Texture Mapping Goal: map locations in texture to locations on 3D geometry (1,1) Texture coordinate space Texture pixels (texels) have texture coordinates (s,t ) t Convention Bottom left corner of texture is at (s,t ) = (0,0) (0,0) Top right corner is at (s,t ) = (1,1) s Texture coordinates 6 Texture Mapping Store 2D texture coordinates s,t with each triangle vertex v1 (s,t ) = (0.65,0.75) (1,1) v0 (s,t ) = (0.6,0.4) (0.65,0.75) v2 t (s,t ) = (0.4,0.45) (0.4,0.45) (0.6,0.4) Triangle in any space before projection (0,0) s Texture coordinates 7 Texture Mapping Each point on triangle gets color from its corresponding point in texture v1 (1,1) (s,t ) = (0.65,0.75) (0.65,0.75) v0 t (s,t ) = (0.6,0.4) (0.4,0.45) (0.6,0.4) v2 (s,t ) = (0.4,0.45) (0,0) Triangle in any space before projection s Texture coordinates 8 Texture Mapping Primitives Modeling and viewing transformation Shading Projection Rasterization Fragment processing Includes texture mapping Frame-buffer access (z-buffering) 9 Image Texture Look-Up Given interpolated texture coordinates (s, t) at current pixel Closest four texels in texture space are at (s 0,t 0), (s 1,t 0), (s 0,t 1), (s 1,t 1) How to compute pixel color? t1 t t0 s0 s s1 10 Nearest-Neighbor Interpolation Use color of closest texel t1 t t0 s0 s s1 Simple, but low quality and aliasing 11 Bilinear Interpolation 1. -

Hardware-Independent Clipmapping

Hardware-Independent Clipmapping Antonio Seoane Javier Taibo Luis Hernández [email protected] [email protected] [email protected] Rubén López Alberto Jaspe [email protected] [email protected] VideaLAB School of Civil Engineering - University of A Coruña, Spain Campus de Elviña 15071 - Spain ABSTRACT We present a technique for efficient management of large textures and its real-time application to geometric models. The proposed technique is inspired by the clipmap [12] idea, that caches in video memory a subset of the texture mipmap pyramid. Based on this concept, we define some structures and a different management allowing its implementation on a personal computer without specific graphics hardware. Finally, we present the results of the application in a terrain visualization system, using several simultaneous textures with a detail up to 0.25 meters per texel, covering a 60,000 km2 area. Keywords Terrain visualization, multiresolution visualization, large data set visualization, level-of-detail techniques, texture mapping, clipmap, mipmap, texture caching. 1 INTRODUCTION One of the best and most used approaches that al- Applying textures to digital terrain models is the classi- lows the handling of big textures is the clipmap [12]. cal solution to simulate the missing geometry details. This technique separates the handling of the texture When we want to apply a large amount of texture to the and the geometry, allowing independence between both terrain surface, the storage problem arises. Although databases. The main problem of this technique is the both the system memory and the video memory are ex- requirement of specific hardware. tremely fast, there is limited storage capacity. -

Visualization of Three-Dimensional Models from Multiple Texel Images Created from Fused Ladar/Digital Imagery

Utah State University DigitalCommons@USU All Graduate Theses and Dissertations Graduate Studies 5-2016 Visualization of Three-Dimensional Models from Multiple Texel Images Created from Fused Ladar/Digital Imagery Cody C. Killpack Utah State University Follow this and additional works at: https://digitalcommons.usu.edu/etd Part of the Computer Engineering Commons Recommended Citation Killpack, Cody C., "Visualization of Three-Dimensional Models from Multiple Texel Images Created from Fused Ladar/Digital Imagery" (2016). All Graduate Theses and Dissertations. 4637. https://digitalcommons.usu.edu/etd/4637 This Thesis is brought to you for free and open access by the Graduate Studies at DigitalCommons@USU. It has been accepted for inclusion in All Graduate Theses and Dissertations by an authorized administrator of DigitalCommons@USU. For more information, please contact [email protected]. VISUALIZATION OF THREE-DIMENSIONAL MODELS FROM MULTIPLE TEXEL IMAGES CREATED FROM FUSED LADAR/DIGITAL IMAGERY by Cody C. Killpack A thesis submitted in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE in Computer Engineering Approved: Dr. Scott E. Budge Dr. Jacob H. Gunther Major Professor Committee Member Dr. Don Cripps Dr. Mark R. McLellan Committee Member Vice President for Research and Dean of the School of Graduate Studies UTAH STATE UNIVERSITY Logan, Utah 2015 ii Copyright c Cody C. Killpack 2015 All Rights Reserved iii Abstract Visualization of Three-Dimensional Models from Multiple Texel Images Created from Fused Ladar/Digital Imagery by Cody C. Killpack, Master of Science Utah State University, 2015 Major Professor: Dr. Scott E. Budge Department: Electrical and Computer Engineering The ability to create three-dimensional (3D) texel models, using registered texel images (fused ladar and digital imagery), is an important topic in remote sensing. -

An Introductory Tour of Interactive Rendering by Eric Haines, [email protected]

An Introductory Tour of Interactive Rendering by Eric Haines, [email protected] [near-final draft, 9/23/05, for IEEE CG&A January/February 2006, p. 76-87] Abstract: The past decade has seen major improvements, in both speed and quality, in the area of interactive rendering. The focus of this article is on the evolution of the consumer-level personal graphics processor, since this is now the standard platform for most researchers developing new algorithms in the field. Instead of a survey approach covering all topics, this article covers the basics and then provides a tour of some parts the field. The goals are a firm understanding of what newer graphics processors provide and a sense of how different algorithms are developed in response to these capabilities. Keywords: graphics processors, GPU, interactive, real-time, shading, texturing In the past decade 3D graphics accelerators for personal computers have transformed from an expensive curiosity to a basic requirement. Along the way the traditional interactive rendering pipeline has undergone a major transformation, from a fixed- function architecture to a programmable stream processor. With faster speeds and new functionality have come new ways of thinking about how graphics hardware can be used for rendering and other tasks. While expanded capabilities have in some cases simply meant that old algorithms could now be run at interactive rates, the performance characteristics of the new hardware has also meant that novel approaches to traditional problems often yield superior results. The term “interactive rendering” can have a number of different meanings. Certainly the user interfaces for operating systems, photo manipulation capabilities of paint programs, and line and text display attributes of CAD drafting programs are all graphical in nature. -

Texture Mapping

Texture Mapping University of Texas at Austin CS354 - Computer Graphics Spring 2009 Don Fussell What adds visual realism? Geometry only Phong shading Phong shading +! Texture maps University of Texas at Austin CS354 - Computer Graphics Don Fussell Textures Supply Rendering Detail Without texture With texture CS 354 Textures Make Graphics Pretty Unreal Tournament Sacred 2 Texture → detail, detail → immersion, immersion → fun CS 354 Microsoft Flight Simulator X Texture mapping Texture mapping (Woo et al., fig. 9-1) Texture mapping allows you to take a simple polygon and give it the appearance of something much more complex. Due to Ed Catmull, PhD thesis, 1974 Refined by Blinn & Newell, 1976 Texture mapping ensures that “all the right things” happen as a textured polygon is transformed and rendered. University of Texas at Austin CS354 - Computer Graphics Don Fussell Non-parametric texture mapping With “non-parametric texture mapping”: Texture size and orientation are fixed They are unrelated to size and orientation of polygon Gives cookie-cutter effect University of Texas at Austin CS354 - Computer Graphics Don Fussell Parametric texture mapping With “parametric texture mapping,” texture size and orientation are tied to the polygon. Idea: Separate “texture space” and “screen space” Texture the polygon as before, but in texture space Deform (render) the textured polygon into screen space A texture can modulate just about any parameter – diffuse color, specular color, specular exponent, … University of Texas at Austin CS354 - Computer Graphics Don Fussell Implementing texture mapping A texture lives in it own abstract image coordinates parameterized by (u,v) in the range ([0..1], [0..1]): It can be wrapped around many different surfaces: Computing (u,v) texture coordinates in a ray tracer is fairly straightforward. -

GPU Benchmarking - for Handsets from a UI Perspective

GPU Benchmarking - for handsets from a UI perspective ERIK BÄCKSTRÖM KRISTIAN SYLWANDER Master’s Thesis at LTH Supervisor: Fredrik Ademar Examiner: Micheal Doggett Abstract The graphical processing unit (GPU) is becoming an essential part of mo- bile phones and handsets. This improves the ability of handling graphics in handsets significantly. With this new chip it becomes possible to develop new stunning games but also new innovative 3D GUI (Graphical User Interfaces). Today there exist a couple of benchmarking programs targeting mobile GPUs but all of these benchmarking tools are all focused on game performance and not GUI performance. The aim with this master’s thesis is to develop a bench- marking program for mobile GPUs focusing on GUI performance. We have identified five features that are important when benchmarking a handset, from a GUI perspective: scissoring, texture uploads, alpha blending, load times and frame rate. Additionally, we have benchmarked five different devices using our tool. From the test we could conclude that there were big differences in the performance compared to the specification sheets. Acknowledgement This master thesis is done as a completing part of our education at LTH (Lund Institute of Technology) with focus on computer science. During the course of our master thesis we have received invaluable supervision and help from a number of persons both at TAT and at LTH. Therefore we would like to take the opportunity to thank these persons for their advise, knowledge and dedi- cation. First we would like to thank our supervisors at TAT Fredrik Ademar, Fredrik Berglund and Dan Gärdenfors. We also want to thank Michael Dog- gett, our examiner at LTH.