Lecture 26: Wrap-Up

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Apple Ipad Pro Wi-Fi Cellular 10.5" 512GB Guld Apple Ios 12 Beskrivelse Apple Ipad Pro 10.5" Wifi + 4G 512GB - Gold

Apple iPad Pro Wi-Fi Cellular 10.5" 512GB Guld Apple iOS 12 Beskrivelse Apple iPad Pro 10.5" WiFi + 4G 512GB - Gold Features Den mest avancerede skærm på hele kloden iPad har altid været den ultimative Multi-Touch-oplevelse. Og den redesignede Retina-skærm på iPad Pro sætter en helt ny standard. Ikke alene har den højere lysstyrke og mindre genskin - den har også langt hurtigere reaktionstid end nogen forgænger. Uanset om du scroller løs i Safari eller spiller tunge 3D-spil, går alt så utroligt jævnt og hurtigt, at du helt sikkert bliver revet med. Stærkere end de fleste computere A10X Fusion-chippen med 64-bit-arkitektur og seks kerner giver dig masser af power mellem hænderne. Så meget at du kan redigere 4K-video på farten. Rendere en detaljeret 3D-model. Eller oprette og markere i komplekse dokumenter og præsentationer. Helt nemt - og på en enhed, der stadig har batteritid til en hel dag. Yderst spidskompetent iPad Pro-skærmens opdateringsfrekvens er blevet forbedret, så Apple Pencil gengiver dine strøg endnu mere præcist og naturligt. Apple Pencil er det eneste digitale skriveredskab, der giver dig mulighed for at skrive, lave markeringer og tegne med så præcist et pixel-niveau. Et kæmpe spring for iPad iOS 11 får alt på din iPad til at virke mere levende end nogensinde før. De nye funktioner og muligheder gør, at du kan endnu mere, både hurtigere og nemmere, så du får en endnu mere personlig iPad-oplevelse med masser af power. Brug den til lige præcis det, du vil. For det kan du nu. -

CIS Apple Ios 12 Benchmark

CIS Apple iOS 12 Benchmark v1.0.0 - 10-19-2018 Terms of Use Please see the below link for our current terms of use: https://www.cisecurity.org/cis-securesuite/cis-securesuite-membership-terms-of-use/ 1 | P a g e Table of Contents Terms of Use ........................................................................................................................................................... 1 Overview .................................................................................................................................................................. 7 Intended Audience ........................................................................................................................................... 7 Consensus Guidance ........................................................................................................................................ 7 Scoring Information ........................................................................................................................................ 9 Profile Definitions ......................................................................................................................................... 10 Acknowledgements ...................................................................................................................................... 11 Recommendations ............................................................................................................................................. 12 1 Benchmark Guidance .............................................................................................................................. -

Ipad Pro 10.5" Teardown Guide ID: 92534 - Draft: 2021-05-12

iPad Pro 10.5" Teardown Guide ID: 92534 - Draft: 2021-05-12 iPad Pro 10.5" Teardown Teardown of the iPad Pro 10.5" performed on June 13, 2017. Written By: Adam O'Camb This document was generated on 2021-05-15 05:56:18 PM (MST). © iFixit — CC BY-NC-SA www.iFixit.com Page 1 of 18 iPad Pro 10.5" Teardown Guide ID: 92534 - Draft: 2021-05-12 INTRODUCTION Apple is at it again, trying to win over the workforce with yet another iPad Pro (this time with a brand- new 10.5" screen size). We expect to see Apple put points on the board with some silicon slam dunks, but what else puts this Pro in the big leagues? Is this new iPad a knock out of the park or is it just KO'd? Only one way to know! Let's play ball tear it down! Care to keep up? We do move fast, but we love our teammates. Stay in the race by following us on Facebook, Instagram, or Twitter for the latest teardown news. [video: https://www.youtube.com/watch?v=DepdFt8ZxNc] TOOLS: iOpener (1) Suction Handle (1) iFixit Opening Picks set of 6 (1) Phillips #00 Screwdriver (1) Halberd Spudger (1) Plastic Cards (1) Tweezers (1) iPad Battery Isolation Pick (1) This document was generated on 2021-05-15 05:56:18 PM (MST). © iFixit — CC BY-NC-SA www.iFixit.com Page 2 of 18 iPad Pro 10.5" Teardown Guide ID: 92534 - Draft: 2021-05-12 Step 1 — iPad Pro 10.5" Teardown You can relax now—this iPad is a professional. -

Information Display Magazine May/June 2018 Vol 34 No 3 2018

THE FUTURE LOOKS RADIANT ENSURING QUALITY FOR THE NEXT GENERATION OF DISPLAY DEVICES Radiant light & color measurement solutions replicate human visual perception to evaluate how users will experience new technology including OLED and microLED displays. Visit us at Booth #729 Display Week 2018 May 22-24 | Los Angeles, CA ID TOC Issue3 p1_Layout 1 4/25/2018 7:12 AM Page 1 Information SOCIETY FOR INFORMATION DISPLAY SID MAY/JUNE 2018 2018 DISPLAY VOL. 34, NO. 3 ON THE COVER: The winners of this year’s Display Industry Awards are, clockwise from upper right: Sharp’s 70-in. 8K LCD TV; LG Displays’ UHD Crystal Sound OLED; contents Apple’s iPhone X; Apple’s iPad Pro Display; Synaptics’ Clear ID Optical In-Display 2 Editorial: Return to Southern California Fingerprint Sensor; Kolon’s Colorless Polyimide; n By Stephen Atwood and Continental Automotive Systems’ 3D Touch Surface Display. 4 President’s Corner: What’s Next (in Display Technology)? 6 Industry News n By Jenny Donelan 8 2018 Display Industry Awards: This Year’s Winners Are a Fun and Compelling Group Each year, SID’s Display Industry Awards Committee selects products that have advanced the state of the art of display technology in the categories of Display of the Year, Display Component of the Year, and Display Application of the Year. n Compiled by Jenny Donelan 12 Display History: David Sarnoff, Display Industry Visionary His many contributions to the display industry are closely linked to the pioneering of Cover Design: Jodi Buckley flat-panel displays and the invention and eventual success of the LCD. -

Current Verizon Equipment Offers (Pdf)

Limited time offers. Qualifying Government Customers COMPARE AND SAVE ON OUR LATEST DEVICES. SmartPhone Accessory Bundle w/ Tempered Glass SmartPhone Memory Accessory Bundle w/ Tempered Glass Save up to 39% Save up to 39% Car Charger (up to $49.99) 64 GB MicroSD Card (up to $49.99) Case (up to $49.99) Case (up to $49.99) Glass Display Protector (up to $49.99) Glass Display Protector (up to $49.99) $89.99 $89.99 SmartPhone Accessory Combination SmartPhone Basic Accessory Combination Car Charger (up to $29.99) Car Charger (up to $29.99) - Not available for Type C USB Case (up to $49.99) Case (up to $29.99) Vinyl Screen Scratch Protector (up to $12.99) Vinyl Screen Scratch Protector (up to $12.99) $69.72 - Available for most phone models $54.72 - Available for select phone models **Portable Power Pack Promo (39% savings)** **Portable Power Pack Promo (45% savings)** Get 3 Portable Power Packs for $89.99 Get 3 Portable Power Packs for $129.99 regularly priced at $49.99 each (hyperlink) regularly priced at $79.99 each (hyperlink) SmartPhone Accessories BlueTooth Headset Car Charger $22.49 - $29.99 Shell Holster Case $22.49 Rugged Case $37.49 - $44.99 Glass Screen Protector $18.74 - $33.74 Explorer 500 $44.99 LG Tone Ultra $99.99 Reflects typcial pricing - some models may vary MicroSD Memory Card - Expand the capacity of your SmartPhone Network Extender Item may differ from picture 32 GB (SDSDQUP-032G-V46A) $39.99 Consumer/Small Business Class $249.99 64 GB (SDSDQUP-064G-V46A) $49.99 Enterprise Class $2,999.99 (30,000 sqft) 128 GB (SDSDQUP-128G-V46A) $99.99 Accessory selection may vary by phone model. -

Security Policy Module Version 10.0

Apple Inc. Apple corecrypto User Space Module for ARM (ccv10) FIPS 140-2 Non-Proprietary Security Policy Module Version 10.0 Prepared for: Apple Inc. One Apple Park Way Cupertino, CA 95014 www.apple.com Prepared by: atsec information security Corp. 9130 Jollyville Road, Suite 260 Austin, TX 78759 www.atsec.com ©2021 Apple Inc. This document may be reproduced and distributed only in its original entirety without revision Trademarks Apple’s trademarks applicable to this document are listed in https://www.apple.com/legal/intellectual- property/trademark/appletmlist.html. Other company, product, and service names may be trademarks or service marks of others. Last update: 2021-03-17 ©2021 Apple Inc. Version: 1.4 Page 2 of 31 Table of Contents 1 Introduction .............................................................................. 5 2 Purpose .................................................................................... 5 2.1 Document Organization / Copyright ............................................................................................. 5 2.2 External Resources / References .................................................................................................. 5 2.2.1 Additional References .......................................................................................................... 5 2.3 Acronyms ...................................................................................................................................... 7 3 Cryptographic Module Specification ......................................... -

Apple Ipad Pro Wi-Fi 12.9" 256GB Sølv Apple Ios 12 Description U Apple Ipad Pro 12.9" 2017 Wifi 256GB - Silver

Apple iPad Pro Wi-Fi 12.9" 256GB Sølv Apple iOS 12 Description U_Apple iPad Pro 12.9" 2017 WiFi 256GB - Silver Features Passer til selv dine allerstørste idéer Med sin Retina-skærm på 5,6 millioner pixels er iPad Pro den iOS-enhed, der har den højeste skærmopløsning. Den 12,9" store skærm gør alt, hvad du gør - redigering af 4K-video, design af præsentationer, drift af en virksomhed - lettere, hurtigere og mere involverende. Og Multi-Touch- undersystemet har fået nyt design, som giver dig flere måder at interagere med iPad på. Oplevelsen bliver bedre for hvert tryk iOS 9 er verdens mest intuitive, avancerede og sikre mobile styresystem. Det hjælper dig til at blive mere produktiv og kreativ takket være de nye funktioner, som udnytter iPad Pro's store ydeevne fuldt ud. Multitasking gør det nemt at have to apps kørende på samme tid. Og iPad kan bruges til endnu mere takket være forbedrede funktioner på tværs af systemet som f.eks. Siri og Spotlight-søgning. Hvis det føles, som om iOS 9 og iPad Pro er designet til at arbejde sammen, så er der noget om snakken. Det er de nemlig. Når der er mere iPad, kan dine apps også mere iPad Pro leveres med en række indbyggede apps, som gør de ting, du gør hver dag, nemmere. Og i App Store kan du finde utrolige apps, som er specialdesignet til iPad, så der næsten ikke er grænser for, hvad du kan. Stor på næsten alle måder Selv med iPad Pro's store skærm er det lykkedes at lave et utroligt tyndt og let design. -

Uložte Si Své Vzpomínky!

Nejširší distribuční síť Dodání do 20 000 produktů hardware v ČR a SR 24 hodin! skladem! ŘÍJEN 2018 Uložte si své vzpomínky! Připomínáme si 100. výročí vzniku samostatného Československa Ke stoletému výročí rozdáváme k našim akčním produktům také hodnotné dárky pouze za 100 Kč NOVINKA NA TRHU DÁREK V HODNOTĚ 2 000 KČ DÁREK ZA 100 Kč DÁREK ZA 100 Kč DÁREK ZA 100 Kč 519012 64GB Micro (SDXC) Card i-stay Black Up to 12" iPad Tristar RD1548 AudioSonic 519011 (Kód: 443110) 1026490 Tablet (Kód: 848000) 518534 (Kód: 821220) Mobilní telefon iPad Notebook ASUS ZENFONE 2 990,- APPLE IPAD PRO 10.5‘‘ 22 490,- HP 15-RB014NC 7 990,- LIVE L1 - DUAL SIM WI-FI + CELLULAR 64GB Mobilní telefon 5.5" HD+ 1440x720 • procesor Qualcomm Snapdragon Tablet Apple A10X s 64bitovou architekturou a pohybovým koprocesorem Notebook - AMD Dual Core E2-9000e • 15.6" LED 1366x768 antireflexní 425 Quad Core • RAM 2GB • interní paměť 16GB • Triple Slot (Dual SIM M10 • multidotykový Retina 10,5" LED 2224x1668 • interní paměť 64GB • RAM 4GB DDR4 • AMD Radeon R2 • HDD 500GB 5400 otáček • DVD + MicroSDXC až 2TB) • fotoaparát zadní 13Mpx (F/2.0) • fotoaparát přední • WiFi 802.11ac • Bluetooth 4.2 • 3G/LTE modem (nano SIM) • 2x • WiFi 802.11a/b/g/n • Bluetooth 4.0 • Webkamera • čtečka karet 5Mpx (F/2.4) • GPS • Glonass • LTE • microUSB • baterie 3000 mAh webkamera • 4x reproduktory • Touch ID • Lightning konektor • iOS 10 • USB 3.1 • HDMI • TPM • Windows 10 Home 64bit • Android 8.0 + ZenUI 5 Vše můžete objednat u nejbližšího eD PROFI partnera. Seznam na www.edprofi.cz Vše můžete objednat u nejbližšího eD PROFI partnera. -

Lote 3 Ordenadores De Sobremesa Y Portátiles Con Sistema Operativo Macos Y Tablets Apple Con Sistema Operativo Ios (Mac)

LOTE 3 ORDENADORES DE SOBREMESA Y PORTÁTILES CON SISTEMA OPERATIVO MACOS Y TABLETS APPLE CON SISTEMA OPERATIVO IOS (MAC) EMPRESA LICITADORA: CLEVISA, S.L. CIF: B28639896 FABRICANTE: APPLE Junio 2018 ACUERDO MARCO PARA EL SUMINISTRO DE EQUIPAMIENTO INFORMÁTICO EN LA UNIVERSIDAD COMPLUTENSE DE MADRID Y EN LA FUNDACIÓN GENETAL DE LA UNIVERSIDAD COMPLUTENSE DE MADRID (EXPEDIENTE AM 15/18) 1 LOTE 3 – ORDENADORES DE SOBREMESA Y PORTÁTILES CON SISTEMA OPERATIVO MACOS Y TABLETS APPLE CON SISTEMA OPERATIVO IOS (MAC) 3.1 PERFIL IMAC Todo más rápido para hacer más rápido todo Ahora más rápida y poderosa que nunca, el iMac está equipado con procesadores potentes y los gráficos de alto rendimiento. Ahora podrás hacer todo a máxima velocidad. La capacidad de ser rápido e inteligente El almacenamiento es un tema de espacio, pero también de velocidad. Las apps y los archivos que más usas se guardan automáticamente en el almacenamiento flash, y todo lo demás pasa a un disco duro de alta capacidad. Con Fusion Drive, todo es más rápido y eficiente, desde iniciar el equipo hasta abrir apps o importar fotos. Gráficos que animarán tus sentidos La potencia interna de la iMac se transforma en imágenes increíbles. Gracias al potente procesador gráfico, cada día de trabajo es un espectáculo. La realidad virtual en la iMac se hizo realidad Ya podrás editar video de 360° y también crear contenido de realidad virtual 3D. ACUERDO MARCO PARA EL SUMINISTRO DE EQUIPAMIENTO INFORMÁTICO EN LA UNIVERSIDAD COMPLUTENSE DE MADRID Y EN LA FUNDACIÓN GENETAL DE LA UNIVERSIDAD COMPLUTENSE DE MADRID (EXPEDIENTE AM 15/18) 2 Mil millones de colores para que tu trabajo deslumbre Con 1,000 millones de colores y 500 nits de brillo, los gráficos tienen una definición extraordinaria. -

Content-Aware Internet Video Delivery

Neural Adaptive Content-aware Internet Video Delivery Hyunho Yeo, Youngmok Jung, Jaehong Kim, Jinwoo Shin, Dongsu Han 2 Observation on Current Video Ecosystem Adaptive streaming has been widely deployed (a primary tool for improving user QoE) Video server Client Quality Bandwidth Quality High ABR Medium Low Time Time Time 3 Traditional Approaches Optimizing ABR algorithms Pensieve [SIGCOMM 17], MPC [SIGCOMM 15] Choosing better servers, CDNs Content Multihoming [SIGCOMM 12], VDN [SIGCOMM 15] Leveraging centralized control plan Video Control Plane [SIGCOMM 12], Pythease [NSDI 17] Goal: Find how to best utilize the network resource 4 Limitation of Current Video Delivery Video quality heavily depends on available bandwidth Video server Client Network Low Quality Congestion Directly affect 5 Limitation of Current Video Delivery Client computing power is scarcely utilized other than for decoding Mobile GPU Desktop GPU 500 Apple A10X 12 Apple A9X Apple A10 GTX 1080Ti 375 Apple A8X GTX 1080 9 GTX 980Ti Apple A7 GTX 780Ti 250 Apple A6X 6 GTX 780 (TFLOPs) (GFLOPs) 125 Apple A5 Apple A9 3 GTX 480 Apple A4 Apple A8 GTX 680 GTX 980 Apple A6 GTX 580 Computing Computing power Computing Computing power 0 0 2009 2012 2015 2018 2009 2012 2015 2018 Year Year 6 Observation on Current Video Ecosystem Standard codecs efficiently reduce redundancy inside GOP Group of Pictures (GOP) Video Standard codecs (H.26x, VPx, AV1) Compressed : Intra-frame coding : Inter-frame coding I-frame P-frames I-frame 7 Observation on Current Video Ecosystem Standard codecs efficiently -

National Information Assurance Partnership Common Criteria

National Information Assurance Partnership Common Criteria Evaluation and Validation Scheme ® TM Validation Report for the Apple iOS 14 and iPadOS 14: Contacts Report Number: CCEVS-VR-VID11191-2021 Dated: August 20, 2021 Version: 1.0 National Institute of Standards and Technology Department of Defense Information Technology Laboratory ATTN: NIAP, SUITE: 6982 100 Bureau Drive 9800 Savage Road Gaithersburg, MD 20899 Fort Meade, MD 20755-6982 ACKNOWLEDGEMENTS Validation Team Patrick Mallett, Ph.D. Jerome Myers, Ph.D. DeRon Graves Seada Mohammed J David D Thompson The Aerospace Corporation Common Criteria Testing Laboratory Kenji Yoshino Thibaut Marconnet Acumen Security, LLC 2 Table of Contents 1 Executive Summary ............................................................................................................... 4 2 Identification .......................................................................................................................... 5 3 Architectural Information .................................................................................................... 6 4 Security Policy........................................................................................................................ 7 4.1 Cryptographic Support .................................................................................................................................. 7 4.2 User Data Protection ..................................................................................................................................... -

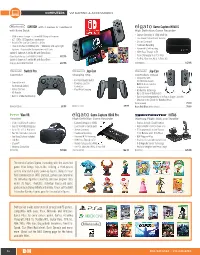

Vive VR Joy-Con Joy-Con HOTAS Game Capture HD60 Pro Switch

COMPUTERS VR GAMING & ACCESSORIES SWITCH with 2 Games & 1 amiibo Kit Game Capture HD60 S with Extra Dock High Definition Game Recorder Capture Gameplay in 1080p at 60 fps 32GB Internal Storage Custom NVIDIA Tegra Processor 6.2” 1280 x 720 Capacitive Touchscreen Live Stream to Twitch and YouTube Includes Two Joy-Con Controllers & Grip Stream Command Three to Six Hours of Battery Life Wirelessly Link up to Eight Flashback Recording Systems Expandable Storage via microSD Cards Advanced H.264 Encoding Switch 2 Games & 1 amiibo Kit with Extra Dock HDMI Pass-Through to TV (Neon Blue & Red Joy-Con (NISWITCHNBRB .................................... 417.55 Record Gameplay to a PC or Mac Switch 2 Games & 1 amiibo Kit with Extra Dock For PS4, Xbox One, Wii U, & Xbox 360 (Gray Joy-Con (NISWITCHGYCB ........................................................ 417.55 ELGCHD60S.....................................................................................167.95 Switch Pro Joy-Con Joy-Con Controller Charging Grip Controllers (Gray) Compatible with For the Nintendo Switch the Nintendo Switch Compatible with Combines Joy-Con Built-In Accelerometer the Nintendo Switch Controllers & Gyro-Sensor Motion Controls Play While Charging HD Rumble Technology HD Rumble Up to 20 Hours of Battery Life Built-In amiibo Functionality Can be Used Independently or in Grip as Single Controller Attaches to the Switch for Handheld Mode NIHACAJAAAA ....................................................................................79.99 NIHACAFSSKA