DM3730, DM3725 Digital Media Processors Datasheet (Rev. D)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

User Manual - S.USV Solutions Compatible with Raspberry Pi, up Board and Tinker Board Revision 2.2 | Date 07.06.2018

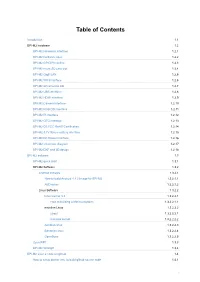

User Manual - S.USV solutions Compatible with Raspberry Pi, UP Board and Tinker Board Revision 2.2 | Date 07.06.2018 User Manual - S.USV solutions / Revision 2.0 Table of Contents 1 Functions .............................................................................................................................................. 3 2 Technical Specification ........................................................................................................................ 4 2.1 Overview ....................................................................................................................................... 5 2.2 Performance .................................................................................................................................. 6 2.3 Lighting Indicators ......................................................................................................................... 6 3 Installation Guide................................................................................................................................. 7 3.1 Hardware ...................................................................................................................................... 7 3.1.1 Commissioning S.USV ............................................................................................................ 7 3.1.2 Connecting the battery .......................................................................................................... 8 3.1.3 Connecting the external power supply ................................................................................. -

A Highly Modular Router Microarchitecture for Networks-On-Chip

A Highly Modular Router Microarchitecture for Networks-on-Chip Item Type text; Electronic Dissertation Authors Wu, Wo-Tak Publisher The University of Arizona. Rights Copyright © is held by the author. Digital access to this material is made possible by the University Libraries, University of Arizona. Further transmission, reproduction, presentation (such as public display or performance) of protected items is prohibited except with permission of the author. Download date 01/10/2021 08:12:16 Link to Item http://hdl.handle.net/10150/631277 A HIGHLY MODULAR ROUTER MICROARCHITECTURE FOR NETWORKS-ON-CHIP by Wo-Tak Wu Copyright c Wo-Tak Wu 2019 A Dissertation Submitted to the Faculty of the DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING In Partial Fulfillment of the Requirements For the Degree of DOCTOR OF PHILOSOPHY In the Graduate College THE UNIVERSITY OF ARIZONA 2019 THE UNIVERSITY OF ARIZONA GRADUATE COLLEGE As members of the Dissertation Committee, we certify that we have read the dissertation prepared by Wo-Tak Wu, titled A HIGHLY MODULAR ROUTER MICROARCHITECTURE FOR NETWORKS-ON-CHIP and recommend that it be accepted as fulfilling the dissertation requirement for the Degree of Doctor of Philosophy. Dr. Linda Powers --~-__:::::____ ---?---- _________ Date: August 7, 2018 Dr. Roman Lysecky Final approval and acceptance of this dissertation is contingent upon the candidate's submission of the final copies of the dissertation to the Graduate College. I hereby certify that I have read this dissertation prepared under my direction and recommend that it be accepted as fulfilling the dissertation requirement. _____(/2 __·...... ~"--------\;-~=--------- · __ Date: August 7, 2018 Dissertation Director: Dr. -

FD-V15N3.Pdf

SILICON COMPOSERS INC FAST Forth Native-Language Embedded Computers DUP >R R> Harris RTX 2000"" l&bit Forth Chip SC32"" 32-bit Forth Microprocessor 08 or 10 MHz operation and 15 MIPS speed. 08 or 10 MHz operation and 15 MIPS speed. 1-cycle 16 x 16 = 32-bi multiply. 1-clock cycle instruction execution. 1-cycle 1&prioritized interrupts. *Contiguous 16 GB data and 2 GB code space. *two 256-word stack memories. *Stack depths limited only by available memory. -&channel 1/0 bus & 3 timer/counters. *Bus request/bus grant lines with on-chip tristate. SC/FOX PCS (Parallel Coprocessor System) SC/FOX SBC32 (Single Board Computer32) *RTX 2000 industrial PGA CPU; 8 & 10 MHz. 032-bi SC32 industrial grade Forth PGA CPU. *System speed options: 8 or 10 MHz. *System speed options: 8 or 10 MHz. -32 KB to 1 MB 0-wait-state static RAM. 42 KB to 512 KB 0-wait-state static RAM. *Full-length PC/XT/AT plug-in (&layer) board. .100mm x 160mm Eurocard size (+layer) board. SC/FOX VME SBC (Single Board Computer) SC/FOX PCS32 (Parallel Coprocessor Sys) *RTX 2000 industrial PGA CPU; 8, 10, 12 MHz. 032-bi SC32 industrial grade Forth PGA CPU. *Bus Master, System Controller, or Bus Slave. *System speed options: 8 or 10 MHz. Up to 640 KB 0-wait-state static RAM. 064 KB to 1 MB 0-wait-state static RAM. -233mm x 160mm 6U size (Slayer) board. *FulClength PC/XT/AT plug-in (Slayer) board. SC/FOX CUB (Single Board Computer) SC/FOX SBC (Single Board Computer) *RTX 2000 PLCC or 2001A PLCC chip. -

New Suppliers Presentation

TechTalk Rutronik´s New Embedded Suppliers: Introduction of Rutronik´s New Partners and Suppliers on the Linecard to meet your Challenges of the Future Bernd Hantsche Cypress Semiconductor is now part of Infineon Infineon is now a Wireless supplier offering following solutions: • Wireless System-on-Chip (Transceiver + Wireless-Stack + your application code, no further MCU required) • WiFi Dual-Band, 1x1 SISO or 2x2 MIMO • Bluetooth Basic Data Rate and Enhanced Data Rate (also known as „classic Bluetooth“) • Bluetooth Low Energy • Bluetooth Dual-Mode (BR/EDR + LE) • WiFi Dual-Band + Bluetooth Dual Mode combination (single chip design) • Wireless Connectivity Chips (Transceiver + Wireless-Stack, external MCU for your application code required) • WiFi Dual-Band, 1x1 SISO or 2x2 MIMO • automotive qualified wireless solutions 3 4 Rutronik offers corresponding Cypress based modules from MURATA • ultra small • safe design cost • safe certification cost • faster time-to-market • less design and logistic complexitity • radio only • connectivity • System-on-Module • Bluetooth Low Energy • Bluetooth Dual-Module • WiFi • WiFi + Bluetooth Dual Mode Do you want to learn more regarding Cypress / Infineon / Murata? [email protected] 5 4D Systems Turning Technology into Art Privately held, est. 1990 HQ, R&D and manufacturing in Australia, regional offices Austria, China, Philippines, Turkey Global leader in intelligent graphic TFT & OLED display module solutions • Smart displays (integrated graphic processor with graphic libraries) • Non-touch devices, -

Banana Pi BPI-M2 A31s Quad Core Single Board Computer

Table of Contents Introduction 1.1 BPI-M2 hardware 1.2 BPI-M2 Hardware interface 1.2.1 BPI-M2 hardware spec 1.2.2 BPI-M2 GPIO Pin define 1.2.3 BPI-M2 micro SD card slot 1.2.4 BPI-M2 GigE LAN 1.2.5 BPI-M2 WIFI interface 1.2.6 BPI-M2 wifi antenna slot 1.2.7 BPI-M2 USB interface 1.2.8 BPI-M2 HDMI interface 1.2.9 BPI-M2 Camera interface 1.2.10 BPI-M2 RGB DSI interface 1.2.11 BPI-M2 IR interface 1.2.12 BPI-M2 OTG interface 1.2.13 BPI-M2 CE FCC RoHS Certification 1.2.14 BPI-M2 3.7V lithium battery interface 1.2.15 BPI-M2 DC Power interface 1.2.16 BPI-M2 schematic diagram 1.2.17 BPI-M2 DXF and 3D design 1.2.18 BPI-M2 software 1.3 BPI-M2 quick start 1.3.1 BPI-M2 Software 1.3.2 Android software 1.3.2.1 How to build Android 4.4.2 Image for BPI-M2 1.3.2.1.1 ABD driver 1.3.2.1.2 Linux Software 1.3.2.2 Linux kernel 3.3 1.3.2.2.1 How to building a Minimal system 1.3.2.2.1.1 mainline Linux 1.3.2.2.2 uboot 1.3.2.2.2.1 mainline kernel 1.3.2.2.2.2 Armbian linux 1.3.2.2.3 Bananian linux 1.3.2.2.4 OpenSuse 1.3.2.2.5 OpenWRT 1.3.3 BPI-M2 WiringPi 1.3.4 BPI-M2 source code on github 1.4 How to setup docker env. -

ISEE Igepv2 BOARD

ISEE IGEPv2 BOARD IGEPv2 BOARD SDK USER MANUAL (Revision 1.02) ISEE (Integration Software & Electronics Engineering ) Crta. De Martorell 95, Local 7 – Terrassa (08224) – Barcelona – SPAIN. +34.93.789.12.71 [email protected] www.iseebcn.com IGEPv2 SDK USER MANUAL v1.02 2 CONTENTS 0 COPYRIGHT NOTICE ................................................................................ 4 1 PREFACE ................................................................................................ 5 1.1 VERY QUICK START GUIDE ................................................................. 5 1.2 ORGANIZATION OF THE MANUAL ........................................................ 6 1.3 MYIGEP ECOSYSTEM .......................................................................... 6 1.4 Useful web LINKS and emails .............................................................. 6 1.5 User registration ............................................................................... 7 2 INTRODUCING IGEPv2 board .................................................................... 8 2.1 IGEPv2 board SDK features ................................................................ 8 2.2 GET your IGEPv2 board POWER ON ..................................................... 9 3 IGEP v2 SDK virtual machine ................................................................... 13 3.1 Why SDK in a virtual machine? .......................................................... 13 3.2 Download SDK virtual machine .......................................................... 13 3.3 Virtual -

PN7150 Beaglebone Black SBC Kit Quick Start Guide Rev

AN11842 PN7150 BeagleBone Black SBC kit quick start guide Rev. 1.3 — 14 June 2021 Application note 373113 COMPANY PUBLIC Document information Information Content Keywords OM5579, PN7150, BeagleBone, NFC, P2P, card emulation, Linux, Android Abstract This document gives a description on how to get started with the OM5579 PN7150 NFC controller SBC kit on BeagleBone Black platform. NXP Semiconductors AN11842 PN7150 BeagleBone Black SBC kit quick start guide 1 Revision history Revision history Rev Date Description 1.3 20210614 Moved to OM5579 because of OM5578 discontinuation 1.2 20180725 Updated weblinks 1.1 20170222 Updated demo images weblinks 1.0 20150518 First official release version AN11842 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2021. All rights reserved. Application note Rev. 1.3 — 14 June 2021 COMPANY PUBLIC 373113 2 / 17 NXP Semiconductors AN11842 PN7150 BeagleBone Black SBC kit quick start guide 2 Introduction This document gives a description on how to get started with the OM5579 PN7150 NFC controller SBC kit on BeagleBone Black platform. This document provides a step by step guide to the installation procedure of the hardware and the software. Finally, it shows PN7150 NFC controller functionalities through demonstration application. OM5579/PN7150 demonstration kit replaces previous OM5578/PN7150 demonstration kit now discontinued. 2.1 OM5579/PN7150BBB demo kit OM5579/PN7150BBB kit is a high performance fully NFC-compliant expansion board for BeagleBone Black (refer to [1] for more details). It meets compliance with Reader mode, P2P mode and card emulation mode standards. The board features an integrated high- performance RF antenna to insure high interoperability level with NFC devices. -

Cubieboard5 SKU: 10000 Category: Board Description General Details Documents

CubieBoard5 SKU: 10000 Category: Board Description General Details Documents Description Cubieboard5 is the 5rd generation product of CubieBoard series from Cubietech Limited Company, and it’s the updated version of CubieBoard3. Thanks to Allwinnertech’ H8 SOC, Compared with CubieBoard3 the performance has been increased by 4 times. CubieBoard5 is open source hardware, single board computer, or development board which targets Developers, Geeks, Makers, Students… CubieBoard5 is also can be used as low power industry computer in all works of life since we have designed a very sturdy and durable metallic enclosure for it which named CubieTruck Plus Metal case. In this case, not only the CubieBoard5 main board can be installed, but also the 2.5 inch HDD/SSD and 5300mAh Li-Po battery. With the HDD and battery, the CubieBoard5 is more suitable for industry applications. Because of open source strategy of our company, the CubieBoard5’s application space is more flexible, and the ecology is more perfect. Product Information Name: Cubieboard5, CB5 for short, Also named CubieTruck plus as MiniPc Property: Software open source, Hardware open, Production materials closed Owner: CubieTech Limited Chipset: Allwinner technology H8, Arm architecture Cortex-A7 octa-core SOC System: Android, Ubuntu and many other open source distribution… Target: Developer, Geek, Maker, Scholar, Student… Product Introduction Cubieboard5 is the updated version of CubieBoard3 open source hardware. It’s a new PCB model adopted with Allwinner H8 main chip. And it is enhanced with some features, such as 2GB DDR3 memory, DP display port on-board, 100M/1000M RJ45, WIFI+BT on-board, support Li-battery and RTC battery, SPDIF audio interface. -

Arduino Tips, Tricks, and Techniques Created by Lady Ada

Arduino Tips, Tricks, and Techniques Created by lady ada Last updated on 2019-04-24 09:36:52 PM UTC Arduino UNO FAQ There's so many Arduino's out there, it may get a little confusing. We wanted to clarify for people some of the changes in the latest version. NB this is just our opinion and interpretation of some of the decisions made by Arduino. We aren't associated with Arduino, and don't speak for them! If you have to get an Official Response to your Arduino question please contact them directly. Thx! NB2 Still in progress, we're collecting common questions to answer. If you have more questions, please post them in our forums (https://adafru.it/forums). Arduino Timeline But first…some history! First there was the serial Arduino (what's the name of it?) with RS232 which was not used outside of the Arduino team & friends. The first popularly manufactured Arduino was called the NG (New Generation, like Star Trek, yknow?) The NG used the Atmega8 chip running at 16 MHz and an FT232 chip for the USB interface. The bootloader takes up 2KB of space and runs at 19200 baud. The next version was the Diecimila. The Diecimila updated the chip from the Atmega8 to the Atmega168. The great thing here is double the space and memory (16K instead of 8K). It still ran at 16MHz. The Diecimila also added two extra header pins for 3.3V (from the FTDI chip) and the reset pin which can be handy when a shield is covering up the Reset button. -

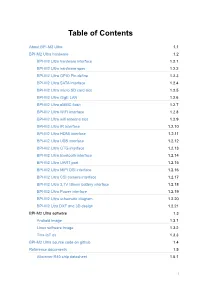

Banana Pi BPI-M2 Ultra Allwinner R40 Quad Core Single Board Computer

Table of Contents About BPI-M2 Ultra 1.1 BPI-M2 Ultra hardware 1.2 BPI-M2 Ultra hardware interface 1.2.1 BPI-M2 Ultra hardware spec 1.2.2 BPI-M2 Ultra GPIO Pin define 1.2.3 BPI-M2 Ultra SATA interface 1.2.4 BPI-M2 Ultra micro SD card slot 1.2.5 BPI-M2 Ultra GigE LAN 1.2.6 BPI-M2 Ultra eMMC flash 1.2.7 BPI-M2 Ultra WIFI interface 1.2.8 BPI-M2 Ultra wifi antenna slot 1.2.9 BPI-M2 Ultra IR interface 1.2.10 BPI-M2 Ultra HDMI interface 1.2.11 BPI-M2 Ultra USB interface 1.2.12 BPI-M2 Ultra OTG interface 1.2.13 BPI-M2 Ultra bluetooth interface 1.2.14 BPI-M2 Ultra UART port 1.2.15 BPI-M2 Ultra MIPI DSI interface 1.2.16 BPI-M2 Ultra CSI camera interface 1.2.17 BPI-M2 Ultra 3.7V lithium battery interface 1.2.18 BPI-M2 Ultra Power interface 1.2.19 BPI-M2 Ultra schematic diagram 1.2.20 BPI-M2 Utra DXF and 3D design 1.2.21 BPI-M2 Ultra software 1.3 Android image 1.3.1 Linux software image 1.3.2 Tina-IoT os 1.3.3 BPI-M2 Ultra source code on github 1.4 Reference documents 1.5 Allwinner R40 chip datasheet 1.5.1 1 BPI-M2 Ultra quality guarantee 1.6 BPI-M2 Ultra BT4.0 Lab test 1.6.1 BPI-M2 Ultra WIFI Lab test 1.6.2 BPI-M2 Ultra validation test report 1.6.3 BPI-M2 Ultra CE,FCC RoHS Certification 1.6.4 All Banana Pi SBC Comparison 1.7 All banana pi product 1.8 BPI 4.0 customized Server 1.9 2 About BPI-M2 Ultra About banana pi BPI-M2 Ultra Banana PI BPI-M2 Ultra is the open source hardware platform, Banana PI BPI-M2 Ultra is a quad-core cortex -A7 CPU ,use Allwinner R40 design, it support WIFI+BT on board.and support SATA interface on board. -

Datasheet Mini5

DataSheet : MINi5- MINI PC The ultra-compact MINi5 PC is based an ultra low voltage dual- core processor. Supporting 4K2K resolution via HDMI interface, the outstanding embedded box computer is ideal for passenger information system, Kiosk, entry-level gaming, video surveillance, and other automation & embedded applications. •Intel Core i5-4200U •Supports four USB 2.0 ports & One USB 3.0 •HDMI Display •Xcalibur W Management Visit our website at: Chip PC HQ Chip PC France Chip PC Inc US Chip PC Germany Chip PC UK Chip PC Netherland & Belgium Tel: +972-8-6909096 Tel: +33 1 83 62 05 12 Tel: +1 866-674-1678 Tel: +49 201 4389 05 - 0 Tel: +44 203 445 5033 Tel: +31 2 024 15 731 www.chippc.com e-mail: [email protected] e-mail: [email protected] e-mail: [email protected] e-mail: [email protected] e-mail: [email protected] e-mail: [email protected] DataSheet : MINi5- MINI PC FRONT SIDE VIEW REAR SIDE VIEW Processor Intel Core i5-4200U 3 Wifi 1 Power LED 4 USB 2.0 ports * 2 2 USB 3.0 ports * 2 Storage 2,5 SATAIII 120GB / 240GB / 500GB or mSATA 32/64/128GB 5 HDMI 6 Audio Out /Mic In Memory Up to 8GB RAM DDR3L 1600 Mhz 7 Ethernet -RJ45 LAN port 8 DC Jack 1x Power button, power LED Front Panel 1 x USB 3.0 Input / Output ports 4 x USB 2.0 Rear Panel 1 x HDMI 1 x microphone(3.5mm) ; 1 x headphone(3.5mm) 1 x RJ 45 1 3 Display Support Resolution HDMI : Up to 1920*1200 Graphics Intel HD GRAPHICS 4 Stereo Audio Output - 3,5 mm (1/8 inch) Audio-Out Jack; 16-bit Stereo, Audio Microphone Input - 3,5 mm (1/8 inch), 5 RJ-45 jack 10/100/1000 Base-T Ethernet Network Wifi built in 802.11 b/g/n Temperature range: Operating - 0ºC to 40ºC (32ºF to 104ºF) 6 Environment Storage - 0ºC to 60ºC (32ºF to 140ºF) Humidity: Operating - 20 to 80% non condensing; Storage – 10 to 90% non condensing Altitude: 0 to 20,000 ft 2 7 Dimensions Dimensions: : 160mm x 143mm x 25mm Device input: 100~240VAC@50/60HZ 8 Power Device Output: 12VDC/3A external power adapter Three-year hardware warranty Warranty Optional extended Warranty for years 4 & 5. -

Getting Started Guide

GETTING STARTED Onion Omega2S Development Kit Getting Started Guide Version 1.0 Omega2 IoT Computer Onion Omega2S Development Kit 1 Revision History Revision Date Description 1.0 March 17, 2018 Initial release Onion Omega2S Development Kit 2 Table of Contents 1. Introduction 4 2. Hardware Overview 5 2.1 Omega2S Hardware Overview 5 2.1.1 Differences from the Omega2 6 2.2 SD Card Development Board Overview 7 2.3 eMMC Development Board Overview 8 3. Hardware Setup 9 4. First Time Setup 13 5. Using the Development Kit 13 5.1 Common Usage 13 5.1.1 Using GPIOs 13 5.1.2 Using USB Storage 13 5.1.3 Using an SD card 14 5.1.4 Rebooting the Omega2S 15 5.1.5 Factory Reset 15 5.2 Removing Omega2S from the Dev Board 16 6. Additional Resources 17 6.1 Hardware Setup Video 17 6.2 Omega2S Datasheet 17 6.3 Schematics 17 6.3.1 Development Board Schematics 17 6.3.2 Omega2S Reference Design Schematics 17 Onion Omega2S Development Kit 3 1. Introduction The Omega2S Development Kit consists of the Omega2S, Onion’s surface-mount Linux WiFi module, and the Development Board, meant to showcase the functionality of the Omega2S module and serve as a test-bed for initial product development. The Omega2S is a highly integrated WiFi enabled, Linux module designed by Onion Corporation. It utilizes the Mediatek MT7688AN System on a Chip (SoC) which is based on the MIPs 24K CPU processor core. The SoC includes 802.11b/g/n Wi-Fi, making the Omega2S ideal for Internet of Things (IoT) applications and projects.