Migration of an Iot Real-Time System and Reimplementation of Some of Its Functions

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Cubietruck – Mini PC

SPRZĘT Cubietruck – mini PC Rynek komputerków jednopłytkowych opartych o procesory ARM zapoczątkowany przez Raspberry Pi rozwija się doskonale. Może nie jak grzyby po deszczu, ale systematycznie pojawiają się nowe rozwiązania: BeagleBoard, Marsboard, Cubieboard, Olinuxino itp. Różnią się one wyposażeniem, wydajnością, dostępnością dokumentacji oraz wsparciem technicznym. Ciekawie rozwija się propozycja Cubieboard. mocujących. Niby nic, ale te trzy kawałki two- org, zapoczątkowana płytką Cubieboard A10 rzywa i paczka tulejek umożliwiają poskładanie Fotografi a 3. Obudowa Cubietruck (opisaną w EP06/2013) i Cubieboard2 zgod- samodzielnego systemu mini-PC wyposażo- ną mechanicznie, ale zbudowaną w oparciu nego w dysk HDD 2,5”, wystarczająco zabez- rolę domowego centrum multimedialnego lub o nowszy, dwurdzeniowy procesor A20, zwięk- pieczając mechanicznie jego elementy. Osłony Linuxowego komputera PC. Jedyne zastrzeżenie szający wydajność Cubie i paletę jej zastosowań w odpowiednich miejscach mają wyfrezowane można mieć do kilku różnokolorowych LED, (fotografi a 1). Najnowsza propozycja to Cubie- otwory umożliwiające korzystanie z GPIO bez bezlitośnie informujących nasze oczy o stanie truck (Cubieboard3), oparty podobnie jak Cu- zdejmowania obudowy. pracy Cubie. bieboard2 (fotografi a 2) o procesor Allwinner Ciekawą propozycją dla osób wykorzy- Cubieboard3 oparty jest o SoC w architektu- A20, lecz mający znacznie bogatsze wyposaże- stujących Cubieboard3 w roli samodzielnego rze ARM7 – Allwinner A20, który w połączeniu nie, co niestety wiąże się z wyższą ceną. Porów- mini-PC, jest pełna obudowa pokazana na fo- ze sporej wielkości dyskiem NAND Flash oraz nanie parametrów poszczególnych komputer- tografi i 3. W swoim wnętrzu mieści swobodnie zwiększoną pamięcią RAM bezproblemowo ków Cubieboard umieszczono w tabeli 1. płytkę Cubieboard3, dysk HDD 2,5” (fotogra- sprawdza się w roli komputera PC pracującego Podobnie jak w przypadku poprzednich fi a 4) i przewody połączeniowe. -

Development Boards This Product Is Rohs Compliant

Development Boards This product is RoHS compliant. PANDABOARD DEVELOPMENT PLATFORM Features: • Core Logic: OMAP4460 applications Processor • Interface: (1) General Purpose Expansion Header • Wireless Connectivity: 802.11 b/g/n (WiLink™ 6.0) • Memory: 1GB DDR2 RAM (I2C, GPMC, USB, MMC, DSS, ETM) • Debug options: JTAG, UART/RS-232, 1 GPIO button NTL • Full Size SD/MMC card port • Camera Expansion Header • Graphics APIs: OpenGL ES v2.0, OpenGL ES v1.1, • 10/100 Ethernet • Display Connectors: HDMI v1.3, DVI-D. LCD Expansion OpenVGv1.1, and EGL v1.3 • USB: (1) USB 2.0 OTG port, (2) USB 2.0 High-speed port • Audio Connectors: 3.5" In/Out, HDMI audio out For quantities greater than listed, call for quote. MOUSER Pandaboard Price Description STOCK NO. Part No. Each 595-PANDABOARD UEVM4430G-01-00-00 Pandaboard ARM Cortex-A9 MPCore 1GHz OMAP4430 SoC Platform 179.00 595-PANDABOARD-ES UEVM4460G-02-01-00 Pandaboard ARM Cortex-A9 MPCore 1GHz OMAP4460 SoC Platform 185.00 Embedded Modules Embedded BEAGLEBOARD SOC PLATFORMS BeagleBoard.org develops low-cost, fan-less single-board computers based on low-power Texas Instruments processors featuring the ARM Cortex-A8 core with all of the expandability of today's desktop machines, but without the bulk, expense, or noise. BeagleBoard.org provides an open source development platform for A B the creation of high-performance embedded designs. Beagleboard C4 Features: Beagleboard xM Features: Beaglebone Features: • Over 1,200 Dhrystone MIPS using the superscalar • Over 2,000 Dhrystone MIPS using the Super-scalar -

User Manual - S.USV Solutions Compatible with Raspberry Pi, up Board and Tinker Board Revision 2.2 | Date 07.06.2018

User Manual - S.USV solutions Compatible with Raspberry Pi, UP Board and Tinker Board Revision 2.2 | Date 07.06.2018 User Manual - S.USV solutions / Revision 2.0 Table of Contents 1 Functions .............................................................................................................................................. 3 2 Technical Specification ........................................................................................................................ 4 2.1 Overview ....................................................................................................................................... 5 2.2 Performance .................................................................................................................................. 6 2.3 Lighting Indicators ......................................................................................................................... 6 3 Installation Guide................................................................................................................................. 7 3.1 Hardware ...................................................................................................................................... 7 3.1.1 Commissioning S.USV ............................................................................................................ 7 3.1.2 Connecting the battery .......................................................................................................... 8 3.1.3 Connecting the external power supply ................................................................................. -

A Highly Modular Router Microarchitecture for Networks-On-Chip

A Highly Modular Router Microarchitecture for Networks-on-Chip Item Type text; Electronic Dissertation Authors Wu, Wo-Tak Publisher The University of Arizona. Rights Copyright © is held by the author. Digital access to this material is made possible by the University Libraries, University of Arizona. Further transmission, reproduction, presentation (such as public display or performance) of protected items is prohibited except with permission of the author. Download date 01/10/2021 08:12:16 Link to Item http://hdl.handle.net/10150/631277 A HIGHLY MODULAR ROUTER MICROARCHITECTURE FOR NETWORKS-ON-CHIP by Wo-Tak Wu Copyright c Wo-Tak Wu 2019 A Dissertation Submitted to the Faculty of the DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING In Partial Fulfillment of the Requirements For the Degree of DOCTOR OF PHILOSOPHY In the Graduate College THE UNIVERSITY OF ARIZONA 2019 THE UNIVERSITY OF ARIZONA GRADUATE COLLEGE As members of the Dissertation Committee, we certify that we have read the dissertation prepared by Wo-Tak Wu, titled A HIGHLY MODULAR ROUTER MICROARCHITECTURE FOR NETWORKS-ON-CHIP and recommend that it be accepted as fulfilling the dissertation requirement for the Degree of Doctor of Philosophy. Dr. Linda Powers --~-__:::::____ ---?---- _________ Date: August 7, 2018 Dr. Roman Lysecky Final approval and acceptance of this dissertation is contingent upon the candidate's submission of the final copies of the dissertation to the Graduate College. I hereby certify that I have read this dissertation prepared under my direction and recommend that it be accepted as fulfilling the dissertation requirement. _____(/2 __·...... ~"--------\;-~=--------- · __ Date: August 7, 2018 Dissertation Director: Dr. -

DM3730, DM3725 Digital Media Processors Datasheet (Rev. D)

DM3730, DM3725 www.ti.com SPRS685D–AUGUST 2010–REVISED JULY 2011 DM3730, DM3725 Digital Media Processors Check for Samples: DM3730, DM3725 1 DM3730, DM3725 Digital Media Processors 1.1 Features 123456 • DM3730/25 Digital Media Processors: • Load-Store Architecture With – Compatible with OMAP™ 3 Architecture Non-Aligned Support – ARM® Microprocessor (MPU) Subsystem • 64 32-Bit General-Purpose Registers • Up to 1-GHz ARM® Cortex™-A8 Core • Instruction Packing Reduces Code Size Also supports 300, 600, and 800-MHz • All Instructions Conditional operation • Additional C64x+TM Enhancements • NEON™ SIMD Coprocessor – Protected Mode Operation – High Performance Image, Video, Audio – Expectations Support for Error (IVA2.2TM) Accelerator Subsystem Detection and Program Redirection • Up to 800-MHz TMS320C64x+TM DSP Core – Hardware Support for Modulo Loop Also supports 260, 520, and 660-MHz Operation operation – C64x+TM L1/L2 Memory Architecture • Enhanced Direct Memory Access (EDMA) • 32K-Byte L1P Program RAM/Cache Controller (128 Independent Channels) (Direct Mapped) • Video Hardware Accelerators • 80K-Byte L1D Data RAM/Cache (2-Way – POWERVR SGX™ Graphics Accelerator Set- Associative) (DM3730 only) • 64K-Byte L2 Unified Mapped RAM/Cache • Tile Based Architecture Delivering up to (4- Way Set-Associative) 20 MPoly/sec • 32K-Byte L2 Shared SRAM and 16K-Byte • Universal Scalable Shader Engine: L2 ROM Multi-threaded Engine Incorporating Pixel – C64x+TM Instruction Set Features and Vertex Shader Functionality • Byte-Addressable (8-/16-/32-/64-Bit Data) -

Openbricks Embedded Linux Framework - User Manual I

OpenBricks Embedded Linux Framework - User Manual i OpenBricks Embedded Linux Framework - User Manual OpenBricks Embedded Linux Framework - User Manual ii Contents 1 OpenBricks Introduction 1 1.1 What is it ?......................................................1 1.2 Who is it for ?.....................................................1 1.3 Which hardware is supported ?............................................1 1.4 What does the software offer ?............................................1 1.5 Who’s using it ?....................................................1 2 List of supported features 2 2.1 Key Features.....................................................2 2.2 Applicative Toolkits..................................................2 2.3 Graphic Extensions..................................................2 2.4 Video Extensions...................................................3 2.5 Audio Extensions...................................................3 2.6 Media Players.....................................................3 2.7 Key Audio/Video Profiles...............................................3 2.8 Networking Features.................................................3 2.9 Supported Filesystems................................................4 2.10 Toolchain Features..................................................4 3 OpenBricks Supported Platforms 5 3.1 Supported Hardware Architectures..........................................5 3.2 Available Platforms..................................................5 3.3 Certified Platforms..................................................7 -

Cubieboard Cubieboard2 Cubietruck Beaglebone Black

Raspberry Pi (Model B rev.2) Cubieboard Cubieboard2 Cubietruck Beaglebone Black 1 Ghz (OC) ARM® Cortex-A6 1 Ghz ARM® Cortex-A8 1 Ghz ARM® Cortex-A7 Dual Core 1 Ghz ARM® Cortex-A7 Dual Core 1 Ghz ARM® Cortex-A8 CPU ARM1176JZF-F Allwinner A10 C8096CA Allwinner A20 Allwinner A20 AM335x GPU/FPU VideoCore IV Mali-400 (CedarX, OpenGL) Mali-400MP2 (CedarX, OpenGL) Mali-400MP2 (CedarX, OpenGL) SGX350 3D / NEON FPU accelerator RAM 512 MB 1 GB DDR3 2 GB 2 GB 512 MB DDR3 Storage micro SD/SDHC 4 GB NAND Flash, micro SD/SDHC, SATA 4 GB NAND Flash, micro SD/SDHC, SATA 4 GB NAND Flash, micro SD/SDHC, SATA 2.0 2GB eMMC Power micro USB (5V/1A) 3.5 W DC 5v/2A DC 5v/2A DC 5v/2.5A DC 5V/500mA Video RCA Composite Video, HDMI 1.4 HDMI HDMI HDMI/VGA microHDMI Audio 3.5 mm Headphone Jack 3.5 mm Headphone Jack / Line In 3.5 mm Headphone Jack 3.5 mm Headphone Jack, SPDIF Network 10/100 Mbps 10/100 Mbps 10/100 Mbps 10/100/1000 Mbps, Wifi, Bluetooth 10/100 Mbps 2x46 PIN GPIO I/O ports 26 PIN GPIO, 2x Ribon 2x48 PIN GPIO, 4PIN Serial, 1IR 2x48 PIN GPIO, 4PIN Serial, 1IR 1x 54 PIN GPIO (Arduino Shield Compatible) USB ports 2x USB 2.0 2x USB 2.0 2x USB 2.0, 1 mini USB OTG 2x USB 2.0, 1 mini USB OTG 1x USB 2.0 Linux (Raspbian, Debian, Fedora, Arch, Gentoo, Kali), Andoid, Angstrom, Ubuntu, Fedora, Gentoo. -

FD-V15N3.Pdf

SILICON COMPOSERS INC FAST Forth Native-Language Embedded Computers DUP >R R> Harris RTX 2000"" l&bit Forth Chip SC32"" 32-bit Forth Microprocessor 08 or 10 MHz operation and 15 MIPS speed. 08 or 10 MHz operation and 15 MIPS speed. 1-cycle 16 x 16 = 32-bi multiply. 1-clock cycle instruction execution. 1-cycle 1&prioritized interrupts. *Contiguous 16 GB data and 2 GB code space. *two 256-word stack memories. *Stack depths limited only by available memory. -&channel 1/0 bus & 3 timer/counters. *Bus request/bus grant lines with on-chip tristate. SC/FOX PCS (Parallel Coprocessor System) SC/FOX SBC32 (Single Board Computer32) *RTX 2000 industrial PGA CPU; 8 & 10 MHz. 032-bi SC32 industrial grade Forth PGA CPU. *System speed options: 8 or 10 MHz. *System speed options: 8 or 10 MHz. -32 KB to 1 MB 0-wait-state static RAM. 42 KB to 512 KB 0-wait-state static RAM. *Full-length PC/XT/AT plug-in (&layer) board. .100mm x 160mm Eurocard size (+layer) board. SC/FOX VME SBC (Single Board Computer) SC/FOX PCS32 (Parallel Coprocessor Sys) *RTX 2000 industrial PGA CPU; 8, 10, 12 MHz. 032-bi SC32 industrial grade Forth PGA CPU. *Bus Master, System Controller, or Bus Slave. *System speed options: 8 or 10 MHz. Up to 640 KB 0-wait-state static RAM. 064 KB to 1 MB 0-wait-state static RAM. -233mm x 160mm 6U size (Slayer) board. *FulClength PC/XT/AT plug-in (Slayer) board. SC/FOX CUB (Single Board Computer) SC/FOX SBC (Single Board Computer) *RTX 2000 PLCC or 2001A PLCC chip. -

WLAN Hacking Workshop

WLAN Hacking Workshop Oz Krakowski – [email protected] Luciano Coelho – [email protected] Agenda What is “OpenLink™”? Workshop intro Board setup Getting WLAN to work on BeagleBoard The OpenLink Challenge Wrap-up – Demo – Ubuntu – Prizes – What’s next What is “OpenLink™”? An open source initiative Wireless connectivity technologies – Wi-Fi™ – Bluetooth® – FM – Roadmap: • Bluetooth Low Energy • ANT • Zigbee® • NFC What is “OpenLink™”? Open link drivers available today Part of mainline Linux kernel Easily attach to open source development platform such as BeagleBoard and PandaBoard What is “OpenLink™”? Website – OpenLink.org – Community – News – Projects – Support – Platforms – Resources … And more to come… Workshop Outline Short hands-on demo Learn how to connect to an AP from the CLI Your chance to get your own BeagleBoard with a WLAN daughter card! Board Setup Pre-requisite: minicom (or another terminal app) Insert the micro-SD card Connect the USB-serial adapter Connect the USB cable (power supply) Serial Console Start minicom – minicom -s -o • /dev/ttyUSB0 • 115200 8N1 • No HW/SW flow control Log in to the serial console • user: root • pwd: rootguri BeagleBoard boot basics Two-phase boot – X-Loader (MLO) – u-boot.bin • Environment setup • Kernel parameters Kernel – Mainline-based (2.6.39-rc1) – One patch for the WLAN daughtercard Connecting to an open Access Point Set your own MAC address ifconfig wlan0 hw ether 08:00:28:00:00:<number> ifconfig wlan0 up Using the iw tool to scan iw wlan0 scan Connecting to an open AP iw wlan0 connect -

New Suppliers Presentation

TechTalk Rutronik´s New Embedded Suppliers: Introduction of Rutronik´s New Partners and Suppliers on the Linecard to meet your Challenges of the Future Bernd Hantsche Cypress Semiconductor is now part of Infineon Infineon is now a Wireless supplier offering following solutions: • Wireless System-on-Chip (Transceiver + Wireless-Stack + your application code, no further MCU required) • WiFi Dual-Band, 1x1 SISO or 2x2 MIMO • Bluetooth Basic Data Rate and Enhanced Data Rate (also known as „classic Bluetooth“) • Bluetooth Low Energy • Bluetooth Dual-Mode (BR/EDR + LE) • WiFi Dual-Band + Bluetooth Dual Mode combination (single chip design) • Wireless Connectivity Chips (Transceiver + Wireless-Stack, external MCU for your application code required) • WiFi Dual-Band, 1x1 SISO or 2x2 MIMO • automotive qualified wireless solutions 3 4 Rutronik offers corresponding Cypress based modules from MURATA • ultra small • safe design cost • safe certification cost • faster time-to-market • less design and logistic complexitity • radio only • connectivity • System-on-Module • Bluetooth Low Energy • Bluetooth Dual-Module • WiFi • WiFi + Bluetooth Dual Mode Do you want to learn more regarding Cypress / Infineon / Murata? [email protected] 5 4D Systems Turning Technology into Art Privately held, est. 1990 HQ, R&D and manufacturing in Australia, regional offices Austria, China, Philippines, Turkey Global leader in intelligent graphic TFT & OLED display module solutions • Smart displays (integrated graphic processor with graphic libraries) • Non-touch devices, -

Banana Pi BPI-M2 A31s Quad Core Single Board Computer

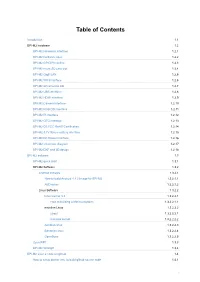

Table of Contents Introduction 1.1 BPI-M2 hardware 1.2 BPI-M2 Hardware interface 1.2.1 BPI-M2 hardware spec 1.2.2 BPI-M2 GPIO Pin define 1.2.3 BPI-M2 micro SD card slot 1.2.4 BPI-M2 GigE LAN 1.2.5 BPI-M2 WIFI interface 1.2.6 BPI-M2 wifi antenna slot 1.2.7 BPI-M2 USB interface 1.2.8 BPI-M2 HDMI interface 1.2.9 BPI-M2 Camera interface 1.2.10 BPI-M2 RGB DSI interface 1.2.11 BPI-M2 IR interface 1.2.12 BPI-M2 OTG interface 1.2.13 BPI-M2 CE FCC RoHS Certification 1.2.14 BPI-M2 3.7V lithium battery interface 1.2.15 BPI-M2 DC Power interface 1.2.16 BPI-M2 schematic diagram 1.2.17 BPI-M2 DXF and 3D design 1.2.18 BPI-M2 software 1.3 BPI-M2 quick start 1.3.1 BPI-M2 Software 1.3.2 Android software 1.3.2.1 How to build Android 4.4.2 Image for BPI-M2 1.3.2.1.1 ABD driver 1.3.2.1.2 Linux Software 1.3.2.2 Linux kernel 3.3 1.3.2.2.1 How to building a Minimal system 1.3.2.2.1.1 mainline Linux 1.3.2.2.2 uboot 1.3.2.2.2.1 mainline kernel 1.3.2.2.2.2 Armbian linux 1.3.2.2.3 Bananian linux 1.3.2.2.4 OpenSuse 1.3.2.2.5 OpenWRT 1.3.3 BPI-M2 WiringPi 1.3.4 BPI-M2 source code on github 1.4 How to setup docker env. -

ISEE Igepv2 BOARD

ISEE IGEPv2 BOARD IGEPv2 BOARD SDK USER MANUAL (Revision 1.02) ISEE (Integration Software & Electronics Engineering ) Crta. De Martorell 95, Local 7 – Terrassa (08224) – Barcelona – SPAIN. +34.93.789.12.71 [email protected] www.iseebcn.com IGEPv2 SDK USER MANUAL v1.02 2 CONTENTS 0 COPYRIGHT NOTICE ................................................................................ 4 1 PREFACE ................................................................................................ 5 1.1 VERY QUICK START GUIDE ................................................................. 5 1.2 ORGANIZATION OF THE MANUAL ........................................................ 6 1.3 MYIGEP ECOSYSTEM .......................................................................... 6 1.4 Useful web LINKS and emails .............................................................. 6 1.5 User registration ............................................................................... 7 2 INTRODUCING IGEPv2 board .................................................................... 8 2.1 IGEPv2 board SDK features ................................................................ 8 2.2 GET your IGEPv2 board POWER ON ..................................................... 9 3 IGEP v2 SDK virtual machine ................................................................... 13 3.1 Why SDK in a virtual machine? .......................................................... 13 3.2 Download SDK virtual machine .......................................................... 13 3.3 Virtual