Microscale Thermal Engineering of Electronic Systems

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Experimental Photonics Multiple Post-Doctoral Positions Experimental Expertise in Any One of the Following Topics/Areas Is Highly Desired

Experimental Photonics Multiple Post-Doctoral Positions Experimental Expertise in any one of the following topics/areas is highly desired . Single photon level measurements , quantum communications . Computational imaging, super-resolution imaging, biomedical imaging . Quantum dots, 2D materials, quantum devices, quantum transport . Single molecule spectroscopy/imaging . Fluorescence microscopy . Optical manipulation of spin , ODMR, Magnetometry, NV centers . Nanofabication (Metasurfaces, plasmonics,silicon photonics) . Streak camera or time-correlated single photon counting experiments . Ultrafast spectroscopy, pump-probe measurements . Single nanoparticle/nanoantenna experiments . Coupling of single quantum emitters to nanophotonic structures . Cold atoms and quantum optics . Infrared spectroscopy, thermal emission measurements Please send your full CV and three representative publications to: [email protected] Prof. Zubin Jacob Birck Nanotechnology Center School of Electrical and Computer Engineering Purdue University, U.S.A. www.electrodynamics.org Zubin Jacob Research Group: Purdue University www.electrodynamics.org About the group Google Scholar Page: https://scholar.google.ca/citations?user=8FXvN_EAAAAJ&hl=en Main Research Areas: Casimir forces, quantum nanophotonics, plasmonics, metamaterials, Vacuum fluctuations, open quantum systems Weblink: www.electrodynamics.org Theory and Experiment Twitter: twitter.com/zjacob_group • Opportunity to closely interact with theorists and experimentalists within the group • Opportunity to travel -

Construction and Research of Thermal Engineering Key Specialty of Application - Oriented Talents Cultivation

International Conference on Education Technology and Management Science (ICETMS 2013) Construction and research of Thermal Engineering key specialty of Application - Oriented Talents Cultivation LI Jiu-ru MENG Ling-kun Harbin University of Science and Technology Harbin University of Science and Technology HUST HUST Harbin China Harbin China e-mail: [email protected] e-mail: [email protected] Abstract—Thermal Engineering specialty of Harbin University of Science and Technology, in the process of construction of B. Subject courses of basic courses. specialty platform— key specialty,, formed a thick essential, wide platform and broaden specialty-caliber, training application-oriented high quality with construction system is conducive to talents[3] optimizing the structure of specialty disciplines, deepen the Subject based curriculum covers Engineering Graphics, Elect reform of promoting the teaching and research and teaching, ric Engineering Theory,Engineering Mechanics,Mecha nical strengthen the construction of specialty content. Improving the Design Basis,Material Molding Tech. To implement broad quality of personnel training, specialty competence, to meet the —range education, the establishment of a thermal energy pl needs of the Economic and Social Development ; by updating atforms curriculum Group, will be a common basis of the spe the concept of education, strengthen the construction of cialty direction included in the Platform. Inclu- ding: Engin teaching staff, strengthening the construction of teaching eering Thermodynamics,Engineering Fluid Me-chanics,Ther conditions, reform of Practice Teaching Link, the reform of mal Transfer Theory,Power Mechanical Engi- neering Basis, teaching contents and teaching methods and means ; strong Thermal Engineering and Power Testing、Energy Saving an impetus to the application - oriented talents cultivation. -

New Trends in Nanophotonics

Nanophotonics 2020; 9(5): 983–985 Editorial New trends in nanophotonics https://doi.org/10.1515/nanoph-2020-0170 Nanophotonics considers the complex interactions between light and matter at the sub-wavelength scale. Recent pro- gress in nanophotonics has revealed unprecedented optical phenomena, which have opened up the novel and rapidly developing fields of metamaterials, photonic crystals, and plasmonics. The last few decades have seen explosive growth in this field, from fundamental research to applications including condensed-matter physics, quantum pho- tonics, near-field/far-field optics, biochemical sensing, deep learning for nanophotonic design, and nanofabrication/ nanomanufacturing. The International Conference on Metamaterials, Photonic Crystals, and Plasmonics (META) is an annual conference of researchers in metamaterials, nanophotonics, and other closely related topics. It covers a broad range of topics including, but not limited to, metasurfaces, meta-devices, topological effects in optics, two-dimensional materials, light-matter interaction in nano-cavities, plasmonic circuits, thermal engineering, and quantum photonic systems. The latest conference, META’19, was held in Lisbon, Portugal (July 23–26, 2019), where the latest trends and recent progress in nanophotonics were discussed to provide further insights for researchers. This special issue introduces a selection of cutting-edge original research and review papers from the conference. Metasurfaces can manipulate the optical properties of light with the ultrathin materials. Two groups review this topic in detail in this issue. Wei et al. [1] focus on the recent research progress in metasurfaces for holographic displays, polarization conversion, active modulation, and linear and nonlinear modulation; the authors discuss in detail the working principle and advantages of metasurfaces and provide many specific applications. -

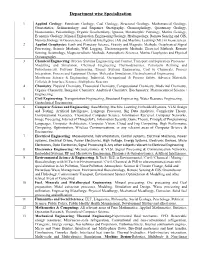

Department Wise Specialization

Department wise Specialization 1 Applied Geology: Petroleum Geology, Coal Geology, Structural Geology, Mathematical Geology, Geostatistics, Sedimentology and Sequence Stratigraphy, Geomorphology, Quaternary Geology, Neotectonics, Paleontology, Organic Geochemistry, Igneous, Metamorphic Petrology, Marine Geology, Economic Geology, Mineral Exploration, Engineering Geology, Hydrogeology, Remote Sensing and GIS, Nanotechnology in Geosciences, Artificial Intelligence (AI) and Machine Learning (ML) in Geosciences. 2 Applied Geophysics: Earth and Planetary Science, Gravity and Magnetic Methods, Geophysical Signal Processing, Seismic Methods, Well Logging, Electromagnetic Methods, Electrical Methods, Remote Sensing, Seismology, Magneto-telluric Methods, Atmospheric Sciences, Marine Geophysics and Physical Oceanography. 3 Chemical Engineering: Process Systems Engineering and Control, Transport and Separation Processes Modelling and Simulation, Chemical Engineering Thermodynamics, Petroleum Refining and Petrochemicals, Polymer Engineering, Energy Systems Engineering, Coal to Chemicals, Process Integration, Process and Equipment Design, Molecular Simulation, Electrochemical Engineering Membrane Science & Engineering, Industrial, Occupational & Process Safety, Advance Materials, Colloids & Interface Science, Multiphase Reactors 4 Chemistry: Physical Chemistry, Theoretical Chemistry, Computational Chemistry, Medicinal Chemistry, Organic Chemistry, Inorganic Chemistry, Analytical Chemistry, Biochemistry, Pharmaceutical Science / Engineering. 5 Civil -

MODERN ELECTRO/THERMOCHEMICAL ADVANCES in LIGHT-METAL SYSTEMS Teaming List

MODERN ELECTRO/THERMOCHEMICAL ADVANCES IN LIGHT-METAL SYSTEMS Teaming List Updated: May 3, 2013 This document contains the list of potential teaming partners for the MODERN ELECTRO/THERMOCHEMICAL ADVANCES IN LIGHT-METAL SYSTEMS, solicited in RFI-0000002 and is published on ARPA-E eXCHANGE (https://arpa-e-foa.energy.gov), ARPA-E’s online application portal. This list will periodically undergo an update as organizations request to be added to this teaming list. If you wish for your organization to be added to this list please refer to https://arpa-e-foa.energy.gov/ for instructions. By enabling and publishing the MODERN ELECTRO/THERMOCHEMICAL ADVANCES IN LIGHT-METAL SYSTEMS Teaming List, ARPA-E is not endorsing or otherwise evaluating the qualifications of the entities that are self-identifying themselves for placement on this Teaming List. Organization Name Organization Area of Background Website Email Phone Address Type Expertise Abengoa Solar is a global leader in concentrating solar power from R&D through plant development, construction, and operation. We have built and operated test facilities and commercial scale plants utilizing our power tower and parabolic trough technologies. Using our technologies and capabilities, we have the abilities to provide technical and construction solutions for process heat and electrical production needs. Specifically related to this announcement, Abengoa Solar has recently been developing a power tower technology using light metals which undergo a solid-liquid phase change as the heat transfer and thermal energy storage material. Through this project, we have developed strengths in handling molten metals at very high temperatures in solar receivers, Business < Renewable transfer systems, storage tanks, and heat exchangers. -

Nanoscale and Microscale Thermophysical Engineering

This article was downloaded by: [108.203.157.83] On: 05 June 2015, At: 18:54 Publisher: Taylor & Francis Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered office: Mortimer House, 37-41 Mortimer Street, London W1T 3JH, UK Nanoscale and Microscale Thermophysical Engineering Publication details, including instructions for authors and subscription information: http://www.tandfonline.com/loi/umte20 Evaluating Broader Impacts of Nanoscale Thermal Transport Research Li Shia, Chris Damesb, Jennifer R. Lukesc, Pramod Reddyd, John Dudae, David G. Cahillf, Jaeho Leeg, Amy Marconneth, Kenneth E. Goodsoni, Je-Hyeong Bahkj, Ali Shakourij, Ravi S. Prasherk, Jonathan Feltsl, William P. Kingm, Bumsoo Hanh & John C. Bischofn a Department of Mechanical Engineering, The University of Texas at Austin, Austin, Texas, USA b Department of Mechanical Engineering, University of California at Click for updates Berkeley, Berkeley, California, USA c Department of Mechanical Engineering and Applied Mechanics, University of Pennsylvania, Philadelphia, Pennsylvania, USA d Materials Science and Engineering, University of Michigan, Ann Arbor, Michigan, USA e Seagate Technology, Minneapolis, Minnesota, USA f Department of Materials Science and Engineering, University of Illinois at Urbana–Champaign, Urbana, Illinois, USA g Department of Mechanical and Aerospace Engineering, University of California at Irvine, Irvine, California, USA h School of Mechanical Engineering, Purdue University, West Lafayette, Indiana, USA i Department of Mechanical Engineering, Stanford University, Stanford, California, USA j Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana, USA k Sheetak Inc., Austin, Texas, USA l Department of Mechanical Engineering, Texas A&M University, College Station, Texas, USA m Department of Mechanical Science and Engineering, University of Illinois at Urbana–Champaign, Urbana, Illinois, USA n Department of Mechanical Engineering, University of Minnesota, Minneapolis, Minnesota, USA Published online: 05 Jun 2015. -

Myths and Truths About Optical Phase Change Materials: a Perspective

Myths and truths about optical phase change materials: A perspective Cite as: Appl. Phys. Lett. 118, 210501 (2021); https://doi.org/10.1063/5.0054114 Submitted: 14 April 2021 . Accepted: 11 May 2021 . Published Online: 26 May 2021 Yifei Zhang, Carlos Ríos, Mikhail Y. Shalaginov, Mo Li, Arka Majumdar, Tian Gu, and Juejun Hu ARTICLES YOU MAY BE INTERESTED IN Perspective on the future of silicon photonics and electronics Applied Physics Letters 118, 220501 (2021); https://doi.org/10.1063/5.0050117 Enhanced light-matter interactions at photonic magic-angle topological transitions Applied Physics Letters 118, 211101 (2021); https://doi.org/10.1063/5.0052580 Ultrawide bandgap semiconductors Applied Physics Letters 118, 200401 (2021); https://doi.org/10.1063/5.0055292 Appl. Phys. Lett. 118, 210501 (2021); https://doi.org/10.1063/5.0054114 118, 210501 © 2021 Author(s). Applied Physics Letters PERSPECTIVE scitation.org/journal/apl Myths and truths about optical phase change materials: A perspective Cite as: Appl. Phys. Lett. 118, 210501 (2021); doi: 10.1063/5.0054114 Submitted: 14 April 2021 . Accepted: 11 May 2021 . Published Online: 26 May 2021 Yifei Zhang,1 Carlos Rıos,1 Mikhail Y. Shalaginov,1 Mo Li,2,3 Arka Majumdar,2,3 Tian Gu,1,4,a) and Juejun Hu1,4,a) AFFILIATIONS 1Department of Materials Science and Engineering, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139, USA 2Department of Electrical and Computer Engineering, University of Washington, Seattle, Washington 98195, USA 3Department of Physics, University of Washington, Seattle, Washington 98195, USA 4Materials Research Laboratory, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139, USA a)Authors to whom correspondence should be addressed: [email protected] and [email protected] ABSTRACT Uniquely furnishing giant and nonvolatile modulation of optical properties and chalcogenide phase change materials (PCMs) have emerged as a promising material to transform integrated photonics and free-space optics alike. -

Mining Engineering Regulations – 2015 Choice Based Credit System

ANNA UNIVERSITY, CHENNAI UNIVERSITY DEPARTMENTS B.E. MINING ENGINEERING REGULATIONS – 2015 CHOICE BASED CREDIT SYSTEM PROGRAM EDUCATIONAL OBJECTIVES Bachelor of Mining Engineering curriculum is designed to prepare the graduates having attitude and knowledge to 1. Function ethically in a variety of professional roles such as mine planner, designer, production manager, consultant, technical support representative, regulatory specialist academicians and research with emphasis on the mineral industries 2. Advance in their careers in the mineral industry, adapting to new situations and emerging problems. 3. Demonstrate an understanding of the importance of mining to the society and for working in a contemporary society in which safety and health, responsibility to the environment, and ethical behavior are required without exception 4. Possess professional skills such as effective communication, teamwork, and leadership. 5. Pursue advanced degrees in mineral-related fields and also those fields that support the mineral industries PROGRAM OUTCOME a) an ability to apply knowledge of mathematics, science, and engineering b) an ability to design and conduct experiments, as well as to analyze and interpret data c) an ability to design a system, component, or process to meet desired needs d) an ability to function on multi-disciplinary teams e) an ability to identify, formulate, and solve engineering problems f) an ability to understand ethical and professional responsibilities g) an ability to control and communicate effectively h) an ability to -

MINING ENGINEERING (Applicable for Batches Admitted from 2016-2017)

COURSE STRUCTURE AND SYLLABUS For MINING ENGINEERING (Applicable for batches admitted from 2016-2017) JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY: KAKINADA KAKINADA - 533 003, Andhra Pradesh, India I Year - I Semester S.No. Subjects L T P Credits 1-HS English – I 4 -- -- 3 2-BS Mathematics – I 4 -- -- 3 3-ES Engineering Chemistry 4 -- -- 3 4-BS Engineering Mechanics 4 -- -- 3 5-BS Computer Programming 4 -- -- 3 6-ES Environmental Studies 4 -- -- 3 7-HS Engineering/Applied Chemistry Laboratory -- -- 3 2 8-BS English Communication Skills Lab – I -- -- 3 2 9-ES C Programming Lab -- -- 3 2 Total Credits 24 I Year - II SEMESTER S.No. Subjects L T P Credits 1-HS English – II 4 -- -- 3 2-BS Mathematics – II (Mathematical Methods) 4 -- -- 3 3-BS Mathematics – III 4 -- -- 3 4-ES Engineering Physics 4 -- -- 3 5-HS Basic Electrical and Electronics Engineering 4 -- -- 3 6-ES Engineering Drawing 4 -- -- 3 7-BS English - Communication Skills Lab – II -- -- 3 2 8-HS Engineering /Applied Physics Lab -- -- 3 2 Engineering /Applied Physics – Virtual Labs – 9-ES -- -- 2 -- Assignments 10 Engg.Workshop & IT Workshop -- -- 3 2 Total Credits 24 II Year - I Semester S.No. Subjects L T P Credits 1 Development of Mineral Deposits 4 -- -- 3 2 Thermal Engineering for Mining 4 -- -- 3 3 Fluid Mechanics and Hydraulic Machines 4 -- -- 3 4 Computer Aided Engineering Drawing Practice 4 -- -- 3 5 Mining Geology – I 4 -- -- 3 6 Managerial Economics & Financial Analysis 4 -- -- 3 7 Electrical and Electronics Engineering Lab -- -- 3 2 8 Fluid Mechanics and Hydraulic Machines Lab -- -- 3 2 Total Credits 22 II Year - II Semester S.No. -

SR. CRYOGENIC THERMAL ENGINEER/PHYSICIST Boston Area, MA

February 2021 SR. CRYOGENIC THERMAL ENGINEER/PHYSICIST Boston Area, MA Giving everyone in the world access to clean, reliable, affordable energy will require substantial expansion of global electricity transmission networks. VEIR is developing a new generation of High Temperature Superconductor (HTS)-based transmission lines, enabling long distance, reliable, low loss, cost–effective power transfer in far smaller right–of–ways. VEIR’s innovations overcome the main barriers to transmission expansion, enabling the world to access the very lowest cost renewable power. The Sr. Cryogenic Thermal Engineer/Physicist will be responsible for building the team to research, design, develop and test VEIR’s cryogenic thermal management subsystems (including all components responsible for heat exchange). DUTIES & RESPONSIBILITIES: • Lead the development and utilization of engineering analysis, models, and simulation tools to improve the performance, reliability, lifetime, and cost of VEIR cryogenic thermal management subsystems and associated components • Lead the iterative design, build, and experimental testing of VEIR cryogenic subsystem and component prototypes • Lead the review, interpretation, and visualization of experimental data on cryogenic subsystems; use data to validate and improve thermal models and strategically plan subsequent prototype design iterations and experimental campaigns • Supervise a small team of engineers and technicians (2-3 direct reports initially); help build team • Collaborate with broader VEIR team to integrate thermal -

Thermal Engineering in Power Systems

Thermal Engineering in Power Systems WITPRESS WIT Press publishes leading books in Science and Technology. Visit our website for the current list of titles. www.witpress.com WITeLibrary Home of the Transactions of the Wessex Institute, the WIT electronic-library provides the international scientific community with immediate and permanent access to individual papers presented at WIT conferences. Visit the WIT eLibrary at http://library.witpress.com International Series on Developments in Heat Transfer Objectives The Developments in Heat Transfer book Series publishes state-of-the-art books and provides valuable contributions to the literature in the field of heat transfer. The overall aim of the Series is to bring to the attention of the international community recent advances in heat transfer by authors in academic research and the engineering industry. Research and development in heat transfer is of significant importance to many branches of technology, not least in energy technology. Developments include new, efficient heat exchangers, novel heat transfer equipment as well as the introduction of systems of heat exchangers in industrial processes. Application areas include heat recovery in the chemical and process industries, and buildings and dwelling houses where heat transfer plays a major role. Heat exchange combined with heat storage is also a methodology for improving the energy efficiency in industry, while cooling in gas turbine systems and combustion engines is another important area of heat transfer research. To progress developments within the field both basic and applied research is needed. Advances in numerical solution methods of partial differential equations, high-speed, efficient and cheap computers, advanced experimental methods using LDV (laser-doppler-velocimetry), PIV (particle-image-velocimetry) and image processing of thermal pictures of liquid crystals, have all led to dramatic advances during recent years in the solution and investigation of complex problems within the field. -

Master of Technology in Mechanical Engineering (With Specialisation in Thermal Engineering) Submitted by Department of Mechanical Engineering

Master of Technology in Mechanical Engineering (With Specialisation in Thermal Engineering) Submitted by Department of Mechanical Engineering MD University, Rohtak Master of Technology in Mechanical Engineering (With Specialisation in Thermal Engineering) EFFECTIVE FROM THE SESSION 2012-13 Semester wise Course Scheme FIRST SEMESTER S. Subject Subject L-T-P Marks Weightage Grand No Code total Theory Sessional . 1 MT-TH 501 Advanced 3-0-0 100 50 150 Thermodynamics 2 MT-TH 503 Advanced Fluid 3-0-0 100 50 150 Dynamics 3 MT-TH 505 Heat Transfer-I 3-0-0 100 50 150 4 MT-TH 507 Combustion 3-0-0 100 50 150 Engineering 5 MT-TH Instrumentation & 3-0-0 100 50 150 803A Measurements 6 MT-TH Advanced Thermal 0-0-4 5 0 50 100 509 Lab 7 MT-TH Instrumentation & 0-0-2 25 25 50 813A Measurements Lab 15-0-6 575 325 900 Master of Technology in Mechanical Engineering (With Specialisation in Thermal Engineering) EFFECTIVE FROM THE SESSION 2012-13 SECOND SEMESTER S. Subject Subject L-T-P Marks Weightage Grand No. Code total Theory Sessional 1 MT-TH Heat Transfer-II 3-0-0 100 50 150 502 2 MT-TH Advanced Gas 3-0-0 100 50 150 508 Dynamics 3 MT-TH Numerical Analysis and 3-0-0 100 50 150 801A Optimization 4 General Elective 3-0-0 100 50 150 5 Programme Elective – I 3-0-0 100 50 150 6 MT-TH Numerical Analysis and 0-0-2 25 25 50 504 Optimization Lab 7 MT-TH Heat and Mass Transfer 0-0-2 25 25 50 506 Lab 15-0-4 550 300 850 General Program Elective Elective – I MT-TH-516- MT-TH-510 – Thermal and Design of Nuclear Power Thermal Systems Plant MT-TH-518 – MT-TH-512 – Steam Generator Heat Exchangers Technology MT-TH-514 – MT-TH 520- Energy Wind Energy Management Technology Master of Technology in Mechanical Engineering (With Specialisation in Thermal Engineering) EFFECTIVE FROM THE SESSION 2012-13 THIRD SEMESTER S.