100G Iscsi - a Bright Future for Ethernet Storage

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

What Is It and How We Use It

Infiniband Overview What is it and how we use it What is Infiniband • Infiniband is a contraction of "Infinite Bandwidth" o can keep bundling links so there is no theoretical limit o Target design goal is to always be faster than the PCI bus. • Infiniband should not be the bottleneck. • Credit based flow control o data is never sent if receiver can not guarantee sufficient buffering What is Infiniband • Infiniband is a switched fabric network o low latency o high throughput o failover • Superset of VIA (Virtual Interface Architecture) o Infiniband o RoCE (RDMA over Converged Ethernet) o iWarp (Internet Wide Area RDMA Protocol) What is Infiniband • Serial traffic is split into incoming and outgoing relative to any port • Currently 5 data rates o Single Data Rate (SDR), 2.5Gbps o Double Data Rate (DDR), 5 Gbps o Quadruple Data Rate (QDR), 10 Gbps o Fourteen Data Rate (FDR), 14.0625 Gbps o Enhanced Data Rate (EDR) 25.78125 Gbps • Links can be bonded together, 1x, 4x, 8x and 12x HDR - High Data Rate NDR - Next Data Rate Infiniband Road Map (Infiniband Trade Association) What is Infiniband • SDR, DDR, and QDR use 8B/10B encoding o 10 bits carry 8 bits of data o data rate is 80% of signal rate • FDR and EDR use 64B/66B encoding o 66 bits carry 64 bits of data Signal Rate Latency SDR 200ns DDR 140ns QDR 100ns Hardware 2 Hardware vendors • Mellanox o bought Voltaire • Intel o bought Qlogic Infiniband business unit Need to standardize hardware. Mellanox and Qlogic cards work in different ways. -

IBM Flex System IB6131 Infiniband Switch User's Guide

IBM Flex System IB6131 InfiniBand Switch User’s Guide ii IBM Flex System IB6131 InfiniBand Switch User’s Guide IBM Flex System IB6131 InfiniBand Switch User’s Guide Note: Before using this information and the product it supports, read the general information in , ʺAppen‐ dix B: Noticesʺ on page 33, the Safety Information and Environmental Notices and Userʹs Guide docu‐ ments on the IBM Notices for Network Devices CD, and the Warranty Information document that comes with the product. First Edition February 2012 © Copyright IBM Corporation 2012. US Government Users Restricted Rights – Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp. Contents Safety . vii Chapter1. Introduction . 1 Related documentation. 1 Notices and statements in this document . 3 Features and specifications. 3 Specifications . 4 Major components of the switch . 5 Chapter2. Installing the switch and basic setup. 7 Installing the IBM Flex system blade . 7 CMM . 7 Serial port access (Method 1) . 7 Configuration . 9 Configuration Wizard (Method 2) . 9 Cabling the switch . 15 Chapter3. LEDs and interfaces. 17 Port LEDs . 17 Switch status lights . 17 Power LED . 18 Fault LED . 18 Unit identification switch identifier LED . 18 RS‐232 interface through mini connector. 18 RJ‐45 Ethernet connector . 19 Configuring the IBM Flex System IB6131 InfiniBand switch . 19 Rerunning the Wizard. 19 Updating the switch software . 20 Chapter4. Connecting to the switch platform . 25 Starting an SSH connection to the switch (CLI) . 25 Starting a WebUI connection to the switch . 25 Managing the IBM Flex System IB6131 InfiniBand switch . 26 Chapter5. Solving problems . 27 Running POST . -

Global MV Standards English

www.visiononline.org www.emva.org www.jiia.org www.china-vision.org www.vdma.com/vision Member-supported trade associations promote the growth of the global vision and imaging industry. Standards development is key to the success of the industry and its trade groups help fund, maintain, manage and promote standards. In 2009, three leading vision associations, AIA, EMVA and JIIA began a cooperative initiative to coordinate the development of globally adopted vision standards. In 2015 they were joined by CMVU and VDMA-MV. This publication is one product of this cooperative effort. Version: April 2016 Copyright 2013, AIA, EMVA and JIIA. All rights reserved. Data within is intended as an information resource and no warranty for its use is given. Camera Link (including PoCL and PoCL-Lite), Camera Link HS, GigE Vision and USB3 Vision are the trademarks of AIA. GenICam is the trademark of EMVA. CoaXPress and IIDC2 are the trademarks of JIIA. FireWire is the trademark of Apple Inc. IEEE 1394 is the trademark of The 1394 Trade Association. USB is the trademark of USB Implementers Forum, Inc. All other names are trademarks or trade names of their respective companies. This is a comprehensive look at the various digital hardware and software interface standards used in machine vision and imaging. In the early days of machine vision, the industry adopted existing analog television standards such as CCIR or RS-170 for the interface between cameras and frame grabbers. The defining In the 1990s, digital technology became characteristics of today’s prevalent and a multitude of proprietary hardware and software interface solutions were used. -

Infiniband Trade Association Integrators' List

InfiniBand Trade Association Integrators’ List April 2019 © InfiniBand Trade Association SPACE IBTA InfiniBand Integrators' List April 2019 Manufacturer Description Model Type Speed FW SW ConnectX®-3 Pro VPI, FDR IB (56Gb/s) and 40/56GbE MLNX_OFED_LINUX 4.4- Mellanox MCX354A-FCCT HCA FDR 2.42.5000 Dual-port QSFP, PCIe3.0 x8 2.0.7.0 ConnectX®-4 VPI, EDR IB (100Gb/s) and 100GbE MLNX_OFED_LINUX 4.5- Mellanox MCX456A-ECAT HCA EDR 12.24.1000 Dual-port QSFP28, PCIe3.0 x16 1.0.1.0 ConnectX®-5 VPI, EDR IB (100Gb/s) and 100GbE MLNX_OFED_LINUX 4.5- Mellanox MCX556A-EDAT HCA EDR 16.24.1000 Dual-port QSFP28, PCIe4.0 x16 1.0.1.0 ConnectX®-6 VPI adapter card, HDR IB (200Gb/s) and 200GbE, MLNX_OFED_LINUX 4.5- Mellanox MCX653A-HCAT HCA HDR 20.25.0330 dual-port QSFP56, Socket Direct 2x PCIe3.0 x16 1.0.1.0 SwitchX®2 InfiniBand to Ethernet gateway, 36 QSFP ports, Mellanox MSX6036G-2SFS Switch FDR 9.4.5070 3.6.8010 Managed Switch Switch-IB 2 based EDR InfiniBand 1U Switch, 36 QSFP28 ports, Mellanox MSB7800-ES2F Switch EDR 15.1910.0618 3.7.1134 x86 dual core Mellanox® Quantum(TM) HDR InfiniBand Switch, 40 QSFP56 Mellanox MQM8700-HS2F Switch HDR 27.2000.1016 3.7.1942 ports, 2 Power Supplies (AC), x86 dual core Software Versions Diagnostic Software Operating System Cent OS 7.5.1804 ibutils2 MLNX OFED 4.5-1.0.1.0 Mellanox OFED MLNX OFED 4.5-1.0.1.0 Compliance Test Suite v. 1.0.52 Open MPII Open MPI 3.1.2 Benchmark Intel MPI Benchmarks Benchmarks Performed Test Plan Software Forge IBTA MOI Suite PingPong Gather Duration 2-5 Minutes PingPing Gatherv Sendrecv Scatter Conditions for Passing Testing Exchange Scatterv Link Width Link width is @ expected width - i.e. -

Infiniband Technology Overview

InfiniBand Technology Overview Dror Goldenberg, Mellanox Technologies SNIA Legal Notice The material contained in this tutorial is copyrighted by the SNIA. Member companies and individuals may use this material in presentations and literature under the following conditions: Any slide or slides used must be reproduced without modification The SNIA must be acknowledged as source of any material used in the body of any document containing material from these presentations. This presentation is a project of the SNIA Education Committee. InfiniBand Technology Overview 2 © 2008 Storage Networking Industry Association. All Rights Reserved. Abstract InfiniBand Technology Overview The InfiniBand architecture brings fabric consolidation to the data center. Storage networking can concurrently run with clustering, communication and management fabrics over the same infrastructure, preserving the behavior of multiple fabrics. The tutorial provides an overview of the InfiniBand architecture including discussion of High Speed – Low Latency, Channel I/O, QoS scheduling, partitioning, high availability and protocol offload. InfiniBand based storage protocols, iSER (iSCSI RDMA Protocol), NFS over RDMA and SCSI RDMA Protocol (SRP), are introduced and compared with alternative storage protocols, such as iSCSI and FCP. The tutorial further enumerates value-add features that the InfiniBand brings to clustered storage, such as atomic operations and end to end data integrity. Learning Objectives: Understand the InfiniBand architecture and feature set. Understand the benefits of InfiniBand for networked storage. Understand the standard InfiniBand storage protocols. InfiniBand Technology Overview 3 © 2008 Storage Networking Industry Association. All Rights Reserved. Agenda Motivation and General Overview Protocol Stack Layers Storage Protocols over InfiniBand Benefits InfiniBand Technology Overview 4 © 2008 Storage Networking Industry Association. -

Opencapi, Gen-Z, CCIX: Technology Overview, Trends, and Alignments

OpenCAPI, Gen-Z, CCIX: Technology Overview, Trends, and Alignments BRAD BENTON| AUGUST 8, 2017 Agenda 2 | OpenSHMEM Workshop | August 8, 2017 AGENDA Overview and motivation for new system interconnects Technical overview of the new, proposed technologies Emerging trends Paths to convergence? 3 | OpenSHMEM Workshop | August 8, 2017 Overview and Motivation 4 | OpenSHMEM Workshop | August 8, 2017 NEWLY EMERGING BUS/INTERCONNECT STANDARDS Three new bus/interconnect standards announced in 2016 CCIX: Cache Coherent Interconnect for Accelerators ‒ Formed May, 2016 ‒ Founding members include: AMD, ARM, Huawei, IBM, Mellanox, Xilinx ‒ ccixconsortium.com Gen-Z ‒ Formed August, 2016 ‒ Founding members include: AMD, ARM, Cray, Dell EMC, HPE, IBM, Mellanox, Micron, Xilinx ‒ genzconsortium.org OpenCAPI: Open Coherent Accelerator Processor Interface ‒ Formed September, 2016 ‒ Founding members include: AMD, Google, IBM, Mellanox, Micron ‒ opencapi.org 5 5 | OpenSHMEM Workshop | August 8, 2017 NEWLY EMERGING BUS/INTERCONNECT STANDARDS Motivations for these new standards Tighter coupling between processors and accelerators (GPUs, FPGAs, etc.) ‒ unified, virtual memory address space ‒ reduce data movement and avoid data copies to/from accelerators ‒ enables sharing of pointer-based data structures w/o the need for deep copies Open, non-proprietary standards-based solutions Higher bandwidth solutions ‒ 25Gbs and above vs. 16Gbs forPCIe-Gen4 Better exploitation of new and emerging memory/storage technologies ‒ NVMe ‒ Storage class memory (SCM), -

Break Through the TCP/IP Bottleneck with Iwarp

Printer Friendly Version Page 1 of 6 Enter Search Term Enter Drill Deeper or ED Online ID Technologies Design Hotspots Resources Shows Magazine eBooks & Whitepapers Jobs More... Click to view this week's ad screen [Design View / Design Solution] Break Through The TCP/IP Bottleneck With iWARP Using a high-bandwidth, low-latency network solution in the same network infrastructure provides good insurance for generation networks. Sweta Bhatt, Prashant Patel ED Online ID #21970 October 22, 2009 Copyright © 2006 Penton Media, Inc., All rights reserved. Printing of this document is for personal use only. Reprints T he online economy, particularly e-business, entertainment, and collaboration, continues to dramatically and rapidly increase the amount of Internet traffic to and from enterprise servers. Most of this data is going through the transmission control protocol/Internet protocol (TCP/IP) stack and Ethernet controllers. As a result, Ethernet controllers are experiencing heavy network traffic, which requires more system resources to process network packets. The CPU load increases linearly as a function of network packets processed, diminishing the CPU’s availability for other applications. Because the TCP/IP consumes a significant amount of the host CPU processing cycles, a heavy TCP/IP load may leave few system resources available for other applications. Techniques for reducing the demand on the CPU and lowering the system bottleneck, though, are available. iWARP SOLUTIONS Although researchers have proposed many mechanisms and theories for parallel systems, only a few have resulted in working computing platforms. One of the latest to enter the scene is the Internet Wide Area RDMA Protocol, or iWARP, a joint project by Carnegie Mellon University Corp. -

Designcon 2003 Tecforum I2C Bus Overview January 27 2003

DesignCon 2003 TecForum I2C Bus Overview January 27 2003 Philips Semiconductors Jean Marc Irazabal –Technical Marketing Manager for I2C Devices Steve Blozis –International Product Manager for I2C Devices Agenda • 1st Hour • Serial Bus Overview • I2C Theory Of Operation • 2nd Hour • Overcoming Previous Limitations • I2C Development Tools and Evaluation Board • 3rd Hour • SMBus and IPMI Overview • I2C Device Overview • I2C Patent and Legal Information • Q & A Slide speaker notes are included in AN10216 I2C Manual 2 DesignCon 2003 TecForum I C Bus Overview 2 1st Hour 2 DesignCon 2003 TecForum I C Bus Overview 3 Serial Bus Overview 2 DesignCon 2003 TecForum I C Bus Overview 4 Com m uni c a t i o ns Automotive SERIAL Consumer BUSES IEEE1394 DesignCon 2003 TecForum I UART SPI 2 C Bus Overview In d u s t r ia l 5 General concept for Serial communications SCL SDA select 3 select 2 select 1 READ Register or enable Shift Reg# enable Shift Reg# enable Shift Reg# WRITE? // to Ser. // to Ser. // to Ser. Shift R/W Parallel to Serial R/W R/W “MASTER” DATA SLAVE 1 SLAVE 2 SLAVE 3 • A point to point communication does not require a Select control signal • An asynchronous communication does not have a Clock signal • Data, Select and R/W signals can share the same line, depending on the protocol • Notice that Slave 1 cannot communicate with Slave 2 or 3 (except via the ‘master’) Only the ‘master’ can start communicating. Slaves can ‘only speak when spoken to’ 2 DesignCon 2003 TecForum I C Bus Overview 6 Typical Signaling Characteristics LVTTL 2 RS422/485 -

DGX-1 User Guide

NVIDIA DGX-1 DU-08033-001 _v15 | May 2018 User Guide TABLE OF CONTENTS Chapter 1. Introduction to the NVIDIA DGX-1 Deep Learning System................................. 1 1.1. Using the DGX-1: Overview............................................................................. 1 1.2. Hardware Specifications................................................................................. 2 1.2.1. Components.......................................................................................... 2 1.2.2. Mechanical............................................................................................3 1.2.3. Power Requirements................................................................................ 3 1.2.4. Connections and Controls.......................................................................... 3 1.2.5. Rear Panel Power Controls.........................................................................4 1.2.6. LAN LEDs..............................................................................................5 1.2.7. IPMI Port LEDs....................................................................................... 5 1.2.8. Hard Disk Indicators................................................................................ 6 1.2.9. Power Supply Unit (PSU) LED..................................................................... 7 Chapter 2. Installation and Setup............................................................................ 8 2.1. Registering Your DGX-1................................................................................. -

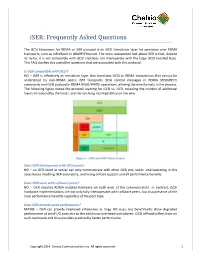

Iser: Frequently Asked Questions

iSER: Frequently Asked Questions The iSCSI Extensions for RDMA or iSER protocol is an iSCSI translation layer for operation over RDMA transports, such as InfiniBand or iWARP/Ethernet. The most unexpected fact about iSER is that, despite its name, it is not compatible with iSCSI and does not interoperate with the large iSCSI installed base. This FAQ clarifies this and other questions that are associated with this protocol. Is iSER compatible with iSCSI? NO – iSER is effectively an emulation layer that translates iSCSI to RDMA transactions that cannot be understood by non-RDMA peers: iSER transports iSCSI control messages in RDMA SEND/RECV commands and iSCSI payload in RDMA READ/WRITE operations, altering the wire formats in the process. The following figure shows the protocol layering for iSCSI vs. iSER, revealing the number of additional layers introduced by the latter, and the resulting incompatibility on the wire. Figure 1 – iSCSI and iSER Protocol Layers Does iSER interoperate with iSCSI peers? NO – an iSER client or server can only communicate with other iSER end nodes. Interoperating in this case means disabling iSER extensions, and losing offload support and all performance benefits. Does iSER work with software peers? NO – iSER requires RDMA enabled hardware on both ends of the communication. In contrast, iSCSI hardware implementations are not only fully interoperable with software peers, but also preserve all the local performance benefits regardless of the peer type. Does iSER provide good performance? MAYBE – iSER can provide improved efficiencies at large I/O sizes, but benchmarks show degraded performance at small I/O sizes due to the additional overheads introduced. -

Iscsi Will Still Be Widely Deployed for at Least the Next Few Years, but Its Growth Prospects Beyond That Are Very Unclear

Widespread use and support mean iSCSI will still be widely deployed for at least the next few years, but its growth prospects beyond that are very unclear. By John F. Kim, Chair, SNIA Networking Storage Forum. What is iSCSI? iSCSI is a block storage protocol for storage networking. It stands for “Internet Small Computer Systems Interface” and runs the very common SCSI storage protocol across a network connection which is usually Ethernet with TCP. You can read more about iSCSI at the “What Is” section of the SNIA website. (The SCSI storage protocol is also used to access block storage as part of the SAS, SRP, and FCP protocols, which run over various physical connections.) Originally, the SCSI protocol was used only for local storage, meaning individual disk drives or direct-attached storage (DAS). Then around 1993, Fibre Channel came along and enabled SCSI to run the Fibre Channel Protocol (FCP) on top of a Fibre Channel Storage Area Network (FC-SAN). iSCSI was submitted as a standard in 2000 and grew in popularity as it was supported by more operating systems, first requiring dedicated iSCSI HBAs but later using a software iSCSI initiator that ran on top of any type of Ethernet NIC. The dedicated iSCSI HBAs gave iSCSI faster performance that was closer to Fibre Channel performance at the time, while the software iSCSI initiator made it easy to use iSCSI from many servers without buying special HBAs for each server. Probably the biggest boost to iSCSI adoption was when Microsoft Windows Server 2008 included a software iSCSI initiator 1/6 (starting in 2008, of course). -

Designing High-Performance and Scalable Clustered Network Attached Storage with Infiniband

DESIGNING HIGH-PERFORMANCE AND SCALABLE CLUSTERED NETWORK ATTACHED STORAGE WITH INFINIBAND DISSERTATION Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University By Ranjit Noronha, MS * * * * * The Ohio State University 2008 Dissertation Committee: Approved by Dhabaleswar K. Panda, Adviser Ponnuswammy Sadayappan Adviser Feng Qin Graduate Program in Computer Science and Engineering c Copyright by Ranjit Noronha 2008 ABSTRACT The Internet age has exponentially increased the volume of digital media that is being shared and distributed. Broadband Internet has made technologies such as high quality streaming video on demand possible. Large scale supercomputers also consume and cre- ate huge quantities of data. This media and data must be stored, cataloged and retrieved with high-performance. Researching high-performance storage subsystems to meet the I/O demands of applications in modern scenarios is crucial. Advances in microprocessor technology have given rise to relatively cheap off-the-shelf hardware that may be put together as personal computers as well as servers. The servers may be connected together by networking technology to create farms or clusters of work- stations (COW). The evolution of COWs has significantly reduced the cost of ownership of high-performance clusters and has allowed users to build fairly large scale machines based on commodity server hardware. As COWs have evolved, networking technologies like InfiniBand and 10 Gigabit Eth- ernet have also evolved. These networking technologies not only give lower end-to-end latencies, but also allow for better messaging throughput between the nodes. This allows us to connect the clusters with high-performance interconnects at a relatively lower cost.