SELECTION of CYCLIC REDUNDANCY CODE and CHECKSUM March 2015 ALGORITHMS to ENSURE CRITICAL DATA INTEGRITY 6

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Hash Functions

Hash Functions A hash function is a function that maps data of arbitrary size to an integer of some fixed size. Example: Java's class Object declares function ob.hashCode() for ob an object. It's a hash function written in OO style, as are the next two examples. Java version 7 says that its value is its address in memory turned into an int. Example: For in an object of type Integer, in.hashCode() yields the int value that is wrapped in in. Example: Suppose we define a class Point with two fields x and y. For an object pt of type Point, we could define pt.hashCode() to yield the value of pt.x + pt.y. Hash functions are definitive indicators of inequality but only probabilistic indicators of equality —their values typically have smaller sizes than their inputs, so two different inputs may hash to the same number. If two different inputs should be considered “equal” (e.g. two different objects with the same field values), a hash function must re- spect that. Therefore, in Java, always override method hashCode()when overriding equals() (and vice-versa). Why do we need hash functions? Well, they are critical in (at least) three areas: (1) hashing, (2) computing checksums of files, and (3) areas requiring a high degree of information security, such as saving passwords. Below, we investigate the use of hash functions in these areas and discuss important properties hash functions should have. Hash functions in hash tables In the tutorial on hashing using chaining1, we introduced a hash table b to implement a set of some kind. -

IEEE Std 802.3™-2012 New York, NY 10016-5997 (Revision of USA IEEE Std 802.3-2008)

IEEE Standard for Ethernet IEEE Computer Society Sponsored by the LAN/MAN Standards Committee IEEE 3 Park Avenue IEEE Std 802.3™-2012 New York, NY 10016-5997 (Revision of USA IEEE Std 802.3-2008) 28 December 2012 IEEE Std 802.3™-2012 (Revision of IEEE Std 802.3-2008) IEEE Standard for Ethernet Sponsor LAN/MAN Standards Committee of the IEEE Computer Society Approved 30 August 2012 IEEE-SA Standard Board Abstract: Ethernet local area network operation is specified for selected speeds of operation from 1 Mb/s to 100 Gb/s using a common media access control (MAC) specification and management information base (MIB). The Carrier Sense Multiple Access with Collision Detection (CSMA/CD) MAC protocol specifies shared medium (half duplex) operation, as well as full duplex operation. Speed specific Media Independent Interfaces (MIIs) allow use of selected Physical Layer devices (PHY) for operation over coaxial, twisted-pair or fiber optic cables. System considerations for multisegment shared access networks describe the use of Repeaters that are defined for operational speeds up to 1000 Mb/s. Local Area Network (LAN) operation is supported at all speeds. Other specified capabilities include various PHY types for access networks, PHYs suitable for metropolitan area network applications, and the provision of power over selected twisted-pair PHY types. Keywords: 10BASE; 100BASE; 1000BASE; 10GBASE; 40GBASE; 100GBASE; 10 Gigabit Ethernet; 40 Gigabit Ethernet; 100 Gigabit Ethernet; attachment unit interface; AUI; Auto Negotiation; Backplane Ethernet; data processing; DTE Power via the MDI; EPON; Ethernet; Ethernet in the First Mile; Ethernet passive optical network; Fast Ethernet; Gigabit Ethernet; GMII; information exchange; IEEE 802.3; local area network; management; medium dependent interface; media independent interface; MDI; MIB; MII; PHY; physical coding sublayer; Physical Layer; physical medium attachment; PMA; Power over Ethernet; repeater; type field; VLAN TAG; XGMII The Institute of Electrical and Electronics Engineers, Inc. -

Linear-XOR and Additive Checksums Don't Protect Damgård-Merkle

Linear-XOR and Additive Checksums Don’t Protect Damg˚ard-Merkle Hashes from Generic Attacks Praveen Gauravaram1! and John Kelsey2 1 Technical University of Denmark (DTU), Denmark Queensland University of Technology (QUT), Australia. [email protected] 2 National Institute of Standards and Technology (NIST), USA [email protected] Abstract. We consider the security of Damg˚ard-Merkle variants which compute linear-XOR or additive checksums over message blocks, inter- mediate hash values, or both, and process these checksums in computing the final hash value. We show that these Damg˚ard-Merkle variants gain almost no security against generic attacks such as the long-message sec- ond preimage attacks of [10,21] and the herding attack of [9]. 1 Introduction The Damg˚ard-Merkle construction [3, 14] (DM construction in the rest of this article) provides a blueprint for building a cryptographic hash function, given a fixed-length input compression function; this blueprint is followed for nearly all widely-used hash functions. However, the past few years have seen two kinds of surprising results on hash functions, that have led to a flurry of research: 1. Generic attacks apply to the DM construction directly, and make few or no assumptions about the compression function. These attacks involve attacking a t-bit hash function with more than 2t/2 work, in order to violate some property other than collision resistance. Exam- ples of generic attacks are Joux multicollision [8], long-message second preimage attacks [10,21] and herding attack [9]. 2. Cryptanalytic attacks apply to the compression function of the hash function. -

Hash (Checksum)

Hash Functions CSC 482/582: Computer Security Topics 1. Hash Functions 2. Applications of Hash Functions 3. Secure Hash Functions 4. Collision Attacks 5. Pre-Image Attacks 6. Current Hash Security 7. SHA-3 Competition 8. HMAC: Keyed Hash Functions CSC 482/582: Computer Security Hash (Checksum) Functions Hash Function h: M MD Input M: variable length message M Output MD: fixed length “Message Digest” of input Many inputs produce same output. Limited number of outputs; infinite number of inputs Avalanche effect: small input change -> big output change Example Hash Function Sum 32-bit words of message mod 232 M MD=h(M) h CSC 482/582: Computer Security 1 Hash Function: ASCII Parity ASCII parity bit is a 1-bit hash function ASCII has 7 bits; 8th bit is for “parity” Even parity: even number of 1 bits Odd parity: odd number of 1 bits Bob receives “10111101” as bits. Sender is using even parity; 6 1 bits, so character was received correctly Note: could have been garbled, but 2 bits would need to have been changed to preserve parity Sender is using odd parity; even number of 1 bits, so character was not received correctly CSC 482/582: Computer Security Applications of Hash Functions Verifying file integrity How do you know that a file you downloaded was not corrupted during download? Storing passwords To avoid compromise of all passwords by an attacker who has gained admin access, store hash of passwords Digital signatures Cryptographic verification that data was downloaded from the intended source and not modified. Used for operating system patches and packages. -

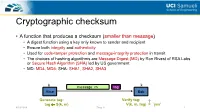

Cryptographic Checksum

Cryptographic checksum • A function that produces a checksum (smaller than message) • A digest function using a key only known to sender and recipient • Ensure both integrity and authenticity • Used for code-tamper protection and message-integrity protection in transit • The choices of hashing algorithms are Message Digest (MD) by Ron Rivest of RSA Labs or Secure Hash Algorithm (SHA) led by US government • MD: MD4, MD5; SHA: SHA1, SHA2, SHA3 k k message m tag Alice Bob Generate tag: Verify tag: ? tag S(k, m) V(k, m, tag) = `yes’ 4/19/2019 Zhou Li 1 Constructing cryptographic checksum • HMAC (Hash Message Authentication Code) • Problem to solve: how to merge key with hash H: hash function; k: key; m: message; example of H: SHA-2-256 ; output is 256 bits • Building a MAC out of a hash function: Paddings to make fixed-size block https://en.wikipedia.org/wiki/HMAC 4/19/2019 Zhou Li 2 Cryptoanalysis on crypto checksums • MD5 broken by Xiaoyun Input Output Wang et al. at 2004 • Collisions of full MD5 less than 1 hour on IBM p690 cluster • SHA-1 theoretically broken by Xiaoyun Wang et al. at 2005 • 269 steps (<< 280 rounds) to find a collision • SHA-1 practically broken by Google at 2017 • First collision found with 6500 CPU years and 100 GPU years Current Secure Hash Standard Properties https://shattered.io/static/shattered.pdf 4/19/2019 Zhou Li 3 Elliptic Curve Cryptography • RSA algorithm is patented • Alternative asymmetric cryptography: Elliptic Curve Cryptography (ECC) • The general algorithm is in the public domain • ECC can provide similar -

A PROPOSED REVISION to IRIG 218 BASED on REAL WORLD EXPERIENCE Gary A

A PROPOSED REVISION TO IRIG 218 BASED ON REAL WORLD EXPERIENCE Gary A. Thom GDP Space Systems 300 Welsh Road, Horsham, PA 19044 [email protected] Abstract The Range Commanders Council has been attempting to standardize Telemetry over IP (TMoIP) for many years now. While the attempt has been valiant, the outcome to date has not been very successful. As a result, many vendors have implemented their own proprietary methods for sending PCM data over IP networks resulting in a lack of interoperability. As telemetry ground stations are finally making the move toward network centric architectures, it is worth considering the lessons learned over the previous 10 years of designing, installing, troubleshooting and optimizing telemetry data distribution over IP networks. This paper describes a proposed revision to IRIG 218 based on these real life experiences. It discusses the critical decisions and architectural decisions to be made and some of the pitfalls to be avoid. Key Words: IRIG 218, TMoIP, IP, TCP, UDP, network, PCM. 1 Introduction The motivation for moving to TMoIP was twofold: first, to find cost effective PCM data distribution and second, to provide reliable and robust PCM data distribution regardless of the destination. The global explosion of IP networking has provided a built in infrastructure with access to the most remote destinations. A wide variety of transport mechanisms for IP traffic provides ubiquitous connectivity, whether twisted pair, fiber optic cable, microwave links, satellite links, analog modems and cell phones, IP connectivity is everywhere. This ubiquity and global deployment has driven down the cost of networking components such as routers and switches. -

FIPS 198, the Keyed-Hash Message Authentication Code (HMAC)

ARCHIVED PUBLICATION The attached publication, FIPS Publication 198 (dated March 6, 2002), was superseded on July 29, 2008 and is provided here only for historical purposes. For the most current revision of this publication, see: http://csrc.nist.gov/publications/PubsFIPS.html#198-1. FIPS PUB 198 FEDERAL INFORMATION PROCESSING STANDARDS PUBLICATION The Keyed-Hash Message Authentication Code (HMAC) CATEGORY: COMPUTER SECURITY SUBCATEGORY: CRYPTOGRAPHY Information Technology Laboratory National Institute of Standards and Technology Gaithersburg, MD 20899-8900 Issued March 6, 2002 U.S. Department of Commerce Donald L. Evans, Secretary Technology Administration Philip J. Bond, Under Secretary National Institute of Standards and Technology Arden L. Bement, Jr., Director Foreword The Federal Information Processing Standards Publication Series of the National Institute of Standards and Technology (NIST) is the official series of publications relating to standards and guidelines adopted and promulgated under the provisions of Section 5131 of the Information Technology Management Reform Act of 1996 (Public Law 104-106) and the Computer Security Act of 1987 (Public Law 100-235). These mandates have given the Secretary of Commerce and NIST important responsibilities for improving the utilization and management of computer and related telecommunications systems in the Federal government. The NIST, through its Information Technology Laboratory, provides leadership, technical guidance, and coordination of government efforts in the development of standards and guidelines in these areas. Comments concerning Federal Information Processing Standards Publications are welcomed and should be addressed to the Director, Information Technology Laboratory, National Institute of Standards and Technology, 100 Bureau Drive, Stop 8900, Gaithersburg, MD 20899-8900. William Mehuron, Director Information Technology Laboratory Abstract This standard describes a keyed-hash message authentication code (HMAC), a mechanism for message authentication using cryptographic hash functions. -

Table of Contents Local Transfers

Table of Contents Local Transfers......................................................................................................1 Checking File Integrity.......................................................................................................1 Local File Transfer Commands...........................................................................................3 Shift Transfer Tool Overview..............................................................................................5 Local Transfers Checking File Integrity It is a good practice to confirm whether your files are complete and accurate before you transfer the files to or from NAS, and again after the transfer is complete. The easiest way to verify the integrity of file transfers is to use the NAS-developed Shift tool for the transfer, with the --verify option enabled. As part of the transfer, Shift will automatically checksum the data at both the source and destination to detect corruption. If corruption is detected, partial file transfers/checksums will be performed until the corruption is rectified. For example: pfe21% shiftc --verify $HOME/filename /nobackuppX/username lou% shiftc --verify /nobackuppX/username/filename $HOME your_localhost% sup shiftc --verify filename pfe: In addition to Shift, there are several algorithms and programs you can use to compute a checksum. If the results of the pre-transfer checksum match the results obtained after the transfer, you can be reasonably certain that the data in the transferred files is not corrupted. If -

The Effectiveness of Checksums for Embedded Control Networks

IEEE TRANSACTIONS ON DEPENDABLE AND SECURE COMPUTING, VOL. 6, NO. 1, JANUARY-MARCH 2009 59 The Effectiveness of Checksums for Embedded Control Networks Theresa C. Maxino, Member, IEEE, and Philip J. Koopman, Senior Member, IEEE Abstract—Embedded control networks commonly use checksums to detect data transmission errors. However, design decisions about which checksum to use are difficult because of a lack of information about the relative effectiveness of available options. We study the error detection effectiveness of the following commonly used checksum computations: exclusive or (XOR), two’s complement addition, one’s complement addition, Fletcher checksum, Adler checksum, and cyclic redundancy codes (CRCs). A study of error detection capabilities for random independent bit errors and burst errors reveals that the XOR, two’s complement addition, and Adler checksums are suboptimal for typical network use. Instead, one’s complement addition should be used for networks willing to sacrifice error detection effectiveness to reduce computational cost, the Fletcher checksum should be used for networks looking for a balance between error detection and computational cost, and CRCs should be used for networks willing to pay a higher computational cost for significantly improved error detection. Index Terms—Real-time communication, networking, embedded systems, checksums, error detection codes. Ç 1INTRODUCTION common way to improve network message data However, the use of less capable checksum calculations Aintegrity is appending a checksum. Although it is well abounds.Onewidelyusedalternativeistheexclusiveor(XOR) known that cyclic redundancy codes (CRCs) are effective at checksum, usedby HART[4],Magellan [5],and manyspecial- error detection, many embedded networks employ less purpose embedded networks (for example, [6], [7], and [8]). -

![3. Layer 2 - the Data Link Layer This Section of the Course, So That We Will Quickly Gain an Read [Tanenbaum96] Ch](https://docslib.b-cdn.net/cover/7444/3-layer-2-the-data-link-layer-this-section-of-the-course-so-that-we-will-quickly-gain-an-read-tanenbaum96-ch-1717444.webp)

3. Layer 2 - the Data Link Layer This Section of the Course, So That We Will Quickly Gain an Read [Tanenbaum96] Ch

We will examine the Logical Link Control (top) sub-layer in 3. Layer 2 - The Data Link Layer this section of the course, so that we will quickly gain an Read [Tanenbaum96] Ch. 3. You can skim Section 3.5.2. understanding the exchange of basic frames of data. Much later in the course, after looking at this and basic store-and-forward This layer provides: networks, will we finally look at the complexities of networks • transmission of basic data frames over, based on shared media access. • and control of, The basic LLC topics that need to be covered are: a single hop link. This section only applies to non-multi-hop 1) framing transmissions. i.e. point-to-point transmission, or semi- 2) error detection and control (and it's subsidiary problem of broadcast (but not store + forward) networks. single-hop re-sequencing) There are two sub-layers to this layer: 3) flow control a) The top one does ‘logical link control’ and thus manages single-hop framing, errors, flow, and half-duplex turn control. TABLE OF CONTENTS - is located at end of the section. b) The bottom one manages media access control and is only present on broadcast (shared) media. It manages contention and multi-point turn control. NETWORK LAYER Logical Link Control (LLC) Sub-Layer DATA LINK Media Access Control (MAC) LAYER Sub-Layer PHYSICAL LAYER 3-1 3-2 3.1 Framing Since in asynchronous transmission a stream of characters is received, and in synchronous transmission a stream of bits is A ‘frame’ is the basic unit of data at ISO Level 2. -

Chapter 5 Peer-To-Peer Protocols and Data Link Layer

Chapter 5 Peer-to-Peer Protocols and Data Link Layer PART I: Peer-to-Peer Protocols Peer-to-Peer Protocols and Service Models ARQ Protocols and Reliable Data Transfer Flow Control Timing Recovery TCP Reliable Stream Service & Flow Control Chapter 5 Peer-to-Peer Protocols and Data Link Layer PART II: Data Link Controls Framing Point-to-Point Protocol High-Level Data Link Control Link Sharing Using Statistical Multiplexing Chapter Overview z Peer-to-Peer protocols: many protocols involve the interaction between two peers z Service Models are discussed & examples given z Detailed discussion of ARQ provides example of development of peer-to-peer protocols z Flow control, TCP reliable stream, and timing recovery z Data Link Layer z Framing z PPP & HDLC protocols z Statistical multiplexing for link sharing Chapter 5 Peer-to-Peer Protocols and Data Link Layer Peer-to-Peer Protocols and Service Models Peer-to-Peer Protocols zzz zzz z Peer-to-Peer processes execute layer-n protocol to provide service to n + 1 peer process n + 1 peer process layer-(n+1) z Layer-(n+1) peer calls SDU SDU layer-n and passes PDU Service Data Units n peer process n peer process (SDUs) for transfer z Layer-n peers exchange Protocol Data Units (PDUs) to effect transfer n – 1 peer process n – 1 peer process z Layer-n delivers SDUs to destination layer-(n+1) peer zzz zzz Service Models z The service model specifies the information transfer service layer-n provides to layer-(n+1) z The most important distinction is whether the service is: z Connection-oriented z Connectionless z Service model possible features: z Arbitrary message size or structure z Sequencing and Reliability z Timing, Pacing, and Flow control z Multiplexing z Privacy, integrity, and authentication Connection-Oriented Transfer Service z Connection Establishment z Connection must be established between layer-(n+1) peers z Layer-n protocol must: Set initial parameters, e.g. -

Introduction Many Data Links Transmit Continuous Sequences Of

ELEX 4550 : Wide Area Networks 2017 Fall Session PPP is lecture describes the Point-to-Point Protocol, a link-layer (Layer 2) protocol that is oen used to encapsulate IP packets when they are transmitted over data links that were not designed for packet transmission. is includes serial (“RS-232”), T-carrier (e.g. T1), and SONET links. Aer this lecture you should be able to: encapsulate a packet using PPP framing including adding and removing escape characters, generate a PPP frame for an IP packet, and decide whether a configuration item would be negotiated by the LCP, NCP or neither. PPP and it’s many optional features are defined Introduction in several IETF RFC’s including RFC1661 and RFC1662. Many data links transmit continuous sequences of bits or characters and have no way to mark the start or end of a packet. is includes RS-232 serial interfaces PPP Encapsulation and related links such as dial-up modem connections and links that were originally designed to carry TDM PPP uses a simple subset of HDLC to encapsulate PCM voice data such as T1 and SONET/SDH links. frames. In order to transmit groups of bytes such as an an PPP delimits frames by using a “flag” character, IP packet1 over such a link, the data link layer has to, 0x7e. An “escape” character, 0x7d, is also defined at a minimum, be able to separate bits or bytes into and is used as the first byte of a two-byte sequence frames. Other features such as support for indicating that is replaced by a single byte at the receiving end.