FOSDEM 2021 Presentation Kicad Project Status

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Pulsonix Design System V10.5 Update Notes

Pulsonix Design System V10.5 Update Notes 2 Pulsonix Version 10.5 Update Notes Copyright Notice Copyright ã WestDev Ltd. 2000-2019 Pulsonix is a Trademark of WestDev Ltd. All rights reserved. E&OE Copyright in the whole and every part of this software and manual belongs to WestDev Ltd. and may not be used, sold, transferred, copied or reproduced in whole or in part in any manner or in any media to any person, without the prior written consent of WestDev Ltd. If you use this manual you do so at your own risk and on the understanding that neither WestDev Ltd. nor associated companies shall be liable for any loss or damage of any kind. WestDev Ltd. does not warrant that the software package will function properly in every hardware software environment. Although WestDev Ltd. has tested the software and reviewed the documentation, WestDev Ltd. makes no warranty or representation, either express or implied, with respect to this software or documentation, their quality, performance, merchantability, or fitness for a particular purpose. This software and documentation are licensed 'as is', and you the licensee, by making use thereof, are assuming the entire risk as to their quality and performance. In no event will WestDev Ltd. be liable for direct, indirect, special, incidental, or consequential damage arising out of the use or inability to use the software or documentation, even if advised of the possibility of such damages. WestDev Ltd. reserves the right to alter, modify, correct and upgrade our software programs and publications without notice and without incurring liability. -

PLM Weekly Summary Editor: Cimdata News Team 15 January 2021 Contents Cimdata News

PLM Weekly Summary Editor: CIMdata News Team 15 January 2021 Contents CIMdata News ............................................................................................................................................ 2 An Enterprise Digital Transformation Platform – a CIMdata Commentary......................................................2 Aras’ Cloud Strategy – a CIMdata Blog Post ....................................................................................................5 CIMdata Announces its 2021 PLM Market & Industry Forum Series ..............................................................6 CIMdata to Host a Free Webinar on CAD Trends ............................................................................................7 NLign Analytics “Structural Lifecycle Digital Environment” Enables Model-Driven Product Quality – a CIMdata Commentary .......................................................................................................................................8 PTC’s Cloud Strategy – a CIMdata Blog Post ................................................................................................. 13 Acquisitions .............................................................................................................................................. 14 Accenture Acquires Real Protect, Brazil-Based Information Security Company ........................................... 14 Atos to acquire In Fidem to reinforce its cybersecurity position in the North American market .................... 15 Planview -

Circuitmaker 2000 (The Symbol Will Be Replaced by a Rectangle)

CircuitMaker® 2000 the virtual electronics lab™ CircuitMaker User Manual advanced schematic capture mixed analog/digital simulation Revision A Software, documentation and related materials: Copyright © 1988-2000 Protel International Limited. All Rights Reserved. Unauthorized duplication of the software, manual or related materials by any means, mechanical or electronic, including translation into another language, except for brief excerpts in published reviews, is prohibited without the express written permission of Protel International Limited. Unauthorized duplication of this work may also be prohibited by local statute. Violators may be subject to both criminal and civil penalties, including fines and/or imprisonment. CircuitMaker, TraxMaker, Protel and Tango are registered trademarks of Protel International Limited. SimCode, SmartWires and The Virtual Electronics Lab are trademarks of Protel International Limited. Microsoft and Microsoft Windows are registered trademarks of Microsoft Corporation. Orcad is a registered trademark of Cadence Design Systems. PADS is a registered trademark of PADS Software. All other trademarks are the property of their respective owners. Printed by Star Printery Pty Ltd ii Table of Contents Chapter 1: Welcome to CircuitMaker Introduction............................................................................................1-1 Required User Background..............................................................1-1 Required Hardware/Software...........................................................1-1 -

IDF Exporter IDF Exporter Ii

IDF Exporter IDF Exporter ii April 27, 2021 IDF Exporter iii Contents 1 Introduction to the IDFv3 exporter 2 2 Specifying component models for use by the exporter 2 3 Creating a component outline file 4 4 Guidelines for creating outlines 6 4.1 Package naming ................................................ 6 4.2 Comments .................................................... 6 4.3 Geometry and Part Number entries ...................................... 7 4.4 Pin orientation and positioning ........................................ 7 4.5 Tips on dimensions ............................................... 8 5 IDF Component Outline Tools 8 5.1 idfcyl ....................................................... 9 5.2 idfrect ...................................................... 10 5.3 dxf2idf ...................................................... 11 6 idf2vrml 12 IDF Exporter 1 / 12 Reference manual Copyright This document is Copyright © 2014-2015 by it’s contributors as listed below. You may distribute it and/or modify it under the terms of either the GNU General Public License (http://www.gnu.org/licenses/gpl.html), version 3 or later, or the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/), version 3.0 or later. All trademarks within this guide belong to their legitimate owners. Contributors Cirilo Bernardo Feedback Please direct any bug reports, suggestions or new versions to here: • About KiCad document: https://gitlab.com/kicad/services/kicad-doc/issues • About KiCad software: https://gitlab.com/kicad/code/kicad/issues • About KiCad software i18n: https://gitlab.com/kicad/code/kicad-i18n/issues Publication date and software version Published on January 26, 2014. IDF Exporter 2 / 12 1 Introduction to the IDFv3 exporter The IDF exporter exports an IDFv3 1 compliant board (.emn) and library (.emp) file for communicating mechanical dimensions to a mechanical CAD package. -

Release Notes: Desktop Edition

Release Notes: Desktop Edition AutoVue 19.2c2: November 30, 2007 Installation • Please make sure you have AutoVue 19.2c1 installed before upgrading to AutoVue 19.2c2. Note: If you have an older version of AutoVue installed (e.g. AutoVue 19.2), please uninstall it before installing AutoVue 19.2c1 and upgrading to AutoVue 19.2c2. MCAD Formats • Added font substitution for missing native fonts: • CATIA 4 and CATIA 5 • Pro/ENGINEER • Unigraphics • Added support for Unigraphics NX5. • Performed bugs fixes for Unigraphics and CATIA 5. EDA Formats • Added font substitution for missing native fonts: • Altium Protel • OrCAD Layout • Cadence Allegro Layout • Cadence Allegro IPF • Cadence Allegro Extract • Mentor Board Station • Mentor PADS • Zuken CADSTAR • P-CAD • PDIF AEC Formats • Added font substitution for missing native fonts: • AutoCAD • MicroStation 7 and MicroStation 8 • Performed bug fixes for AutoCAD. Release Notes - AutoVue Desktop Edition - 1 - November 30, 2007 AutoVue 19.2c1: September 30, 2007 Packaging and Licensing • Introduced separate installers for the following product packages: • AutoVue Office • AutoVue 2D, AutoVue 2D Professional • AutoVue 3D Professional-SME, AutoVue 3D Advanced, AutoVue 3D Professional Advanced • AutoVue EDA Professional • AutoVue Electro-Mechanical Professional • AutoVue DEMO • Customers are no longer required to enter license keys to install and run the product. • To install 19.2c1, users are required to first uninstall 19.2. MCAD Formats • General bug fixes for CATIA 5 EDA Formats • Performed maintenance and bug fixes for Allegro files. General • Enabled interface for customized resource resolution DLL to give integrators more flexibility on how to locate external resources. Sample source code and DLL is located in the integrat\VisualC\reslocate directory. -

Blueprint-PCB for PADS, Orcad, CADSTAR Or Altium Page 1 of 4

Industry Leading PCB BluePrint-PCB For PADS, Documentation Authoring Tool OrCAD, CADSTAR or Altium For the past several decades PCB CAD BluePrint is a feature rich, easy to use PCB documentation editor for creating tools have evolved to become superlative and maintaining PCB documentation. at PCB design. However, with respect to PCB Documentation they are woefully behind even the most rudimentary word Features and Functionality processor, or graphic editor application. Unlike the typical PCB CAD tool, BluePrint-PCB functionality includes: BluePrint was designed from the ground up to be a documentation editor. Directly import your PCB CAD design in ODB++ or PADS ASCII to initiate documentation authoring Create PCB Fabrication, PCB Assembly, Variant Assembly, PCB Use BluePrint to create assembly Assembly Process Step, Assembly Panel or other custom drawings process step documentation, variant Standardize your documentation with your own sheet borders, title assembly drawings, or component blocks, revision blocks, fabrication and assembly notes coordinate charts. Use assembly panel 3D viewing for enhanced visualization of design data design features to design and document PCB Stackup design with user defined material table and 3D modeling a custom assembly panel with mill tabs, Optional 3D PDF printing for sharing fully modeled PCB data web routes, pinning holes and fiducials. Create Mil-Aero documentation with automated GD&T compliant With BluePrint you can create custom dimensioning documentation to meet your specific Automated -

Industrial Circuit Board Design and Microprocessor Programming Bachelor of Science Thesis in Mechatronics

Industrial circuit board design and microprocessor programming Bachelor of Science thesis in Mechatronics FREDRIK HÖGBERG Department of Signals and Systems CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden 2017 REPORT NO. XXXX XXXX Industrial circuit boar! design and %icroprocessor pro$ram%in$ FREDRIK HÖGBERG Depart%ent of Signal and S'ste%s CH)*MERS UNI,ERSIT- OF TE(HNO*OG- Gothenbur$, S/eden 2017 Industrial circuit board design and microprocessor pro$ra%%in$ FREDRIK HÖGBERG FREDRIK HÖGBERG, 2017 Technical report no xxxx544 Depart%ent of Signals and S'ste%s Chal%ers +ni6ersit' of Technolo$' SE-412 96 G;tebor$ S/eden Telephone + 46 (0)31-772 1000 (o6er5 Hot Screen 2000 is an industrial heat press machine that can be used to attach screen prints on clothin$. This thesis will go in to details on ho/ the circuit board and pro$ra% was ma!e for this %achine. Chal%ers Reproservice G;tebor$. S/eden 2017 CHALMERS Signals and Systems, Bachelor@s Thesis XXXX5XX I Abstract The %ain obAect of this proAect is to design and %aBe circuitr' to control a industrial heat press %achine. The circuitr' consist of a 0 la'er boar! containin$ a %icro controller. displa' %odule. )( DC module. te%perature controller and electronics to control electromechanical devices. The fra%e of reference /ill $o through the basics steps in designin$ and %anufacturin$ electrical circ"itry /ith digital and analo$ technolo$y and explain the basics of the most com%on electrical components use! in circuitr' toda'. The fra%e of reference /ill also sho/ ho/ to create sche%atic and circuit design "sin$ Ki()D and ho/ to pro$ra% a Microchi& %icroprocessor in the C pro$ra%ing lan$"a$e. -

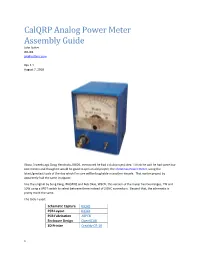

Calqrp Analog Power Meter Assembly Guide John Sutter W1JDS [email protected]

CalQRP Analog Power Meter Assembly Guide John Sutter W1JDS [email protected] Rev 1.1 August 7, 2018 About 3 weeks ago Doug Hendricks, KI6DS, mentioned he had a club project idea. I think he said he had some low cost meters and thought it would be good to spin an old project, the Christmas Power Meter, using the latest/greatest tools of the day which I’m sure will be laughable in another decade. That earlier project by apparently had the same instigator. Like the original by Song Kang, WA3AYQ and Bob Okas, W3CD, this version of the meter has two ranges, 1W and 10W using a SPDT switch to select between them instead of 2 BNC connectors. Beyond that, the schematic is pretty much the same. The tools I used: Schematic Capture KiCAD PCB Layout KiCAD PCB Fabrication AllPCB Enclosure Design OpenSCAD 3D Printer Creality CR-10 1 The Circuit As mentioned earlier the schematic matches the Christmas Power Meter pretty closely. SW1 is used to switch the power from the BNC connector into either the 10W load consisting of four 200 Ω 3 Watt carbon film resistors or the 1W load consisting of two 100 Ω ½ Watt carbon film resistors. The diodes are used as detectors with the resulting voltage filtered by the capacitors. The resistors are used to adjust the full-scale current to 200 μA. More on that later. FIGURE 1 SCHEMATIC A germanium diode was used on the 1 W range due to its lower voltage drop. More on that later. If you decide to use a through hole switch, the maximum shaft diameter is 6.3 mm. -

Minor Changes and Bug Fixes

List of fixed bugs in DipTrace 4.1.3.1 if compared to 4.1.3.0 PCB Layout 1. If IPC-7351 models are used, STEP export does not work. 2. When entering text into table cells "Shift + U" works as a Hotkey. 3. When importing KiCad 5.1 files, SMD pads on the Bottom layer may be imported incorrectly. Schematics 1. When entering text into table cells "Shift + U" works as a Hotkey.. 2. Back Annotate does not update supplier information. List of fixed bugs in DipTrace 4.1.3.0 if compared to 4.1.2.0 General 1. Snap EDA: multiple clicks for page switching result in a long "freezing". PCB Layout 4. The panelization parameters are reset when opening a schematic file in the PCB Layout after starting. 5. D-shape pads are displayed incorrectly in the Mirror mode. 6. The Highlight Net for the Obround and D-shape pads is displayed incorrectly in the Mirror mode. 7. TrueType text is shifted in BOM HTML. 8. DXF with multilayer blocks is imported incorrectly 9. Export of arcs with a very small angle and extra-large radius to Gerber has been changed. 10. Chamfer of the corners of a rectangular board outline may result in incorrect formation of outlines in Gerber when panelizing with Edge Rails. 11. After changing any of the markings parameters for a group of selected objects, the marking for selected Mounting Hole and Fiducial may appear. 12. Dimension objects are not updated automatically after changing the shape dimensions in the shape properties. -

CADSTAR FPGA TRAINING Agenda

CADSTAR FPGA TRAINING Agenda 1. ALDEC Corporate Overview 2. Introduction to Active-HDL 3. Design Entry Methods 4. Efficient Design Management 5. Design Verification – Running Simulation 6. Design Verification- Debugging 7. Synthesis and Implementation in Flow Manager 8. Using the PCB interface Corporate Overview Aldec Focus - Background • Founded 1984 – Dr. Stanley Hyduke • Privately held, profitable and 100% product revenue funded • Leading EDA Technology – VHDL and Verilog Simulation – SystemVerilog – SystemC Co-Verification – Server Farm Manager – IP Cores – Hardware assisted Acceleration/Emulation and Prototyping • Over 30,000 active licenses worldwide • Several key Patents in Verification Technology • Office Locations: – Direct Sales and Support • United States • Japan • Canada • France • ROW – Distribution Channel Corporate Milestones Technology Focus Design Creation • Text, block diagram and state diagram entry • Automatic testbench generation • Automatically created parameterized blocks • Variety of IP cores Verification • Multiple language support (VHDL, [System]Verilog, C++, SystemC) • Assertions (OpenVera, PSL, SystemVerilog) • Direct compilation and common kernel simulation • Co-simulation Interfaces(VHPI/VPI, Matlab/Simulink, SWIFT, …) Technology Focus – cont. Hardware Validation • Hardware assisted acceleration of HDL simulation • Emulation and ASIC prototyping • Hardware / software co-simulation (Embedded Systems, SoC) Niche Solution • Actel CoreMP7 Designs Co-verification (ARM7) • DO-254 Verification Solution • Actel RTAX-S/SL -

Low-Cost Industrial Controller Based on the Raspberry Pi Platform

Low-cost Industrial Controller based on the Raspberry Pi platform Gustavo Mendonça de Morais Rabelo Vieira Dissertation presented to the School of Technology and Management of Bragança to obtain the Master Degree in Industrial Engineering. Work oriented by: Professor PhD Paulo Leitão Professor PhD José Barbosa Professor MsC Ulisses da Graça Bragança 2018-2019 ii Low-cost Industrial Controller based on the Raspberry Pi platform Gustavo Mendonça de Morais Rabelo Vieira Dissertation presented to the School of Technology and Management of Bragança to obtain the Master Degree in Industrial Engineering. Work oriented by: Professor PhD Paulo Leitão Professor PhD José Barbosa Professor MsC Ulisses da Graça Bragança 2018-2019 iv Dedication Este trabalho é dedicado a mulher mais trabalhadora que conheço, a quem admiro muito e me inspira imensamente desde criança, minha querida e amada avó Terezinha Mendonça de Morais, singularmente importante em minha vida. À minha mãe Janaína, à minha tia Gildete, melhores amigas que sempre me ofereceram apoio a perseverar em minhas conquistas. Aos meus queridos irmãos mais novos, Lucas e Vitor que me orgulham pelas pessoas que estão se tornando e por toda a companhia que tive o prazer de desfrutar durante o nosso crescimento. v vi Acknowledgements Agradeço a todo o apoio e suporte que tive da minha família por me proporcionar a oportunidade de chegar até aqui. Aos meus professores orientadores José Barbosa e Paulo Leitão pela rica e experiente orientação. A todos os amigos, colegas e professores que foram sumariamente importantes para o sucesso da realização deste trabalho. vii viii Abstract The low-cost automation field exhibits the need of innovation both in terms of hardware and software. -

Getting Started with Orcad Capture

1 Lesson 1: Getting Started with OrCAD Capture Lesson Objectives • Discuss design flow using OrCAD Capture • Learn how to start OrCAD Capture • The OrCAD Capture “Start Page” • Open an existing Project • Explore the user interface • Describe project structure • Select and edit objects Cadence Tools Overview May, 2011 OrCAD Capture Version 16.5 1-1 Getting Started with OrCAD Capture Lesson 1 The OrCAD Capture tool provides support for programmable logic design. OrCAD Capture is tightly integrated with the OrCAD and Allegro PCB Editor design, SPECCTRAQuest™ for high-speed circuit analysis, and Advanced Package Designer for multi-chip and single-chip modules. OrCAD Capture supports digital simulation using Verilog® or VHDL models, or analog simulation with PSpice A/D. OrCAD Capture also uses a Cadence OrCAD Component Information System (Cadence OrCAD Capture CIS) to integrate your board-level design with existing in-house part procurement and manufacturing databases. The procedures included within this training guide can be used with both the standard OrCAD Capture application and OrCAD Capture CIS. More Information OrCAD Capture supports programmable logic design by accessing synthesis and simulation tools, and by providing libraries for the most popular FPGA/CPLD vendors. Increased integration provides easy access to NC VHDL Desktop for simulation. Further, OrCAD Capture includes functionality for generating simulation test benches and provides numerous coding samples that you can use when developing your designs and test benches. If you have installed Synplify on your system, you can launch it from within the OrCAD Capture user interface, create a Synplify project, and invoke the tool on your programmable logic design.OrCAD Capture also launches the place-and-route tool set appropriate for the target vendor (provided that the tool set is installed on your computer).