A Highly Configurable High-Level Synthesis Functional Pattern Library

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Richard S. Uhler

Smten and the Art of Satisfiability-Based Search by Richard S. Uhler B.S., University of California, Los Angeles (2008) S.M., Massachusetts Institute of Technology (2010) Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY September 2014 c Massachusetts Institute of Technology 2014. All rights reserved. Author.............................................................. Department of Electrical Engineering and Computer Science August 22, 2014 Certified by. Jack B. Dennis Professor of Computer Science and Engineering Emeritus Thesis Supervisor Accepted by . Leslie A. Kolodziejski Chairman, Committee for Graduate Students 2 Smten and the Art of Satisfiability-Based Search by Richard S. Uhler Submitted to the Department of Electrical Engineering and Computer Science on August 22, 2014, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science Abstract Satisfiability (SAT) and Satisfiability Modulo Theories (SMT) have been leveraged in solving a wide variety of important and challenging combinatorial search prob- lems, including automatic test generation, logic synthesis, model checking, program synthesis, and software verification. Though in principle SAT and SMT solvers sim- plify the task of developing practical solutions to these hard combinatorial search problems, in practice developing an application that effectively uses a SAT or SMT solver can be a daunting task. SAT and SMT solvers have limited support, if any, for queries described using the wide array of features developers rely on for describing their programs: procedure calls, loops, recursion, user-defined data types, recursively defined data types, and other mechanisms for abstraction, encapsulation, and modu- larity. -

Bash Guide for Beginners

Bash Guide for Beginners Machtelt Garrels Garrels BVBA <tille wants no spam _at_ garrels dot be> Version 1.11 Last updated 20081227 Edition Bash Guide for Beginners Table of Contents Introduction.........................................................................................................................................................1 1. Why this guide?...................................................................................................................................1 2. Who should read this book?.................................................................................................................1 3. New versions, translations and availability.........................................................................................2 4. Revision History..................................................................................................................................2 5. Contributions.......................................................................................................................................3 6. Feedback..............................................................................................................................................3 7. Copyright information.........................................................................................................................3 8. What do you need?...............................................................................................................................4 9. Conventions used in this -

PJM Command Line Interface

PJM Command Line Interface PJM Interconnection LLC Version 1.5.1 11-18-2020 PJM Command Line Interface Table of Contents Purpose ..................................................................................................................................................................................... 4 System Requirements ............................................................................................................................................................... 4 Release History ......................................................................................................................................................................... 4 Usage ........................................................................................................................................................................................ 5 Standalone Application ......................................................................................................................................................... 5 Example Standalone Execution ....................................................................................................................................... 5 Parameter Details ............................................................................................................................................................. 7 Password Encryption ....................................................................................................................................................... -

FPGA Programming for the Masses

practice DOI:10.1145/2436256.2436271 used to implement sequential logic. Article development led by queue.acm.org Apart from the homogeneous array of logic cells, an FPGA also contains discrete components such as BRAMs The programmability of FPGAs must improve (block RAMs), digital signal process- if they are to be part of mainstream computing. ing (DSP) slices, processor cores, and various communication cores (for ex- BY DavID F. BACON, RODRIC RabbaH, AND SUNIL SHUkla ample, Ethernet MAC and PCIe). BRAMs, which are specialized mem- ory structures distributed throughout the FPGA fabric in columns, are of par- ticular importance. Each BRAM can FPGA hold up to 36Kbits of data. BRAMs can be used in various form factors and can be cascaded to form a larger logical memory structure. Because of the dis- Programming tributed organization of BRAMs, they can provide terabytes of bandwidth for memory bandwidth-intensive applica- tions. Xilinx and Altera dominate the PLD market, collectively holding more for the Masses than an 85% share. FPGAs were long considered low- volume, low-density ASIC replace- ments. Following Moore’s Law, how- ever, FPGAs are getting denser and faster. Modern-day FPGAs can have up to two million logic cells, 68Mbits WHEN LOOKING AT how hardware influences of BRAM, more than 3,000 DSP slices, computing performance, we have general-purpose and up to 96 transceivers for imple- menting multigigabit communication processors (GPPs) on one end of the spectrum and channels.23 The latest FPGA families application-specific integrated circuits (ASICs) on the from Xilinx and Altera are more like a system-on-chip (SoC), mixing dual- other. -

TASSEL 3.0 / 4.0 Pipeline Command Line Interface: Guide to Using Tassel Pipeline

TASSEL 3.0 / 4.0 Pipeline Command Line Interface: Guide to using Tassel Pipeline Terry Casstevens ([email protected]) Institute for Genomic Diversity, Cornell University, Ithaca, NY 14853-2703 March 28, 2014 Prerequisites ............................................................................................................................................................ 1 Source Code ............................................................................................................................................................ 1 Install ....................................................................................................................................................................... 1 Execute .................................................................................................................................................................... 1 Increasing Heap Size ............................................................................................................................................... 2 Examples ................................................................................................................................................................. 2 Examples (XML Configuration Files) .................................................................................................................... 2 Usage ...................................................................................................................................................................... -

Design Automation for Streaming Systems

Design Automation for Streaming Systems Eylon Caspi Electrical Engineering and Computer Sciences University of California at Berkeley Technical Report No. UCB/EECS-2005-27 http://www.eecs.berkeley.edu/Pubs/TechRpts/2005/EECS-2005-27.html December 16, 2005 Copyright © 2005, by the author(s). All rights reserved. Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Design Automation for Streaming Systems by Eylon Caspi B.S. (University of Maryland, College Park) 1996 M.S. (University of California, Berkeley) 2000 A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Computer Science in the GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY Committee in charge: Professor John Wawrzynek, Chair Professor Edward A. Lee Professor Robert Jacobsen Fall 2005 Design Automation for Streaming Systems Copyright c 2005 by Eylon Caspi Abstract Design Automation for Streaming Systems by Eylon Caspi Doctor of Philosophy in Computer Science University of California, Berkeley Professor John Wawrzynek, Chair RTL design methodologies are struggling to meet the challenges of modern, large system design. Their reliance on manually timed design with fully exposed device resources is laborious, restricts reuse, and is increasingly ineffective in an era of Moore’s Law expansion and growing interconnect delay. -

Review of FPD's Languages, Compilers, Interpreters and Tools

ISSN 2394-7314 International Journal of Novel Research in Computer Science and Software Engineering Vol. 3, Issue 1, pp: (140-158), Month: January-April 2016, Available at: www.noveltyjournals.com Review of FPD'S Languages, Compilers, Interpreters and Tools 1Amr Rashed, 2Bedir Yousif, 3Ahmed Shaban Samra 1Higher studies Deanship, Taif university, Taif, Saudi Arabia 2Communication and Electronics Department, Faculty of engineering, Kafrelsheikh University, Egypt 3Communication and Electronics Department, Faculty of engineering, Mansoura University, Egypt Abstract: FPGAs have achieved quick acceptance, spread and growth over the past years because they can be applied to a variety of applications. Some of these applications includes: random logic, bioinformatics, video and image processing, device controllers, communication encoding, modulation, and filtering, limited size systems with RAM blocks, and many more. For example, for video and image processing application it is very difficult and time consuming to use traditional HDL languages, so it’s obligatory to search for other efficient, synthesis tools to implement your design. The question is what is the best comparable language or tool to implement desired application. Also this research is very helpful for language developers to know strength points, weakness points, ease of use and efficiency of each tool or language. This research faced many challenges one of them is that there is no complete reference of all FPGA languages and tools, also available references and guides are few and almost not good. Searching for a simple example to learn some of these tools or languages would be a time consuming. This paper represents a review study or guide of almost all PLD's languages, interpreters and tools that can be used for programming, simulating and synthesizing PLD's for analog, digital & mixed signals and systems supported with simple examples. -

Chapter 5. Writing Your Own Shell

Chapter 5. Writing Your Own Shell You really understand something until you program it. GRR Introduction Last chapter covered how to use a shell program using UNIX commands. The shell is a program that interacts with the user through a terminal or takes the input from a file and executes a sequence of commands that are passed to the Operating System. In this chapter you are going to learn how to write your own shell program. Shell Programs A shell program is an application that allows interacting with the computer. In a shell the user can run programs and also redirect the input to come from a file and output to come from a file. Shells also provide programming constructions such as if, for, while, functions, variables etc. Additionally, shell programs offer features such as line editing, history, file completion, wildcards, environment variable expansion, and programing constructions. Here is a list of the most popular shell programs in UNIX: sh Shell Program. The original shell program in UNIX. csh C Shell. An improved version of sh. tcsh A version of Csh that has line editing. ksh Korn Shell. The father of all advanced shells. bash The GNU shell. Takes the best of all shell programs. It is currently the most common shell program. In addition to commandline shells, there are also Graphical Shells such as the Windows Desktop, MacOS Finder, or Linux Gnome and KDE that simplify theDraft use of computers for most of the users. However, these graphical shells are not substitute to command line shells for power users who want to execute complex sequences of commands repeatedly or with parameters not available in the friendly, but limited graphical dialogs and controls. -

Generating Configurable Hardware from Parallel Patterns

Generating Configurable Hardware from Parallel Patterns Raghu Prabhakar David Koeplinger Kevin Brown HyoukJoong Lee Christopher De Sa Christos Kozyrakis Kunle Olukotun Pervasive Parallelism Laboratory Stanford University {raghup17, dkoeplin, kjbrown, hyouklee, cdesa, kozyraki, kunle}@stanford.edu Abstract systems [23] and machine learning algorithms like deep belief networks [31, 32]. In recent years the computing landscape has seen an in- creasing shift towards specialized accelerators. Field pro- The performance and energy advantages of FPGAs are now grammable gate arrays (FPGAs) are particularly promising motivating the integration of reconfigurable logic into data as they offer significant performance and energy improvements center computing infrastructures. Both Microsoft [37] and compared to CPUs for a wide class of applications and are Baidu [31] have recently announced such systems. These far more flexible than fixed-function ASICs. However, FPGAs systems have initially been in the form of banks of FPGA are difficult to program. Traditional programming models accelerators which communicate with CPUs through Infini- for reconfigurable logic use low-level hardware description band or PCIe [28]. Work is also being done on heterogeneous languages like Verilog and VHDL, which have none of the pro- motherboards with shared CPU-FPGA memory [22]. The re- ductivity features of modern software development languages cent acquisition of Altera by Intel suggests that systems with but produce very efficient designs, and low-level software lan- tighter, high performance on-chip integration of CPUs and guages like C and OpenCL coupled with high-level synthesis FPGAs are now on the horizon. (HLS) tools that typically produce designs that are far less The chief limitation of using FPGAs as general purpose efficient. -

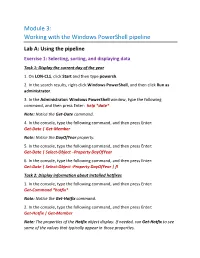

Working with the Windows Powershell Pipeline

Module 3: Working with the Windows PowerShell pipeline Lab A: Using the pipeline Exercise 1: Selecting, sorting, and displaying data Task 1: Display the current day of the year 1. On LON-CL1, click Start and then type powersh. 2. In the search results, right-click Windows PowerShell, and then click Run as administrator. 3. In the Administrator: Windows PowerShell window, type the following command, and then press Enter: help *date* Note: Notice the Get-Date command. 4. In the console, type the following command, and then press Enter: Get-Date | Get-Member Note: Notice the DayOfYear property. 5. In the console, type the following command, and then press Enter: Get-Date | Select-Object –Property DayOfYear 6. In the console, type the following command, and then press Enter: Get-Date | Select-Object -Property DayOfYear | fl Task 2: Display information about installed hotfixes 1. In the console, type the following command, and then press Enter: Get-Command *hotfix* Note: Notice the Get-Hotfix command. 2. In the console, type the following command, and then press Enter: Get-Hotfix | Get-Member Note: The properties of the Hotfix object display. If needed, run Get-Hotfix to see some of the values that typically appear in those properties. 3. In the console, type the following command, and then press Enter: Get-Hotfix | Select-Object –Property HotFixID,InstalledOn,InstalledBy 4. In the console, type the following command, and then press Enter: Get-Hotfix | Select-Object –Property HotFixID,@{n='HotFixAge';e={(New- TimeSpan –Start $PSItem.InstalledOn).Days}},InstalledBy Task 3: Display a list of available scopes from the DHCP server 1. -

Introduction to Linux/Unix

Introduction to Linux/Unix Xiaoge Wang, ICER [email protected] Feb. 4, 2016 How does this class work • We are going to cover some basics with hands on examples. • Exercises are denoted by the following icon: • Bold means commands which I expect you type on your terminal in most cases. Green and red sticky Use the sJcKy notes provided to help me help you. – No s%cky = I am worKing – Green = I am done and ready to move on (yea!) – Red = I am stucK and need more Jme and/or some help Agenda • IntroducJon • Linux – Commands • Navigaon • Get or create files • Organizing files • Closer looK into files • Search files • Distribute files • File permission • Learn new commands – Scripts • Pipeline • Make you own command • Environment of a shell • Summary Agenda • Linux – Commands • Navigaon • Get or create files • Organizing files • Closer looK into files • Search files • Distribute files • File permission • Learn new commands – Scripts • Pipeline • Make you own command • Environment of a shell • Summary Introduction • Get ready for adventure? – TicKet(account)? • Big map – Linux/Unix – Shell • Overview of the trail – Commands – Simple Shell script – Get ready for HPC. Exercise 0: Get ready • Connect to HPCC (gateway) – $ ssh [email protected] • Windows users MobaXterm • Mac users Terminal • Linux users? • Read important message – $ mod • Go to a development node – $ ssh dev-nodename Message of the day (mod) • Mac Show screen Big picture Shell Shell Big picture • Shell – CLI ✔ – GUI OS shell example Overview of the trail • Commands • Simple Shell script • Get ready for HPC Linux shell tour Ready? GO! Agenda • IntroducJon – Scripts • Pipeline • Make you own command • Environment of a shell • Summary Example 1: Navigation • TasK: Wander around on a node. -

Unix Tools As Visual Programming Components in a GUI-Builder

Unix Tools as Visual Programming Components Ý in a GUI-builder Environment £ Diomidis Spinellis Department of Management Science and Technology Athens University of Economics and Business Patision 76, GR-104 34 Athens, Greece email: [email protected] September, 2001 Abstract Introduction A number of environments support the visual composition Development environments based on ActiveX controls and of graphical user interfaces (GUIs) using components with a JavaBeans are marketed as “visual programming” plat- predefined set of interfaces. In addition, technologies such forms; in practice their visual dimension is limited to the as ActiveX and JavaBeans allow the development of visual design and implementation of an application’s graphical components (typically GUI elements) that can be seamlessly user interface (GUI. The availability of sophisticated GUI incorporated into an integrated development environment development environments and visual component develop- (IDE) and subsequently used in application development. In ment frameworks is now providing viable platforms for this article we present how visual IDEs and components can implementing visual programming within general-purpose be extended beyond GUI development to support visual pro- platforms, i.e. for the specification of non-GUI program gramming for a particular domain. functionality using visual representations. We describe A visual programming language can be informally de- how specially-designed reflective components can be used in an industry-standard visual programming environment fined as a programming language with a syntax that in- cludes visual expressions such as diagrams, free-hand to graphically specify sophisticated data transformation sketches, icons, or graphical manipulations [1]. Visual pipelines that interact with GUI elements. The components are based on Unix-style filters repackaged as ActiveX con- programming approaches aim towards easing the program- ming learning curve or enhancing programming productiv- trols.