Fier for Ultra-Wideband (Uwb) Transmitter S

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Downloaded (Thus Far, by More Than 262 Million People) Software Such As Skype

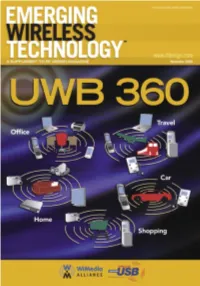

Consortium Standards Bulletin A ConsortiumInfo.org publication February 2006 Vol V, No. 2 FEATURE ARTICLE CASE STUDY: THE UNRULY EMERGENCE OF THE DIGITAL HOME Andrew Updegrove Abstract: Although basic electrical devices like thermostats, phones and radios entered our dwellings many decades ago, the long-awaited vision of the "digital home" is only now becoming a reality. The emergence of the futuristic home, controlled by and for the fulfillment of the comfort, safety and enjoyment of its owners, has become possible only with the development of the hundreds of telecommunications, wireless, data format, networking and other standards that have been created by scores of accredited standards development organizations and unaccredited consortia, some venerable, and others new and created specifically for this purpose. An examination of how this new standards development ecosystem has evolved demonstrates how complex standards infrastructures come into existence through the reordering of relationships among existing, and the formation of new, standard setting organizations. Such a review also illustrates how participants behave when commercial opportunities are great, and the stakes for success (or failure) are high. Introduction: Through the coincidental maturation of a variety of technologies, the New Year has brought a rash of news stories and product announcements relating to innovations in digital home technology. All at once, multi-year research, standards development and commercialization efforts in video delivery and storage technology, wireless services (both "last mile" and in-home), multiple types of display technology, and new PC capabilities are converging at roughly the same time, allowing long- anticipated innovations in home services and systems to become available to consumers. -

High-Speed Wireless Personal Area Networks: an Application of UWB Technologies

7 High-Speed Wireless Personal Area Networks: An Application of UWB Technologies H. K. Lau The Open University of Hong Kong Hong Kong 1. Introduction Recently, a large number of wireless networks are being developed and deployed in the market. According to the communication range, wireless networks can be classified into wireless wide area networks (WWANs), wireless metropolitan area networks (WMANs), wireless local area networks (WLANs), wireless personal area networks (WPANs), and wireless body area networks (WBANs). With the advances in wireless technologies, latest generation of WPANs can provide a data rate of hundreds (or even thousands) of Mbps at a distance of less than 10 meters. Ultra-wideband (UWB) is an emerging technology that offers distinct advantages, e.g. high bandwidth and small communication ranges, for WPAN applications (Park & Rappaport, 2007; Chong et al., 2006; Fontana, 2004; Intel, 2004; Porcino & Hirt, 2003). One of the ‘killer’ applications of high-speed WPAN is wireless video area network (WVAN) that offers wireless transmission of high-definition videos (several Gbps) within a small communication distance (Singh et al., 2008; Wirelesshd 2009; Whdi 2009). This chapter provides a comprehensive summary on the latest development and standardization progress of high-speed WPANs. There are seven sections in this chapter. The first section describes the background of WPANs and introduces the IEEE networking standards for WPAN. The second section discusses characteristics of UWB signals and explains why they are particularly suitable for high-speed WPAN applications. The third section discusses technical challenges and standardization issues. The fourth section reports on the latest development of high-speed WPANs. -

Distributed Medium Access Control (Mac) for Wireless Networks

DISTRIBUTED MEDIUM ACCESS CONTROL (MAC) FOR WIRELESS NETWORKS Making High-Speed Wireless A Reality ... MAC SPECIFICATION: RELEASE 1.5 DECEMBER 1, 2009 NOTICE The WiMedia Alliance, Inc. (WiMedia) disclaims any and all warranties, whether expressed or implied, including (without limitation) any implied warranties of merchantability or fitness for a particular purpose. WiMedia reserves the right to make changes to the document without further notice. Copyright © 2009 WiMedia Alliance, Inc. All Rights Reserved. December 1, 2009 MAC Specification: Release 1.5 ii WiMedia Limited Copyright License Agreement By receiving, installing, copying, reviewing or otherwise using the WiMedia Distributed Medium Access Control for Wireless Networks Specification (the "Specification"), you (the “Specification Recipient”) agree to the terms and conditions of this WiMedia Limited Copyright License Agreement (the “Agreement”) by and between the WiMedia Alliance, Inc. (“WiMedia”) and Specification Recipient. NO WIMEDIA PROMOTER, CONTRIBUTOR OR ADOPTER MEMBER SHALL BE BOUND TO THE TERMS OR CONDITIONS OF THIS AGREEMENT WHILE IT IS A PROMOTER, CONTRIBUTOR OR ADOPTER MEMBER. THIS AGREEMENT DOES BIND ALL WIMEDIA SUPPORTER MEMBERS AND NON-MEMBERS. 1. The Specification. “Specification” shall mean this WiMedia Logical Link Control Protocol Specification document. WiMedia reserves the right to change the Specification at any time without notice to Specification Recipient. 2. Limited Copyright Grant. Provided Specification Recipient complies with all terms and conditions of this Agreement, WiMedia grants Specification Recipient a non-exclusive, revocable, temporary, royalty-free, personal copyright license to copy, display and distribute the Specification. 3. Other Restrictions. Specification Recipient shall not disclose the Specification without prominently displaying the terms of this Agreement with the Specification and binding each recipient to the terms of this Agreement. -

Wimedia Ultra-Wideband: Efficiency Considerations of the Effects of Protocol Overhead on Data Throughput

WiMedia Ultra-wideband: Efficiency Considerations of the Effects of Protocol Overhead on Data Throughput © January 2009. All Rights Reserved. Contributed by WiMedia member company Introduction Abstract The WiMedia UWB specifications provide the technical details of Today’s wireless applications demand more band- the operation of a 480Mb/s PHY and a fully distributed MAC. The width than ever. The WiMedia Ultrawideband (UWB) very high data rates are achieved at very low transmitted power by specifications are the most advanced high performance occupying very large amounts of spectrum but using very low power wireless specifications available for low cost, low power, spectral density. consumer and information technology products. The WiMedia UWB specifications include: Any communications scheme which transfers data • A PHY specification describing the structure of transmission on the across a network cannot expect to utilize the full band- radio channel width of the medium since some data is required to • A MAC specification describing how devices use a radio channel to describe the content of the data, routing information establish communications amongst them. and other protocol needs. This document investigates the sources of protocol overhead inherent in implemen- The WiMedia PHY Channel tations of the WiMedia UWB specifications. We explain The WiMedia PHY transmits a waveform constructed from the the structure of the Physical Layer (PHY) frame and output of an IFFT function to produce an ODFM symbol. All symbols how the Medium Access Control (MAC) protocol uses are the same length and have an effective raw data rate of 640Mb/s. the frame to carry its very high performance data. -

High Speed Bluetooth

TM for the short range connectivity environment Video enabled September 2006 HIGH SPEED BLUETOOTH THIS ISSUE A NEW DAWN SHIFTING INTO HIGH GEAR BLUETOOTH – THE UNDERLYING SUCCESS OF UWB? MOTOROLA’S VISION FOR HIGH SPEED BLUTOOTH sponsored by 2 www.click.co.uk a new dawn This issue of Incisor is dedicated to an important development that is taking place now in the short range wireless market. It has been produced in partnership with three industry-leading organisations with whom Incisor enjoys a close working relationship. These are the Bluetooth Special Interest Group, CSR and Motorola. The development that we are focusing on concerns the alliance that has been created between two wireless technologies – Bluetooth and Ultra-Wideband (UWB). Few would dispute that Bluetooth is the de facto standard for short range wireless connectivity, and the master of the Wireless Personal Area Network or WPAN. This is a fast-moving world though, and today’s mobile devices are encouraging us to move ever larger amounts of data around. Bluetooth needed a higher speed of data transfer if it was to retain control of the WPAN. In March this year the Bluetooth SIG announced that it would join forces with the WiMedia Alliance version of UWB, which offers very high data rates and very low power consumption. We are now working towards the launch of what is currently known as High Speed Bluetooth. Within this special issue we use the multi-media capability of our magazine to include video as well as conventional editorial material. We present interviews with three senior executives – one each from the Bluetooth Special Interest Group, CSR and Motorola. -

Technical Considerations for Co-Locating Uwb and Gps Radios

TECHNICAL CONSIDERATIONS FOR CO-LOCATING UWB AND GPS RADIOS by TYLER H. VAN SLYKE B.S., Kansas State University, 2006 A THESIS submitted in partial fulfillment of the requirements for the degree MASTER OF SCIENCE Department of Electrical and Computer Engineering College of Engineering KANSAS STATE UNIVERSITY Manhattan, Kansas 2009 Approved by: Co-Major Professor William B. Kuhn Approved by: Co-Major Professor Balasubramaniam Natarjan ABSTRACT Excitement about using ultra-wideband (UWB) technology for networking has grown considerably over the last few years. UWB has several strengths, including high data rates, security, and robustness in multipath environments. Despite these benefits, UWB has been scrutinized for its potential to interfere with narrowband technologies like the Global Positioning System (GPS). Until recently, much of the literature about UWB and GPS compatibility has been published on the basis of theoretical analysis alone. We have investigated the compatibility of UWB and GPS signals using theoretical analysis as well as laboratory measurements with a consumer GPS receiver and a WiMedia UWB device. We conclude from our tests that the UWB device does emit interference in the GPS L1 band, but the interference is low enough that careful antenna and chipset placement could allow UWB and GPS radios to coexist in a single product. Also, we have evaluated several UWB antennas to determine their fitness for use in a handheld electronic product. We find that the antennas’ gain pattern and return loss do not have a significant effect upon the data throughput of the UWB system. Thus, we infer that the indoor environment is highly dispersive and that the UWB system is able to exploit multipath propagation. -

Wireless HDMI

Trash Your Cables! Organize your desk, unclutter your office, even move video wirelessly! New technologies promise the moon, but when will they deliver? BY ANNE LOUISE BANNON ome folks start talking wire- high-definition multimedia interface, has become less and you can almost see the vi- the de facto standard (ignoring the minor dif- sions of connected homes dancing ference between HDmi 1.0 and 1.3, of course…). in their heads. Video, phone calls, High-def tV sets have one, two, or even three and network packets enter through ports. true HDmi is a single point-to-point con- a single box, from either the cable nection over a cable, with a chip at either end of or satellite company. from there, the link that lets components speak to each oth- five tVs receive high definition video from a er. it can instantaneously and securely transmit variety of sources, including a digital video re- an uncompromised high-definition video signal corder, the internet, a PC, a game console, and a from various units, such as a set-top box, DVr, digital video camera all without wires. the sur- PC, or game console, along with as many as eight round sound system also connects wirelessly. all channels of digital audio. controlled by a single remote in each room. there are significant advantages to wired con- to hear them talk, we’re even now stepping nections, of course, particularly HDMI. they are into a wireless nirvana; products will hit the mar- very fast, practically instantaneous—a significant ket by the end of this year. -

802.15 Personal Area Networks File:///F:/Www/Cse574-06/Ftp/Wpans/Index.Html

802.15 Personal Area Networks file:///F:/www/cse574-06/ftp/wpans/index.html Greg Hackmann, [email protected] Abstract Recently, low-power wireless networking standards like 802.15.1 (Bluetooth) have driven consumer interest in personal area networks (PANs). These networks are designed for inexpensively connecting low-power devices located within 1 m to 100 m of each other. In this paper, we discuss recent evolutions to the Bluetooth standard, as well as two emerging PAN standards: 802.15.4/ZigBee, and Ultra-Wide Band. We provide a high-level summary of how these standards operate, as well as a brief discussion of what to expect from each technology in the future. See also: Table of Contents 1 Introduction 2 802.15.1 (Bluetooth) 2.1 Transport Layer 2.1.1 Radio Layer 2.1.2 Baseband and Link Layers 2.2 Middleware Layer 2.3 Bluetooth Security 2.4 Bluetooth 2.0 EDR 2.5 Applications and Future Outlook 3 802.15.4/ZigBee 3.1 802.15.4 PHY and MAC Layers 3.2 ZigBee 3.3 802.15.4 Security 3.4 Applications and Future Outlook 4 Ultra-Wide Band 4.1 Direct Sequence-UWB 4.2 Multi-Band OFDM 4.3 UWB Security 4.4 Standardization Efforts 4.5 Applications and Future Outlook 5 Summary References List of Acronyms 1 Introduction Wireless networking standards like 802.11b and Wi-Max typically focus on providing PC-to-PC or PC-to-ISP connectivity over the range of a building or a metropolitan area. However, many applications have far less stringent range requirements, such as connecting peripherals wirelessly to a mobile device or adding components to a home theater system. -

Author Guidelines for 8

RF Lecture Series Modulation Fundamentals 6 Introduction to WiMedia Alliance UWB (Wireless USB) 802.15.3a Modulation Standard Scott Chesnut Verigy 1. Introduction This paper describes a Multiband-Orthogonal Frequency Division Multiplex (MB-OFDM) implementation of Ultra-Wideband (UWB) technologies. Ultra-wideband (aka UWB, ultra-wide band, ultraband, etc.) is a radio technology that can be used at very low energy levels for short-range high-bandwidth communications by using a large portion of the radio spectrum. Since the 1970s UWB has traditional applications in military focused non cooperative radar imaging. Such applications targeted sensor data collection, precision locating, tracking and targeting applications. Basically warfare related applications. But recently, the WiMedia Alliance has planned widespread implementation of certified wireless USB and possibly next-generation Bluetooth 3.0 products, using multi-band orthogonal division modulation (MB-OFDM)-based ultra-wideband (UWB) physical layer (PHY). It will target the Wireless Personal Area Network (WPAN) civilian market and will span the frequency ranges of 3.1GHz to 10.6GHz. In these writings the basics of the IEEE 802.15.3a indoor operation standard will be described. The motivations for its use, and architectural comparisons to narrow band transceivers will be considered. Then, limitations to its omnipresence are visited, and finally, a thorough overview of the UWB modulation fundamentals is described. This report can not be comprehensive as the amount of material published on this subject is voluminous. Instead, an attempt is made to make the reader familiar with what many consider are the key aspects of the technology. 2. UWB: Why another Wireless Protocol? 2.1. -

Ultrawideband Communicationsvan Idea Whose Time Has Still Yet to Come?

Wireless Corner Eva Rajo-Iglesias Dept. Signal Theory and Communications University Carlos III of Madrid Avda Universidad 30, 28911 Leganés (Madrid), Spain Tel.: +34 91 624 8774 E-mail: [email protected] http://www.tsc.uc3m.es/~eva Ultrawideband CommunicationsVAn Idea Whose Time has Still Yet to Come? Philip A. Catherwood1 and William G. Scanlon2 1Nanotechnology and Integrated Bioengineering Centre (NIBEC), Sensors and Connected Health Group, School of Engineering, University of Ulster, Newtownabbey BT37 0QB, U.K. E-mail: [email protected] 2The Institute of Electronics, Communications and Information Technology (ECIT), Queen’s University of Belfast, Belfast BT3 9DT, U.K. E-mail: [email protected] Abstract This paper presents a critical analysis of ultrawideband (UWB) and considers the turbulent journey it has had from the Federal Communications Commission’s bandwidth allocation in 2002 to today. It analyzes the standards, the standoffs, and the stalemate in standardization activities and investigates the past and present research and commercial activities in realizing the UWB dream. In this paper, statistical evidence is presented to depict UWB’s changing fortunes and is utilized as an indicator of future prominence. This paper reviews some of the opinions and remarks from commen- tators and analyzes predictions that were made. Finally, it presents possible ways forward to reignite the high-data-rate UWB standardization pursuit. Keywords: Ultrawideband (UWB); UWB radar; IEEE 802.15 standards; mobile communication; SHF communication; personal area networks (PANs); wireless sensor networks; microwave communication; UWB technology; high-definition television (HDTV) 1. Introduction nthefirst few years after the Federal Communications Digital Object Identifier 10.1109/MAP.2015.2420013 ICommission (FCC) allocated the ultrawideband (UWB) Date of publication: 13 May 2015 bandwidth [1], UWB was considered to be the future wireless 38 IEEE Antennas and Propagation Magazine, Vol. -

Raising the Throughput Bar

Phone: +1 (978) 376-5841 387 Berlin road Fax: + 1 (866) 401-5382 Bolton, MA 01740 Wireless HD Video: Raising the Throughput Bar By Fanny Mlinarsky, President, octoScope, Inc. 1 February 2008 Leapfrogging technologies.......................................................................................... 2 UWB video challenges ............................................................................................... 2 Test results .................................................................................................................. 4 AirHook technology review........................................................................................ 7 Conclusion ................................................................................................................ 10 Appendix A: Test Methodology .............................................................................. 11 +1 (978) 376-5841 1 www.octoscope.com It is difficult to imagine a wireless technology with more innovation and dynamism at work than ultra wideband (UWB), particularly for the delivery of HD video. After a period of relative quiet in the UWB arena, new products are emerging to raise the throughput bar. Recent independent tests put Radiospire (www.radiospire.com) in the lead. Testing by octoScope verified that Radiospire's AirHook technology achieved throughput of 1.6 Gbps – fast enough for uncompressed HD video distribution over distances of 15 feet. Radiospire sponsored the test. This article will first review the promise and technical challenges -

November 2006 Issue of RF Design Magazine

RFID 611RFDEFC.indd 1 11/1/2006 4:37:36 PM ���������������������� ������������������������������������������������������� ������������������������������������������������������������������������ ��������������������������������������������������������������������������������� ������������������������������������������� ������������������������������������� ����������������������������������������������������������������������������� ����������������������������������������������������������������������������� �������������������������������������������������������������������������� ������������������������������������������������� ������������������������������ �������������������������������������������������������������� ��������������������� �������������������� � ��������������������������������������� � ������������������������������������������������������������ �������� ��������� � ����������������������������������������������������������� � ����������������������������������������� ������������������� � ����������������������������������������� � ������������������������������������������������������������������������ ���������������� ������� ������������������������������� � ����������������� �������������������������� � ��������������������������������������������������������������������������� ������������������������������ ������ � ��������� �� ������� �� ��������� ����� ���������������������������������� ����������������������������������������������������� ����� ������������������������������� ����������������������������������������������������