Introduction of P2401 LSI-Package-Board Standard Format

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Japanese Manufacturing Affiliates in Europe and Turkey

06-ORD 70H-002AA 7 Japanese Manufacturing Affiliates in Europe and Turkey - 2005 Survey - September 2006 Japan External Trade Organization (JETRO) Preface The survey on “Japanese manufacturing affiliates in Europe and Turkey” has been conducted 22 times since the first survey in 1983*. The latest survey, carried out from January 2006 to February 2006 targeting 16 countries in Western Europe, 8 countries in Central and Eastern Europe, and Turkey, focused on business trends and future prospects in each country, procurement of materials, production, sales, and management problems, effects of EU environmental regulations, etc. The survey revealed that as of the end of 2005 there were a total of 1,008 Japanese manufacturing affiliates operating in the surveyed region --- 818 in Western Europe, 174 in Central and Eastern Europe, and 16 in Turkey. Of this total, 291 affiliates --- 284 in Western Europe, 6 in Central and Eastern Europe, and 1 in Turkey --- also operate R & D or design centers. Also, the number of Japanese affiliates who operate only R & D or design centers in the surveyed region (no manufacturing operations) totaled 129 affiliates --- 125 in Western Europe and 4 in Central and Eastern Europe. In this survey we put emphasis on the effects of EU environmental regulations on Japanese manufacturing affiliates. We would like to express our great appreciation to the affiliates concerned for their kind cooperation, which have enabled us over the years to constantly improve the survey and report on the results. We hope that the affiliates and those who are interested in business development in Europe and/or Turkey will find this report useful. -

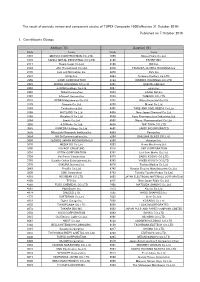

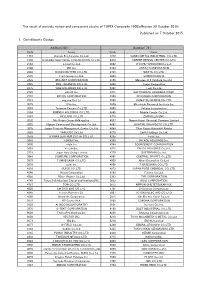

Published on 7 October 2016 1. Constituents Change the Result Of

The result of periodic review and component stocks of TOPIX Composite 1500(effective 31 October 2016) Published on 7 October 2016 1. Constituents Change Addition( 70 ) Deletion( 60 ) Code Issue Code Issue 1810 MATSUI CONSTRUCTION CO.,LTD. 1868 Mitsui Home Co.,Ltd. 1972 SANKO METAL INDUSTRIAL CO.,LTD. 2196 ESCRIT INC. 2117 Nissin Sugar Co.,Ltd. 2198 IKK Inc. 2124 JAC Recruitment Co.,Ltd. 2418 TSUKADA GLOBAL HOLDINGS Inc. 2170 Link and Motivation Inc. 3079 DVx Inc. 2337 Ichigo Inc. 3093 Treasure Factory Co.,LTD. 2359 CORE CORPORATION 3194 KIRINDO HOLDINGS CO.,LTD. 2429 WORLD HOLDINGS CO.,LTD. 3205 DAIDOH LIMITED 2462 J-COM Holdings Co.,Ltd. 3667 enish,inc. 2485 TEAR Corporation 3834 ASAHI Net,Inc. 2492 Infomart Corporation 3946 TOMOKU CO.,LTD. 2915 KENKO Mayonnaise Co.,Ltd. 4221 Okura Industrial Co.,Ltd. 3179 Syuppin Co.,Ltd. 4238 Miraial Co.,Ltd. 3193 Torikizoku co.,ltd. 4331 TAKE AND GIVE. NEEDS Co.,Ltd. 3196 HOTLAND Co.,Ltd. 4406 New Japan Chemical Co.,Ltd. 3199 Watahan & Co.,Ltd. 4538 Fuso Pharmaceutical Industries,Ltd. 3244 Samty Co.,Ltd. 4550 Nissui Pharmaceutical Co.,Ltd. 3250 A.D.Works Co.,Ltd. 4636 T&K TOKA CO.,LTD. 3543 KOMEDA Holdings Co.,Ltd. 4651 SANIX INCORPORATED 3636 Mitsubishi Research Institute,Inc. 4809 Paraca Inc. 3654 HITO-Communications,Inc. 5204 ISHIZUKA GLASS CO.,LTD. 3666 TECNOS JAPAN INCORPORATED 5998 Advanex Inc. 3678 MEDIA DO Co.,Ltd. 6203 Howa Machinery,Ltd. 3688 VOYAGE GROUP,INC. 6319 SNT CORPORATION 3694 OPTiM CORPORATION 6362 Ishii Iron Works Co.,Ltd. 3724 VeriServe Corporation 6373 DAIDO KOGYO CO.,LTD. 3765 GungHo Online Entertainment,Inc. -

Toshiba Case Study RF Module Shrink (Transferjet TM)

Toshiba Case Study RF Module Shrink (TransferJet TM) These slides are an abridgement of two presentations given by Toshiba at the Zuken Innovation World (ZIW) conference held in Japan in 2012 and 2013. Powered by © 2017 Toshiba Electronic Devices & Storage Corporation Project Objectives • TransferJet™ is a standard for high-speed, close proximity wireless transfer technology. 1 • Original design was a simple board with a wire bond package and several peripherals. • Competitive pressures required a significant reduction in size and height of the package. Communication • Customer requests a module which RF matching module is done to handle this technology easily. eMMC µSD DRAM HDMI SSD Battery 8mm CPU TC35420AXLG USB LCD 8mm • Shrink substrate: 8mmX8mm ⇒ 4.5mmX6mm • Shrink height: 1.7mm ⇒ 1.0mm 1. https://toshiba.semicon-storage.com/eu/product/wireless-communication/transferjet.html © 2017 Toshiba Electronic Devices & Storage Corporation 2 Project Requirements • All components could not fit on one PCB substrate • Overall Goals: – Shrink size and thickness of module – Provide RF matching – Provide power stabilization – Minimize noise • Decided to use bare die instead of wire bond package • Needed to do RDL routing on the die • Needed to embed the die – Added extra test pins • Needed to co-design chip, package, board • Needed analysis in context of system • Needed 3D design capabilities • Needed close collaboration with CAE tools. • Selected Zuken’s CR-8000 Design Force and Ansys analysis tools © 2017 Toshiba Electronic Devices & Storage -

Proposal of a Data Processing Guideline for Realizing Automatic Measurement Process with General Geometrical Tolerances and Contactless Laser Scanning

Proposal of a data processing guideline for realizing automatic measurement process with general geometrical tolerances and contactless laser scanning 2018/4/4 Atsuto Soma Hiromasa Suzuki Toshiaki Takahashi Copyright (c)2014, Japan Electronics and Information Technology Industries Association, All rights reserved. 1 Contents • Introduction of the Project • Problem Statements • Proposed Solution – Proposal of New General Geometric Tolerance (GGT) – Data Processing Guidelines for point cloud • Next Steps Copyright (c)2014, Japan Electronics and Information Technology Industries Association, All rights reserved. 2 Contents • Introduction of the Project • Problem Statements • Proposed Solution – Proposal of New General Geometric Tolerance (GGT) – Data Processing Guidelines for Point Cloud • Next Steps Copyright (c)2014, Japan Electronics and Information Technology Industries Association, All rights reserved. 3 Introduction of JEITA What is JEITA? The objective of the Japan Electronics and Information Technology Industries Association (JEITA) is to promote healthy manufacturing, international trade and consumption of electronics products and components in order to contribute to the overall development of the electronics and information technology (IT) industries, and thereby to promote further Japan's economic development and cultural prosperity. JEITA’s Policy and Strategy Board > Number of full members: 279> Number of associate members: 117(as of May 13, 2014) - Director companies and chair/subchair companies - Policy director companies (alphabetical) Fujitsu Limited (chairman Masami Yamamoto) Asahi Glass Co., Ltd. Nichicon Corporation Sharp Corporation Azbil Corporation IBM Japan, Ltd. Hitachi, Ltd. Advantest Corporation Nippon Chemi-Con Corporation Panasonic Corporation Ikegami Tsushinki Co., Ltd. Japan Aviation Electronics Industry, Ltd. SMK Corporation Mitsubishi Electric Corporation Nihon Kohden Corporation Omron Corporation NEC Corporation JRC Nihon Musen Kyocera Corporation Sony Corporation Hitachi Metals, Ltd KOA Corporation Fuji Xerox Co., Ltd. -

Product Safety Guide

Product Safety Guide HL-L2310D / HL-L2335D / HL-B2000D / HL-L2350DW / HL-L2351DW / HL-L2370DN / HL-L2375DW / HL-B2080DW / HL-L2376DW / HL-L2385DW / HL-L2386DW / DCP-L2535D / DCP-B7500D / DCP-L2531DW / DCP-L2535DW / DCP-L2550DW / DCP-B7535DW / HL-L2395DW / MFC-L2710DW / MFC-B7715DW / MFC-L2713DW / MFC-L2715DW / MFC-L2716DW / MFC-L2730DW / MFC-L2750DW / MFC-L2751DW / MFC-L2770DW / MFC-L2771DW Brother Industries, Ltd. 15-1, Naeshiro-cho, Mizuho-ku, Nagoya 467-8561, Japan Read this guide before attempting to operate the product, or before attempting any maintenance. Failure to follow these instructions may result in an increased risk of personal injury or damage to property, including through fire, electrical shock, burns or suffocation. Brother shall not be liable for damage caused where the product owner has failed to follow instructions set out in this guide. How to use this guide: 1. Read the whole guide before using your product and keep it for later reference. 2. Carefully follow the instructions set out in this guide and always ensure that you follow all warnings and instructions marked on the product. 3. If you have concerns about how to use your product after reading this guide, contact Brother customer service or your local Brother dealer. 4. To ensure you understand all of the instructions, study the Symbols and Conventions used in the documentation. NOTE For more advanced instructions, information, and product specifications, see the Online User's Guide at support.brother.com/manuals 1 Symbols and Conventions Used in the Documentation The following symbols and conventions are used throughout the documentation. Follow all warnings and instructions marked on the product. -

Transparency Report 2019

Transparency Report 2019 2018 9 ______年 月 www.kpmg.com jp / / © 2019 KPMG AZSA LLC, a limited liability audit corporation incorporated under the Japanese Certified Public Accountants Law and a member firm of the KPMG network of independent member firms affiliated with KPMG International Cooperative (“KPMG International”), a Swiss entity. All rights reserved. Transparency Report 2019 1 1. Message from the local Senior Partner As a member of the KPMG network, KPMG AZSA LLC shares a common purpose - to Inspire Confidence, Empower Change – with member firms around the globe. Based on this purpose, we aim to establish the reliability of information through auditing and accounting services and support the change of companies and society towards sustainable growth. AZSA Quality 2019 introduces efforts at KPMG AZSA LLC to improve audit quality, the foundation of which is KPMG’s globally consistent audit quality. In this transparency report, we will additionally introduce KPMG’s system for ensuring audit quality. 2. Who we are 2.1 Our business 2.2 Our strategy KPMG AZSA LLC, a member firm of KPMG International, comprises Our firm’s mission is to ensure the reliability of information by approximately 6,000 people in major cities in Japan, providing audit, providing quality audit and accounting services as well as to attestation, and advisory services such as accounting advisory contribute to the realization of a fair society and healthy services, financial advisory services, IT advisory service and other development of our economy by empowering change. In order to advisory services for initial public offerings and the public sector. execute our firm’s mission, we have following vision: We also offer highly specialized professional services that address To be ‘The Clear Choice’ for our clients, people and society. -

SYSTEM CONTROL FAIR 2015 R E P O R T

Showcasing Cutting-Edge Technologies Showcasingfor the Art Cutting-Edge of Manufacturing Technologies for the Art of Manufacturing SYSTEMSYSTEM CONTROLCONTROL FAIRFAIR 20152015 Innovative Manufacturing: Connecting Technology to Tomorrow Innovative Manufacturing: Connecting Technology to Tomorrow Date: December 2 (Wed.) – 4 (Fri), 2015 Opening Hours: 10:00 – 17:00 Venue: Tokyo Big Sight West Hall 1,2,3,4 & Atrium Report SYSTEM CONTROL FAIR Innovative Manufacturing: Connecting Technology to Tomorrow http://scf.jp/en/ Organized by The Japan Electrical Manufacturers’ Association (JEMA) Nippon Electric Control Equipment Industries Association (NECA) Organized by The Japan Electrical Manufacturers’ Association (JEMA) Nippon Electric Control Equipment Industries Association (NECA) SYSTEM CONTROL FAIR 2015 R e p o r t C o n t e n t s Ⅰ.Thanking Remarks ·················································································1 4. A re you planning to participate in the next show in Ⅱ. Result ···············································································································2 2017? 1. Overview Ⅳ. Visitor questionnaire ········································································· 12 2. Exhibitor List 1. What was your reason for visit? 3. Exhibition Floor plan 2. Do you consider your visit was worthwhile? 4. Visitors 3. H ow would you rate the SYSTEM CONTROL 5. Opening ceremony FAIR 2015 and Measurement and Control Show 2015 6. Opening reception TOKYO simultaneous event? 7. Simultaneous event: Conference & Seminar 4. Which category of exhibits did you find interesting? 8. Simultaneous event: Organizer’s Project Ⅴ. Advertising and PR activities ···················································· 13 “The 4th Industrial Revolution– Getting Connected” 1. Preliminary Seminar 9. Simultaneous event: Atrium Stage 2. Press conference and mass media announcements 10. Simultaneous event: Open Network Zone 3. P resentation for embassies, trade promotion 11. Simultaneous event: Overseas Pavilion organizations, and related groups 12. -

IBIS Open Forum Minutes

IBIS Open Forum Minutes Meeting Date: November 13, 2020 Meeting Location: Online Virtual Summit VOTING MEMBERS AND 2020 PARTICIPANTS ANSYS Curtis Clark, Wei-hsing Huang, Marko Marin Shai Sayfan-Altman, Zilwan Mahmod, Baolong Li Usman Saeed, Miyo Kawata* Applied Simulation Technology (Fred Balistreri) Broadcom James Church, Jim Antonellis Cadence Design Systems Zhen Mu, Ambrish Varma, Jared James Kumar Keshavan, Ken Willis, Suomin Cui Takuya Moriya*, Tadaaki Yoshimura* Cisco Systems Stephen Scearce, Hong Wu, Han Gao Dassault Systemes (CST) Stefan Paret Ericsson [Anders Ekholm], Sungjoo Yu, Thomas Ahlstrom Google Zhiping Yang, Shuai Jin, Zhenxue Xu, Hanfeng Wang Songping Wu, Yimajian Yan Huawei Technologies (Hang (Paul) Yan) IBM [Michael Cohen], Greg Edlund Infineon Technologies AG (Christian Sporrer) Instituto de Telecomunicações (Abdelgader Abdalla) Intel Corporation Hsinho Wu, Michael Mirmak, Adrien Auge Fernando Mendoza, Taeyoung Kim, Wendem Beyene Oleg Mikulchenko, Nhan Phan, Ifiok Umoh Subas Bastola, Kinger Cai Keysight Technologies Radek Biernacki, Hee-Soo Lee, Todd Bermensolo Graham Riley, Pegah Alavi, Fangyi Rao Stephen Slater, Toshinori Kageura*, Hiroaki Sasaki* Satoshi Nakamizo*, Toshinobu Sanuki* Marvell Steve Parker, Johann Nittmann, Shaowu Huang Maxim Integrated Joe Engert, Charles Ganal, Dzung Tran, Yan Liang Tushar Pandey Mentor, A Siemens Business Arpad Muranyi, Raj Raghuram, Todd Westerhoff Weston Beal, Kunimoto Mashino*, Kenji Kushima* Micron Technology Randy Wolff*, Justin Butterfield, Larry Smith Vijay Kanagachalam Micron Memory Japan, G.K. Masayuki Honda*, Mikio Sugawara* MST EMC Lab Chulsoon Hwang, Anfeng Huang, Bo Pu, Jiayi He Yin Sun NXP John Burnett ©2020 IBIS Open Forum 1 SerDesDesign.com John Baprawski SiSoft (MathWorks) Mike LaBonte*, Walter Katz, Graham Kus Synopsys Ted Mido*, Andy Tai Teraspeed Labs Bob Ross* Xilinx Ravindra Gali ZTE Corporation (Shunlin Zhu) Zuken Michael Schäder, Kazunari Koga, Kensuke Yoshijima* Takayuki Shiratori* Zuken USA Lance Wang* OTHER PARTICIPANTS IN 2020 A&D Print Engineering Co. -

CADSTAR Express D.I.Y. Tutorial

Express – Version 2018.0 Do-it-Yourself Training Guide Express Do-It-Yourself Guide With Projects for Training Purposes Welcome! Thank you for acquiring CADSTAR Express. This free version provides a number of features used in the full CADSTAR version, only limited by the number of components (max 50) and pins (max 300). Electronic hobbyists, Students and Evaluators use CADSTAR Express for designing Schematics and Printed Circuit Boards (PCB). This guide will assist you in detail on how to make use of CADSTAR’s features to design your next project. • We will start by showing you a hand drawn electronic circuit and transforming it into a professional schematic design. • We will guide you through the process of creating an error-free transfer of data to a PCB board design, and then move to component placement and wire routing. • You will then move to the CAM output process where you will generate the necessary artwork, reports and files needed to get your PCB built by your preferred fabrication vendor. • We will guide you through the process of creating schematic symbols, component and parts for future CADSTAR libraries. Upon completion of this guide, you will be ready to move into higher variations of CADSTAR, offering features and constraints for High Speed signal applications and simulation as well as 3D Electro- Mechanical collaboration. To provide you with additional “how to” information, click on the camera icons for demonstration videos. (internet connection required) The videos are for demonstration purposes only. They are not created to match the exact instructions in the task steps. Please follow the specific steps in the tasks. -

Valor Process Preparation SMT/AOI/Dfx Machine

Valor Process Preparation SMT/AOI/DFx machine Unrestricted © Siemens AG 2019 ❖ Realize innovation. Process Preparation for manufacturing DESIGN TOOL WHAT? PRODUCT NPI . Product data cannot be transferred directly to the line . Valor Process Preparation generates manufacturing execution instructions for automated and manual stations, including : FABRICATION NPI BOM validation HOW? Stencil design ASSEMBLY / TEST Line balancing PROCESS NPI SMT, Test and Inspection programming ASSEMBLY / TEST PLANNING Generation of documentation / work instructions A complete ANALYSIS, MODELING and SIMULATION environment for maximizing the efficiency of the design-to-manufacturing flow Accelerate NPI Increase engineering efficiency by using a single tool for all process engineering tasks Automated Reflow Inspection Manual Assembly Eliminate redundant preparation work with Visual Learning Libraries (machine shapes, rotation etc.) Inspection ICT & Repair Increase efficiency through automation and use of Pick & Final Assembly Place templates (for work instructions, data import parsers, etc.) & Configuration Functional Screen Test / Repair Printer Increase line utilization Maximize off-line preparation Production Packaging to eliminate on-line trial and error delays Preparation A complete ANALYSIS, MODELING and SIMULATION environment for maximizing the efficiency of the design-to-manufacturing flow Preserve manufacturing know-how Consolidate organizational best-practice flows Automated Centralized part libraries incl. rotation neutralization Reflow -

Published on 7 October 2015 1. Constituents Change the Result Of

The result of periodic review and component stocks of TOPIX Composite 1500(effective 30 October 2015) Published on 7 October 2015 1. Constituents Change Addition( 80 ) Deletion( 72 ) Code Issue Code Issue 1712 Daiseki Eco.Solution Co.,Ltd. 1972 SANKO METAL INDUSTRIAL CO.,LTD. 1930 HOKURIKU ELECTRICAL CONSTRUCTION CO.,LTD. 2410 CAREER DESIGN CENTER CO.,LTD. 2183 Linical Co.,Ltd. 2692 ITOCHU-SHOKUHIN Co.,Ltd. 2198 IKK Inc. 2733 ARATA CORPORATION 2266 ROKKO BUTTER CO.,LTD. 2735 WATTS CO.,LTD. 2372 I'rom Group Co.,Ltd. 3004 SHINYEI KAISHA 2428 WELLNET CORPORATION 3159 Maruzen CHI Holdings Co.,Ltd. 2445 SRG TAKAMIYA CO.,LTD. 3204 Toabo Corporation 2475 WDB HOLDINGS CO.,LTD. 3361 Toell Co.,Ltd. 2729 JALUX Inc. 3371 SOFTCREATE HOLDINGS CORP. 2767 FIELDS CORPORATION 3396 FELISSIMO CORPORATION 2931 euglena Co.,Ltd. 3580 KOMATSU SEIREN CO.,LTD. 3079 DVx Inc. 3636 Mitsubishi Research Institute,Inc. 3093 Treasure Factory Co.,LTD. 3639 Voltage Incorporation 3194 KIRINDO HOLDINGS CO.,LTD. 3669 Mobile Create Co.,Ltd. 3197 SKYLARK CO.,LTD 3770 ZAPPALLAS,INC. 3232 Mie Kotsu Group Holdings,Inc. 4007 Nippon Kasei Chemical Company Limited 3252 Nippon Commercial Development Co.,Ltd. 4097 KOATSU GAS KOGYO CO.,LTD. 3276 Japan Property Management Center Co.,Ltd. 4098 Titan Kogyo Kabushiki Kaisha 3385 YAKUODO.Co.,Ltd. 4275 Carlit Holdings Co.,Ltd. 3553 KYOWA LEATHER CLOTH CO.,LTD. 4295 Faith, Inc. 3649 FINDEX Inc. 4326 INTAGE HOLDINGS Inc. 3660 istyle Inc. 4344 SOURCENEXT CORPORATION 3681 V-cube,Inc. 4671 FALCO HOLDINGS Co.,Ltd. 3751 Japan Asia Group Limited 4779 SOFTBRAIN Co.,Ltd. 3844 COMTURE CORPORATION 4801 CENTRAL SPORTS Co.,LTD. -

International Smallcap Separate Account As of August 31, 2017

International SmallCap Separate Account As of August 31, 2017 SCHEDULE OF INVESTMENTS MARKET % OF SECURITY SHARES VALUE ASSETS AUSTRALIA DOWNER EDI LTD 1,551,344 $ 8,796,821 0.45% ALUMINA LTD 5,024,806 $ 8,467,003 0.44% INVESTA OFFICE FUND 2,137,134 $ 7,675,099 0.39% SEVEN GROUP HOLDINGS LTD 687,396 $ 6,967,918 0.36% GPT GROUP 1,189,409 $ 4,728,160 0.24% NORTHERN STAR RESOURCES LTD 1,004,861 $ 4,199,669 0.22% DOWNER EDI LTD 119,088 $ 675,283 0.03% ORORA LTD 234,345 $ 577,639 0.03% TABCORP HOLDINGS LTD 162,980 $ 531,806 0.03% ILUKA RESOURCES LTD 67,000 $ 506,034 0.03% ANSELL LTD 28,800 $ 499,024 0.03% CENTAMIN EGYPT LTD 240,680 $ 470,984 0.02% NIB HOLDINGS LTD 99,941 $ 468,154 0.02% SPARK INFRASTRUCTURE GROUP 214,049 $ 458,851 0.02% IOOF HOLDINGS LTD 48,732 $ 427,260 0.02% WORLEYPARSON LTD 39,819 $ 426,181 0.02% METCASH LTD 191,136 $ 412,387 0.02% DULUXGROUP LTD 77,229 $ 407,957 0.02% PRIMARY HEALTH CARE LTD 148,843 $ 404,926 0.02% CARSALES.COM AU LTD 37,481 $ 404,212 0.02% JB HI-FI LTD 21,914 $ 402,605 0.02% SIMS METAL MANAGEMENT LTD 33,123 $ 393,373 0.02% LINK ADMINISTRATION HOLDINGS 64,343 $ 386,385 0.02% OZ MINERALS LTD 57,242 $ 371,067 0.02% ADELAIDE BRIGHTON LTD 80,460 $ 367,858 0.02% CLEANAWAY WASTE MGMT LTD 303,210 $ 346,026 0.02% MINERAL RESOURCES LTD 28,233 $ 333,958 0.02% PERPETUAL LTD 7,649 $ 333,636 0.02% Not FDIC or NCUA Insured PQ 1041 May Lose Value, Not a Deposit, No Bank or Credit Union Guarantee 08-17 Not Insured by any Federal Government Agency Informational data only.