Flexibilis Ethernet Switch

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Time-Synchronized Data Collection in Smart Grids Through Ipv6 Over

Time-synchronized Data Collection in Smart Grids through IPv6 over BLE Stanley Nwabuona Markus Schuss Simon Mayer Pro2Future GmbH Graz University of Technology Pro2Future GmbH and Graz Graz, Austria Graz, Austria University of Technology [email protected] [email protected] Graz, Austria [email protected] Konrad Diwold Lukas Krammer Alfred Einfalt Siemens Corporate Siemens Corporate Siemens Corporate Technology Technology Technology Vienna, Austria Vienna, Austria Vienna, Austria [email protected] [email protected] [email protected] ABSTRACT INTRODUCTION For the operation of electrical distribution system an increased Due to the progressing integration of distributed energy re- shift towards smart grid operation can be observed. This shift sources (such as domestic photovoltaics) into the distribution provides operators with a high level of reliability and efficiency grid [5], conventional – mostly passive – monitoring and con- when dealing with highly dynamic distribution grids. Techni- trol schemes of power systems are no longer applicable. This cally, this implies that the support for a bidirectional flow of is because these are not designed to handle and manage the data is critical to realizing smart grid operation, culminating in volatile and dynamic behavior stemming from these new active the demand for equipping grid entities (such as sensors) with grid entities. Therefore, advanced controlling and monitoring communication and processing capabilities. Unfortunately, schemes are required for distribution grid operation (i.e., in- the retrofitting of brown-field electric substations in distribu- cluding in Low-Voltage (LV) grids) to avoid system overload tion grids with these capabilities is not straightforward – this which could incur permanent damages. -

Transparent LAN Service Over Cable

Transparent LAN Service over Cable This document describes the Transparent LAN Service (TLS) over Cable feature, which enhances existing Wide Area Network (WAN) support to provide more flexible Managed Access for multiple Internet service provider (ISP) support over a hybrid fiber-coaxial (HFC) cable network. This feature allows service providers to create a Layer 2 tunnel by mapping an upstream service identifier (SID) to an IEEE 802.1Q Virtual Local Area Network (VLAN). Finding Feature Information Your software release may not support all the features documented in this module. For the latest feature information and caveats, see the release notes for your platform and software release. To find information about the features documented in this module, and to see a list of the releases in which each feature is supported, see the Feature Information Table at the end of this document. Use Cisco Feature Navigator to find information about platform support and Cisco software image support. To access Cisco Feature Navigator, go to http://tools.cisco.com/ITDIT/CFN/. An account on http:// www.cisco.com/ is not required. Contents • Hardware Compatibility Matrix for Cisco cBR Series Routers, page 2 • Prerequisites for Transparent LAN Service over Cable, page 2 • Restrictions for Transparent LAN Service over Cable, page 3 • Information About Transparent LAN Service over Cable, page 3 • How to Configure the Transparent LAN Service over Cable, page 6 • Configuration Examples for Transparent LAN Service over Cable, page 8 • Verifying the Transparent LAN Service over Cable Configuration, page 10 • Additional References, page 11 • Feature Information for Transparent LAN Service over Cable, page 12 Cisco Converged Broadband Routers Software Configuration Guide For DOCSIS 1 Transparent LAN Service over Cable Hardware Compatibility Matrix for Cisco cBR Series Routers Hardware Compatibility Matrix for Cisco cBR Series Routers Note The hardware components introduced in a given Cisco IOS-XE Release are supported in all subsequent releases unless otherwise specified. -

Ieee 802.1 for Homenet

IEEE802.org/1 IEEE 802.1 FOR HOMENET March 14, 2013 IEEE 802.1 for Homenet 2 Authors IEEE 802.1 for Homenet 3 IEEE 802.1 Task Groups • Interworking (IWK, Stephen Haddock) • Internetworking among 802 LANs, MANs and other wide area networks • Time Sensitive Networks (TSN, Michael David Johas Teener) • Formerly called Audio Video Bridging (AVB) Task Group • Time-synchronized low latency streaming services through IEEE 802 networks • Data Center Bridging (DCB, Pat Thaler) • Enhancements to existing 802.1 bridge specifications to satisfy the requirements of protocols and applications in the data center, e.g. • Security (Mick Seaman) • Maintenance (Glenn Parsons) IEEE 802.1 for Homenet 4 Basic Principles • MAC addresses are “identifier” addresses, not “location” addresses • This is a major Layer 2 value, not a defect! • Bridge forwarding is based on • Destination MAC • VLAN ID (VID) • Frame filtering for only forwarding to proper outbound ports(s) • Frame is forwarded to every port (except for reception port) within the frame's VLAN if it is not known where to send it • Filter (unnecessary) ports if it is known where to send the frame (e.g. frame is only forwarded towards the destination) • Quality of Service (QoS) is implemented after the forwarding decision based on • Priority • Drop Eligibility • Time IEEE 802.1 for Homenet 5 Data Plane Today • 802.1Q today is 802.Q-2011 (Revision 2013 is ongoing) • Note that if the year is not given in the name of the standard, then it refers to the latest revision, e.g. today 802.1Q = 802.1Q-2011 and 802.1D -

Implementing an IEEE 1588 V2 on I.MX RT Using Ptpd, Freertos, and Lwip TCP/IP Stack

NXP Semiconductors Document Number: AN12149 Application Note Rev. 1 , 09/2018 Implementing an IEEE 1588 V2 on i.MX RT Using PTPd, FreeRTOS, and lwIP TCP/IP stack 1. Introduction Contents This application note describes the implementation of 1. Introduction .........................................................................1 the IEEE 1588 V2 Precision Time Protocol (PTP) on 2. IEEE 1588 basic overview ..................................................2 2.1. Synchronization principle ........................................ 3 the i.MX RT MCUs running FreeRTOS OS. The IEEE 2.2. Timestamping ........................................................... 5 1588 standard provides accurate clock synchronization 3. IEEE 1588 functions on i.MX RT .......................................6 for distributed control nodes in industrial automation 3.1. Adjustable timer module .......................................... 6 3.2. Transmit timestamping ............................................. 8 applications. 3.3. Receive timestamping .............................................. 8 3.4. Time synchronization ............................................... 8 The implementation runs on the i.MX RT10xx 3.5. Input capture and output compare block .................. 8 Evaluation Kit (EVK) board with i.MX RT10xx MCUs. 4. IEEE 1588 implementation for i.MX RT ............................9 The demo software is based on the NXP MCUXpresso 4.1. Hardware components .............................................. 9 4.2. Software components ............................................ -

Introduction to Spanning Tree Protocol by George Thomas, Contemporary Controls

Volume6•Issue5 SEPTEMBER–OCTOBER 2005 © 2005 Contemporary Control Systems, Inc. Introduction to Spanning Tree Protocol By George Thomas, Contemporary Controls Introduction powered and its memory cleared (Bridge 2 will be added later). In an industrial automation application that relies heavily Station 1 sends a message to on the health of the Ethernet network that attaches all the station 11 followed by Station 2 controllers and computers together, a concern exists about sending a message to Station 11. what would happen if the network fails? Since cable failure is These messages will traverse the the most likely mishap, cable redundancy is suggested by bridge from one LAN to the configuring the network in either a ring or by carrying parallel other. This process is called branches. If one of the segments is lost, then communication “relaying” or “forwarding.” The will continue down a parallel path or around the unbroken database in the bridge will note portion of the ring. The problem with these approaches is the source addresses of Stations that Ethernet supports neither of these topologies without 1 and 2 as arriving on Port A. This special equipment. However, this issue is addressed in an process is called “learning.” When IEEE standard numbered 802.1D that covers bridges, and in Station 11 responds to either this standard the concept of the Spanning Tree Protocol Station 1 or 2, the database will (STP) is introduced. note that Station 11 is on Port B. IEEE 802.1D If Station 1 sends a message to Figure 1. The addition of Station 2, the bridge will do ANSI/IEEE Std 802.1D, 1998 edition addresses the Bridge 2 creates a loop. -

Layer 2 Virtual Private Networks CM-SP-L2VPN-I11-130808

Data-Over-Cable Service Interface Specifications Business Services over DOCSIS® Layer 2 Virtual Private Networks CM-SP-L2VPN-I11-130808 ISSUED Notice This DOCSIS specification is the result of a cooperative effort undertaken at the direction of Cable Television Laboratories, Inc. for the benefit of the cable industry and its customers. This document may contain references to other documents not owned or controlled by CableLabs®. Use and understanding of this document may require access to such other documents. Designing, manufacturing, distributing, using, selling, or servicing products, or providing services, based on this document may require intellectual property licenses from third parties for technology referenced in this document. Neither CableLabs nor any member company is responsible to any party for any liability of any nature whatsoever resulting from or arising out of use or reliance upon this document, or any document referenced herein. This document is furnished on an "AS IS" basis and neither CableLabs nor its members provides any representation or warranty, express or implied, regarding the accuracy, completeness, noninfringement, or fitness for a particular purpose of this document, or any document referenced herein. Cable Television Laboratories, Inc., 2006-2013 CM-SP-L2VPN-I11-130808 Data-Over-Cable Service Interface Specifications DISCLAIMER This document is published by Cable Television Laboratories, Inc. ("CableLabs®"). CableLabs reserves the right to revise this document for any reason including, but not limited to, changes in laws, regulations, or standards promulgated by various agencies; technological advances; or changes in equipment design, manufacturing techniques, or operating procedures described, or referred to, herein. CableLabs makes no representation or warranty, express or implied, with respect to the completeness, accuracy, or utility of the document or any information or opinion contained in the report. -

7-Port Gigabit Ethernet Switch with Audio Video Bridging and Two RGMII/MII/RMII Interfaces

KSZ9567R 7-Port Gigabit Ethernet Switch with Audio Video Bridging and Two RGMII/MII/RMII Interfaces Highlights • Five Integrated PHY Ports - 1000BASE-T/100BASE-TX/10BASE-Te IEEE 802.3 • Non-blocking wire-speed Ethernet switching fabric - Fast Link-up option significantly reduces link-up time • Full-featured forwarding and filtering control, includ- - Auto-negotiation and Auto-MDI/MDI-X support ing Access Control List (ACL) filtering - On-chip termination resistors and internal biasing for • Full VLAN and QoS support differential pairs to reduce power • Five ports with integrated 10/100/1000BASE-T PHY - LinkMD® cable diagnostic capabilities for determining transceivers cable opens, shorts, and length • Two ports with 10/100/1000 Ethernet MACs and con- • Advanced Switch Capabilities figurable RGMII/MII/RMII interfaces - IEEE 802.1Q VLAN support for 128 active VLAN • IEEE 1588v2 Precision Time Protocol (PTP) support groups and the full range of 4096 VLAN IDs - IEEE 802.1p/Q tag insertion/removal on per port basis • IEEE 802.1AS/Qav Audio Video Bridging (AVB) - VLAN ID on per port or VLAN basis • IEEE 802.1X access control support - IEEE 802.3x full-duplex flow control and half-duplex • EtherGreen™ power management features, back pressure collision control including low power standby - IEEE 802.1X access control 2 • Flexible management interface options: SPI, I C, (Port-based and MAC address based) MIIM, and in-band management via any port - IGMP v1/v2/v3 snooping for multicast packet filtering • Industrial temperature range support - IPv6 -

Analysis of Qos in Software Defined Wireless Network with Spanning Tree Protocol

I. J. Computer Network and Information Security, 2017, 6, 61-68 Published Online June 2017 in MECS (http://www.mecs-press.org/) DOI: 10.5815/ijcnis.2017.06.07 Analysis of QoS in Software Defined Wireless Network with Spanning Tree Protocol Rafid Mustafiz, Abu Sayem Mohammad Delowar Hossain, Nazrul Islam+, Mohammad Motiur Rahman Department of Computer Science and Engineering +Department of Information and Communication Technology Mawlana Bhashani Science and Technology University, Santosh, Tangail-1902, Bangladesh E-mail: [email protected], [email protected], [email protected], [email protected] Abstract—Software Defined Network (SDN) is more technique. The data controlling actions are controlled by dynamic, manageable, adaptive and programmable a software or hardware based centralized controller and network architecture. This architecture separates the data forwarding task has performed by a hardware core control plane from the forwarding plane that enables the device [3]. This enables the control plane to be directly network to become directly programmable. The programmable which makes it suitable in the field of programmable features of SDN technology has research. Data plane functionality contains features such dramatically improved network efficiency and simplify as quality of service (QoS) [4]. The overall performance the network configuration and resource management. of a network topology depends mostly on the parameters SDN supports Open-Flow technology as forwarding of QoS. The present goal of SDN is to design a network function and centralized control successfully. Wireless that is capable the maximum improvement of QoS environment has recently added to the SDN infrastructure parameters. SDN supports many new types of that has rapidly emerged with Open-Flow protocol. -

V1.1.1 (2014-09)

Final draft ETSI ES 203 385 V1.1.1 (2014-09) ETSI STANDARD CABLE; DOCSIS® Layer 2 Virtual Private Networking 2 Final draft ETSI ES 203 385 V1.1.1 (2014-09) Reference DES/CABLE-00008 Keywords access, broadband, cable, data, IP, IPcable, L2VPN, modem ETSI 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88 Important notice The present document can be downloaded from: http://www.etsi.org The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorization of ETSI. In case of any existing or perceived difference in contents between such versions and/or in print, the only prevailing document is the print of the Portable Document Format (PDF) version kept on a specific network drive within ETSI Secretariat. Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at http://portal.etsi.org/tb/status/status.asp If you find errors in the present document, please send your comment to one of the following services: http://portal.etsi.org/chaircor/ETSI_support.asp Copyright Notification No part may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm except as authorized by written permission of ETSI. -

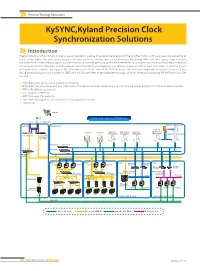

Kysync,Kyland Precision Clock Synchronization Solutions

Precise Timing Solutions KySYNC,Kyland Precision Clock Synchronization Solutions Introduction Precision clock synchronization solutions are using external precise time reference to establish the synchronization with local clocks by delivering all kinds of time signal. The time source provides the time reference, and the time server distributes the timing. While the time source is not available, the time server’s time keeping ability will be critical to assure the precision of the time reference. So in a precision clock synchronization network, the precision of time reference, time distribution and time keeping are hook-ups and all plays important role in each time node. In order to ensure all legacy devices which only support IRIG-B format could still be synced, the PTP (Precision Time Protocol) signal will need to be converted into IRIG-B format through clock conversion. IEEE 1588 will also be need to be distributed through all kinds of network including PRP/HSR and also SDH network. Kyland provides turnkey timing solution including: High-precision time server and IEEE 1588 industrial Ethernet switches supporting IEEE 1588 in both power profile (C37.238) and telecom profile PTP to IRIG-B time conversion IEEE 1588 over PRP/HSR IEEE 1588 over SDH network TMS (Time Management System) & Service Management System Time tester Satellite KySYNC, Intelligent Gateway, PRP/HSR Solution E1/T1 GPS Antenna Remote Control Center KySYNC Station Level Protection Engineering Server A Sever B Operation Maintenance Operation Workstation Workstation Workstation -

Network Virtualization Using Shortest Path Bridging (802.1Aq) and IP/SPB

avaya.com Network Virtualization using Shortest Path Bridging and IP/SPB Abstract This White Paper discusses the benefits and applicability of the IEEE 802.1aq Shortest Path Bridging (SPB) protocol which is augmented with sophisticated Layer 3 routing capabilities. The use of SPB and the value to solve virtualization of today’s network connectivity in the enterprise campus as well as the data center are covered. This document is intended for any technically savvy network manager as well as network architect who are faced with: • Reducing time to service requirements • Less tolerance for network down time • Network Virtualization requirements for Layer 2 (VLAN-extensions) and Layer 3 (VRF-extensions) • Server Virtualization needs in data center deployments requiring a large set of Layer 2 connections (VLANs) • Traffic separation requirements in campus deployments for security purposes as well as robustness considerations (i.e. contractors for maintenance reasons needing access to their equipment or guest access needs) • Multi-tenant applications such as airports, governments or any other network with multiple discrete (legal) entities that require traffic separation WHITE PAPER 1 avaya.com Table of Contents 1. Introduction ........................................................................................................................ 3 2. Benefits of SPB ................................................................................................................... 4 2.1 Network Service Enablement ............................................................................................................ -

4Th Slide Set Computer Networks

Devices of the Data Link Layer Impact on the Collision Domain Addressing in the Data Link Layer 4th Slide Set Computer Networks Prof. Dr. Christian Baun Frankfurt University of Applied Sciences (1971–2014: Fachhochschule Frankfurt am Main) Faculty of Computer Science and Engineering [email protected] Prof. Dr. Christian Baun – 4th Slide Set Computer Networks – Frankfurt University of Applied Sciences – WS1920 1/28 Devices of the Data Link Layer Impact on the Collision Domain Addressing in the Data Link Layer Learning Objectives of this Slide Set Data Link Layer (part 1) Devices of the Data Link Layer Learning Bridges Loops on the Data Link Layer Spanning Tree Protocol Impact on the collision domain Addressing in the Data Link Layer Format of MAC addresses Uniqueness of MAC addresses Security aspects of MAC addresses Prof. Dr. Christian Baun – 4th Slide Set Computer Networks – Frankfurt University of Applied Sciences – WS1920 2/28 Devices of the Data Link Layer Impact on the Collision Domain Addressing in the Data Link Layer Data Link Layer Functions of the Data Link Layer Sender: Pack packets of the Network Layer into frames Receiver: Identify the frames in the bit stream from the Physical Layer Ensure correct transmission of the frames inside a physical network from one network device to another one via error detection with checksums Provide physical addresses (MAC addresses) Control access to the transmission medium Devices: Bridge, Layer-2-Switch (Multiport-Bridge), Modem Protocols: Ethernet, Token Ring, WLAN, Bluetooth,