The Future Is Not What It Used to Be

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The State of Digital Computer Technology in Europe, 1961

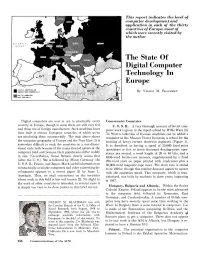

This report indicates the level of computer development and application in each of the thirty countries of Europe, most of which were recently visited by the author The State Of Digital Computer Technology In Europe By NELSON M. BLACHMAN Digital computers are now in use in practically every Communist Countries country in Europe, though in some there are still very few U. S. S.R. A very thorough account of Soviet com- and these are of foreign manufacture. Such machines have puter work is given in the report edited by Willis Ware [3]. been built in sixteen European countries, of which seven To Ware's collection of Russian machines can be added a are producing them commercially. The map above shows computer at the Moscow Power Institute, a school for the the computer geography of Europe and the Near East. It is training of heavy-current electrical engineers (Figure 1). somewhat difficult to rank the countries on a one-dimen- It is described as having a speed of 25,000 fixed-point sional scale both because of the many-faceted nature of the operations or five to seven thousand floating-point oper- computer field and because their populations differ widely ations per second, a word length of 20 or 40 bits, and a in size. Nevertheh~ss, Great Britain clearly comes first 4096-word ferrite-core memory, supplemented by a fixed (after the U. S.). She is followed by (West) Germany, the 256-word store on paper printed with condensers plus a U. S. S. R., France, and Japan. Much useful information on 50,000-word magnetic-tape store. -

Open PDF in New Window

BEST AVAILABLE COPY i The pur'pose of this DIGITAL COMPUTER Itop*"°a""-'"""neesietter' YNEWSLETTER . W OFFICf OF NIVAM RUSEARCMI • MATNEMWTICAL SCIENCES DIVISION Vol. 9, No. 2 Editors: Gordon D. Goldstein April 1957 Albrecht J. Neumann TABLE OF CONTENTS It o Page No. W- COMPUTERS. U. S. A. "1.Air Force Armament Center, ARDC, Eglin AFB, Florida 1 2. Air Force Cambridge Research Center, Bedford, Mass. 1 3. Autonetics, RECOMP, Downey, Calif. 2 4. Corps of Engineers, U. S. Army 2 5. IBM 709. New York, New York 3 6. Lincoln Laboratory TX-2, M.I.T., Lexington, Mass. 4 7. Litton Industries 20 and 40 DDA, Beverly Hills, Calif. 5 8. Naval Air Test Centcr, Naval Air Station, Patuxent River, Maryland 5 9. National Cash Register Co. NC 304, Dayton, Ohio 6 10. Naval Air Missile Test Center, RAYDAC, Point Mugu, Calif. 7 11. New York Naval Shipyard, Brooklyn, New York 7 12. Philco, TRANSAC. Philadelphia, Penna. 7 13. Western Reserve Univ., Cleveland, Ohio 8 COMPUTING CENTERS I. Univ. of California, Radiation Lab., Livermore, Calif. 9 2. Univ. of California, SWAC, Los Angeles, Calif. 10 3. Electronic Associates, Inc., Princeton Computation Center, Princeton, New Jersey 10 4. Franklin Institute Laboratories, Computing Center, Philadelphia, Penna. 11 5. George Washington Univ., Logistics Research Project, Washington, D. C. 11 6. M.I.T., WHIRLWIND I, Cambridge, Mass. 12 7. National Bureau of Standards, Applied Mathematics Div., Washington, D.C. 12 8. Naval Proving Ground, Naval Ordnance Computation Center, Dahlgren, Virgin-.a 12 9. Ramo Wooldridge Corp., Digital Computing Center, Los Angeles, Calif. -

Niels Ivar Bech

Niels Ivar Bech Born 1920 Lemvig, Denmark; died 1975; originator of Danish computer development. Niels Ivar Bech was one of Europe's most creative leaders in the field of electronic digital computers.1 He originated Danish computer development under the auspices of the Danish Academy of Technical Sciences and was first managing director of its subsidiary, Regnecentralen, which was Denmark's (and one of Europe's) first independent designer and builder of electronic computers. Bech was born in 1920 in Lemvig, a small town in the northwestern corner of Jutland, Denmark; his schooling ended with his graduation from Gentofte High School (Statsskole) in 1940. Because he had no further formal education, he was not held in as high esteem as he deserved by some less gifted people who had degrees or were university professors. During the war years, Bech was a teacher. When Denmark was occupied by the Nazis, he became a runner for the distribution of illegal underground newspapers, and on occasion served on the crews of the small boats that perilously smuggled Danish Jews across the Kattegat to Sweden. After the war, from 1949 to 1957, he worked as a calculator in the Actuarial Department of the Copenhagen Telephone Company (Kobenhavns Telefon Aktieselskab, KTA). The Danish Academy of Technical Sciences established a committee on electronic computing in 1947, and in 1952 the academy obtained free access to the complete design of the computer BESK (Binar Electronisk Sekevens Kalkylator) being built in Stockholm by the Swedish Mathematical Center (Matematikmaskinnamndens Arbetsgrupp). In 1953 the Danish academy founded a nonprofit computer subsidiary, Regnecentralen. -

Norwegian Computer Tecnology Founding a New Industry

Norwegian Computer Tecnology Founding a new Industry Yngvar Lundh Research Engineer rered from NDRE Norwegian Defence Research Establisment Early history of development a personal account • 1950s: – Electronic brains ”Replacing so many matemacians” – A few isolated goups in Scandinavia BESK, DASK, NUSSE – Similar groups in the US and elsewhere Probably many military applicaons. • 1960s: – Group of young research engineers at NDRE – Spawning three major businesses Three growing businesses • Norsk Data grew fast to become ”The Flagship of Norwegian Industry” – unl the crisis in the late 1980s • Computer division of Kongsberg Våpenfabrikk specialised systems • Consulng company AS Informasjonskontroll Informasjonskontroll Professional knowledge,advice and assistance Study ”Siffer Frekvens‐ systemet” could In my thesis work I invesgated add, mulply, divide a special digital technique Vacuum tube digital logic Reliability • Vacuum tubes unreliable • Much litterature about that • Solid state? Transistors and magnec devices were studied and a few experimental transistorized machines were built in the late 1950s in USA Fellowship at MIT • In 1958 – 59 I was guest • I could use it all by at MIT and worked on myself the TX‐0 computer • Studied circuits • Transistors • Magnec core memory • CRT screen Paper tape, CRT, Flexowriter • Programming in binary Exploing Man machine • Some fellow researchers communicaons in the TX‐0 lab developed useful programming aids: • Tom Stockham: ”Insight” • Larry Roberts: ”Text on the screen” • Yngvar Lundh: Input via -

Något Om De Första Svenska Datamaskinerna

Något om de första svenska datamaskinerna Av Jörgen Lund De datamaskiner - eller som vi säger idag, datorer - som fanns tillgängliga i början av 1950-talet var samtliga laboratoriebyggda. De var till yttermera visso inte datorer i modern bemärkelse utan snarare automatiska beräkningsmaskiner. Det skulle dröja några år innan de första egentliga ”databehandlingsmaskinerna”, dvs vad tyskarna kal lade ”Datenverarbeitungsanlagen”, kom på marknaden; med andra ord, datorer avsedda för det område som kallas administrativ databe handling (ADB). I och med lanseringen av de första ADB-datorerna i slutet av 1950-talet i Sverige inleddes en ny epok med en mer allmän utbredning och användning av det relativt nya hjälpmedlet, datorn. I mitten av 50-talet stod det klart att datorn var ett hjälpmedel att räkna med i framtiden - i dubbel bemärkelse. Sverige skulle bli något av ett föregångsland i kraft av skickliga och begåvade tekniker och matematiker. Visserligen hade man innan dess varit i det stora landet i väst, USA, och lärt sig en hel del om den nya teknologin; visserligen hade amerikanska maskiner tjänat som förebild för de första svenska datorerna, men de konstruerades och byggdes icke förty av svenska tekniker och matematiker. ”Nattvandrare Varför inte inleda med ett citat ur Dagens Nyheter 1 februari 1953: kan konstatera ”Nattvandrare kan konstatera att det alltid lyser i nämndens fönster att.. ut mot Drottninggatan. Där arbetar BARK, Sveriges första matema tikmaskin, ambitiöst dygnet runt och tjänar in vackra slantar ät svenska staten. När den blev färdig 1950 hade den kostat 600000 kronor. Nu ger den en avkastning pä i runt tal 100000 om äret och kan alltsä sägas vara en ovanligt lyckad kapitalplacering. -

Downloading from Naur's Website: 19

1 2017.04.16 Accepted for publication in Nuncius Hamburgensis, Band 20. Preprint of invited paper for Gudrun Wolfschmidt's book: Vom Abakus zum Computer - Begleitbuch zur Ausstellung "Geschichte der Rechentechnik", 2015-2019 GIER: A Danish computer from 1961 with a role in the modern revolution of astronomy By Erik Høg, lektor emeritus, Niels Bohr Institute, Copenhagen Abstract: A Danish computer, GIER, from 1961 played a vital role in the development of a new method for astrometric measurement. This method, photon counting astrometry, ultimately led to two satellites with a significant role in the modern revolution of astronomy. A GIER was installed at the Hamburg Observatory in 1964 where it was used to implement the entirely new method for the meas- urement of stellar positions by means of a meridian circle, then the fundamental instrument of as- trometry. An expedition to Perth in Western Australia with the instrument and the computer was a suc- cess. This method was also implemented in space in the first ever astrometric satellite Hipparcos launched by ESA in 1989. The Hipparcos results published in 1997 revolutionized astrometry with an impact in all branches of astronomy from the solar system and stellar structure to cosmic distances and the dynamics of the Milky Way. In turn, the results paved the way for a successor, the one million times more powerful Gaia astrometry satellite launched by ESA in 2013. Preparations for a Gaia suc- cessor in twenty years are making progress. Zusammenfassung: Eine elektronische Rechenmaschine, GIER, von 1961 aus Dänischer Herkunft spielte eine vitale Rolle bei der Entwiklung einer neuen astrometrischen Messmethode. -

Early Nordic Compilers and Autocodes Peter Sestoft

Early Nordic Compilers and Autocodes Peter Sestoft To cite this version: Peter Sestoft. Early Nordic Compilers and Autocodes. 4th History of Nordic Computing (HiNC4), Aug 2014, Copenhagen, Denmark. pp.350-366, 10.1007/978-3-319-17145-6_36. hal-01301428 HAL Id: hal-01301428 https://hal.inria.fr/hal-01301428 Submitted on 12 Apr 2016 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Distributed under a Creative Commons Attribution| 4.0 International License Early Nordic Compilers and Autocodes Version 2.1.0 of 2014-11-17 Peter Sestoft IT University of Copenhagen Rued Langgaards Vej 7, DK-2300 Copenhagen S, Denmark [email protected] Abstract. The early development of compilers for high-level program- ming languages, and of so-called autocoding systems, is well documented at the international level but not as regards the Nordic countries. The goal of this paper is to provide a survey of compiler and autocode development in the Nordic countries in the early years, roughly 1953 to 1965, and to relate it to international developments. We also touch on some of the historical societal context. 1 Introduction A compiler translates a high-level, programmer-friendly programming language into the machine code that computer hardware can execute. -

The Development of University Computing in Sweden 1965–1985

The Development of University Computing in Sweden 1965–1985 Ingemar Dahlstrand Former affiliation of author: Manager of Lund University Computing Center 1968–1980 Abstract. In 1965-70 the government agency, Statskontoret, set up five univer- sity computing centers, as service bureaux financed by grants earmarked for computer use. The centers were well equipped and staffed and caused a surge in computer use. When the yearly flow of grant money stagnated at 25 million Swedish crowns, the centers had to find external income to survive and acquire time-sharing. But the charging system led to the computers not being fully used. The computer scientists lacked equipment for laboratory use. The centers were decentralized and the earmarking abolished. Eventually they got new tasks like running computers owned by the departments, and serving the university administration. Keywords: University, computing, center, earmarked grants. 1 University Computer Resources before 1965 In 1964, the Swedish government decided to organize computer resources for the uni- versities. At that time, the universities’ access to computing power varied a great deal and was insufficient in most places. Lund was best equipped with SMIL, a well- developed BESK copy of its own. Uppsala and Stockholm had access to state-owned BESK and Facit that were heavily loaded, however. Now those three machines were becoming obsolete. In Gothenburg Alwac III E minis were available, and a Datasaab D21, the latter however without supporting service, and the two universities there actually had to rely on Facit time donated by the service bureau Industridata for their computing science education. 2 The Proposed Organization A scheme was set up which included fresh money earmarked for computer time. -

Gene Amdahl - a Computer Pioneer Carl-Johan Ivarsson

Swedish American Genealogist Volume 33 | Number 3 Article 6 9-1-2013 Gene Amdahl - a computer pioneer Carl-Johan Ivarsson Elisabeth Thorsell Christopher Olsson Follow this and additional works at: https://digitalcommons.augustana.edu/swensonsag Part of the Genealogy Commons, and the Scandinavian Studies Commons Recommended Citation Ivarsson, Carl-Johan; Thorsell, Elisabeth; and Olsson, Christopher (2013) "Gene Amdahl - a computer pioneer," Swedish American Genealogist: Vol. 33 : No. 3 , Article 6. Available at: https://digitalcommons.augustana.edu/swensonsag/vol33/iss3/6 This Article is brought to you for free and open access by Augustana Digital Commons. It has been accepted for inclusion in Swedish American Genealogist by an authorized editor of Augustana Digital Commons. For more information, please contact [email protected]. Gene Amdahl - a Swedish-Norwegian computer pioneer Computers are now a common daily tool, but they also have their history BY CARL-JOHAN IVARSSON Translation by Elisabeth Thorsell and Christopher Olsson. In the 3rd edition of the Swedish other early pioneers are mentioned South Dakota encyclopedia Bra Backer's Lexikon, as well as some known early com- Gene Myron Amdahl was born 1922 volume 5 (Coe-Dick) from 1984, we puters in Sweden with names like Nov. 16 close to Flandreau, Moody find the word "Dator" (computer). It BARK, BESK, and SMIL. Apple is Co., South Dakota. The name sounds says dator or datamaskin is "a ma- mentioned, but not Microsoft. We do Norwegian, and three of his grand- chine that without human inter- not find the business superstars of parents came from Norway. ference can perform large com- our time, people like Steve Jobs and His paternal grandfather Ole Ol- putations of a great number of Bill Gates. -

Central Computer for Aircraft Saab 37, Viggen

1 Central Computer for aircraft Saab 37, Viggen Bengt Jiewertz Formerly of Datasaab and Ericsson AB Abstract: In the beginning of the 1960s it was decided that the multipurpose attack/fighter Saab 37 Viggen should be designed as a single seat aircraft. A central computer and a head-up display made it possible to dispense with the need for a human navigator. The computer was the central computing and integrating unit for all electronic equipment to support the pilot. This computer, CK37 used in the Saab AJ37, was the first airborne computer in the world to use integrated circuits (first generation ICs). Almost 200 computers were delivered 1970 -1978. The function was reliable and the computers were still in operation, with upgrades, at the early beginning of 2000`s. Key words: Aircraft computers, CK37 1. Background In the early twentieth century there were twelve Swedish companies involved in the manufacture of aircraft. They had, however, no support from the Swedish Defence Department. Later, in 1932, Parliament decided that Sweden should be self-sufficient in the supply of military aircraft. The company Saab (Svenska Aeroplan AktieBolaget) was established in 1937 and was contracted by the Swedish Air Force to deliver military aircraft. Three types of propeller aircraft were successively delivered. The international tension grew after the Second World War and the Saab technical ability and capacity was used for new advanced developments. From 1950 four new subsonic jet aircrafts were delivered. The most famous one was the fighter Saab 29 “Tunnan”. In total 661 Saab 29 were delivered in the period 1950-1956 and made the Swedish Air Force the fourth largest in the world. -

The ENIAC Integrations

10 The ENIAC integrations The role of the enormous weather factory envisaged by Richardson (1922) with its thousands of computers will . be taken over by a com- pletely automatic electronic computing machine. (Charney, 1949) It is without question that Richardson’s attempt to predict the weather by numerical means, while visionary and courageous, was premature. In his review of WPNP, Exner (1923) expressed the view that Richardson’s method was unlikely to lead to progress in weather forecasting and even recommended that he should write a book on theoretical meteorology that was free from the aim of a direct application to prediction. This negative response was echoed by several other reviewers. Later, the renowned meteorologist Bernhard Haurwitz wrote in his textbook Dynamic Meteorology that efforts to compute weather changes by direct application of the equations was not promising, adding that . a computation of the future weather by dynamical methods will be possible only when it is known more definitely which factors have to be taken into account under given conditions and which may be neglected (Haurwitz, 1941, p. 180). Haurwitz understood that a simplification of the mathematical formulation of the forecasting problem was required but he was not in a position to propose any spe- cific solution. In fact, there were several obstacles preventing the fulfilment of Richardson’s dream, and progress was required on four separate fronts before it could be realized. Firstly, in order to develop a simplified system suitable for numerical predic- tion, a better understanding of atmospheric dynamics, and especially of the wave motions in the upper atmosphere, was required. -

Computing and Operational Command in the Swedish Armed Forces, 1966-1989

Precursors of the IT Nation: Computer Use and Control in Swedish Society, 1955–1985 Isabelle Dussauge1, Johan Gribbe2, Arne Kaijser2, Per Lundin2, Julia Peralta2, Gustav Sjöblom3, and Björn Thodenius4 1 Dept. of Thematic Studies – Technology and Social Change, Linköping University 581 83 Linköping, Sweden [email protected] 2 Div. of History of Science and Technology, KTH 100 44 Stockholm, Sweden {johan.gribbe, arne.kaijser, per.lundin, julia.peralta}@abe.kth.se 3 Div. of Technology and Society, Chalmers University of Technology 412 96 Göteborg, Sweden [email protected] 4 Dept. of Management and Organization, Stockholm School of Economics 113 83 Stockholm, Sweden [email protected] Abstract. This paper is a presentation of a research project that aims at writing the history of computing in Sweden in the mainframe age from a user perspective. Rather than beginning with the history of hardware, this project takes as its point of departure the way in which actors in different sectors of society used computer technology in order to achieve a higher degree of control over crucial processes, whether through electronic data processing systems, process control or technical/scientific computation. Keywords: Control, historiography, history of computing, IT-history, Sweden, users 1 Introduction This paper is a presentation of the research project “Precursors of the IT Nation: Computer Use and Control in Swedish Society, 1955–1985.”1 The aim is to draw upon the experience and sources accumulated in the project “From Computing Machines to IT” and to write the history of computing in Sweden in the mainframe age from a user perspective [1, 2].