TPS23861 IEEE 802.3At Quad Port Power-Over-Ethernet PSE

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Disability Classification System

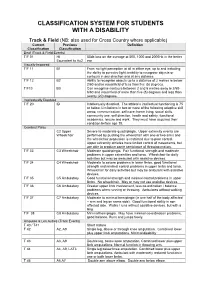

CLASSIFICATION SYSTEM FOR STUDENTS WITH A DISABILITY Track & Field (NB: also used for Cross Country where applicable) Current Previous Definition Classification Classification Deaf (Track & Field Events) T/F 01 HI 55db loss on the average at 500, 1000 and 2000Hz in the better Equivalent to Au2 ear Visually Impaired T/F 11 B1 From no light perception at all in either eye, up to and including the ability to perceive light; inability to recognise objects or contours in any direction and at any distance. T/F 12 B2 Ability to recognise objects up to a distance of 2 metres ie below 2/60 and/or visual field of less than five (5) degrees. T/F13 B3 Can recognise contours between 2 and 6 metres away ie 2/60- 6/60 and visual field of more than five (5) degrees and less than twenty (20) degrees. Intellectually Disabled T/F 20 ID Intellectually disabled. The athlete’s intellectual functioning is 75 or below. Limitations in two or more of the following adaptive skill areas; communication, self-care; home living, social skills, community use, self direction, health and safety, functional academics, leisure and work. They must have acquired their condition before age 18. Cerebral Palsy C2 Upper Severe to moderate quadriplegia. Upper extremity events are Wheelchair performed by pushing the wheelchair with one or two arms and the wheelchair propulsion is restricted due to poor control. Upper extremity athletes have limited control of movements, but are able to produce some semblance of throwing motion. T/F 33 C3 Wheelchair Moderate quadriplegia. Fair functional strength and moderate problems in upper extremities and torso. -

University of Wales Archive (GB 0210 UNIVWALES)

Llyfrgell Genedlaethol Cymru = The National Library of Wales Cymorth chwilio | Finding Aid - University of Wales Archive (GB 0210 UNIVWALES) Cynhyrchir gan Access to Memory (AtoM) 2.3.0 Generated by Access to Memory (AtoM) 2.3.0 Argraffwyd: Mai 04, 2017 Printed: May 04, 2017 Wrth lunio'r disgrifiad hwn dilynwyd canllawiau ANW a seiliwyd ar ISAD(G) Ail Argraffiad; rheolau AACR2; ac LCSH This description follows NLW guidelines based on ISAD(G) Second Edition; AACR2; and LCSH. https://archifau.llyfrgell.cymru/index.php/university-of-wales-archive archives.library .wales/index.php/university-of-wales-archive Llyfrgell Genedlaethol Cymru = The National Library of Wales Allt Penglais Aberystwyth Ceredigion United Kingdom SY23 3BU 01970 632 800 01970 615 709 [email protected] www.llgc.org.uk University of Wales Archive Tabl cynnwys | Table of contents Gwybodaeth grynodeb | Summary information .............................................................................................. 3 Hanes gweinyddol / Braslun bywgraffyddol | Administrative history | Biographical sketch ......................... 3 Natur a chynnwys | Scope and content .......................................................................................................... 5 Trefniant | Arrangement .................................................................................................................................. 6 Nodiadau | Notes ............................................................................................................................................ -

Series 16/160/18/180-Model B Maintenance Manual, GFZ-62445E

GE Fanuc Automation Computer Numerical Control Products Series 16 / 160 / 18 / 180 – Model B Maintenance Manual GFZ-62445E/03 January 1995 B–62445E/03 PREFACE PREFACE Description of 1.CRT/MDI display and operation this manual This chapter covers those items, displayed on the CRT, that are related to maintenance. A list of all supported operations is also provided at the end of this chapter. 2.Hardware This chapter covers hardware–related items, including the hardware configuration, connection, and NC status indicated on printed circuit boards. A list of all units is also provided as well as an explanation of how to replace each unit. 3.Data input/output This chapter describes the input/output of data, including programs, parameters, and tool compensation data, aswell as the input/output procedures for conversational data. 4.Interface between the NC and PMC This chapter describes the PMC specifications, the system configuration, and the signals used by the PMC. 5.Digital servo This chapter describes the servo tuning screen and how to adjust the reference position return position. 6.and 7. AC spindles These chapters describe the spindle amplifier checkpoints, as well as the spindle tuning screen. 8.Trouble shooting This chapter describes the procedures to be followed in the event of certain problems occurring, for example, if the power cannot be turned on or if manual operation cannot be performed. Countermeasures to be applied in the event of alarms being output are also described. 9.and 10. Spindle trouble shooting These chapters explain the alarms related to spindles, as well as the corresponding countermeasures to be applied. -

Serie Nfórmate Sobre... Deporte Adaptado

Serie infórmate sobre... Nº 5 Deporte Adaptado Deporte adaptado Autor: Raquel María Moya Cuevas. Prólogo: Raquel María Moya Cuevas. Coordinación de la edición: Ceapat-Imserso. Diseño de la portada: Ceapat-Imserso. Fecha publicación web: junio 2014. Colaboradores: ¾ Luisa García Calvente: técnico superior de actividades técnicas y profesiona les del Ceapat. ¾ Joseba González Angulo: coordinador deportivo. ¾ Dr. Javier Pérez-Tejero: profesor de la Facultad de Ciencias de la Actividad Física y Deporte del INEF; director de Centro de Estudios sobre Deporte In clusivo del CEDI, Universidad Politécnica de Madrid. Autor del capítulo 2. ¾ Elies Soler Machirant: director gerente de Rodem Ortotec S.L. Revisión: Reyes Noya Arnaiz, Isabel Valle Gallego y Ángela Vigara Cerrato. Edición en formato accesible: Pilar Martínez. Empresas colaboradoras: ¾ Invacare, S.A. ¾ Kinethic hand made bikes. ¾ Otto Bock Ibérica, S.A. ¾ Sunrise Medical, S.L. Acceso, mediante código QR, a la descarga del documento 2 A lo largo del documento se pueden encontrar referencias a nombres comerciales distribuidos en España. Las imágenes de los productos utilizados como ejemplo pertenecen a las empresas que los distribuyen referenciadas con su nombre, al banco de datos de imágenes del Comité Paralímpico Español, junto al del Centro de Estudios sobre Deporte Inclusivo (CEDI) y al banco de fotos personales de Luisa García Calvente y Raquel María Moya Cuevas. Para obtener más información sobre los productos de apoyo que se mencionan y las empresas que los distribuyen, puede consultarse el Catálogo de Productos de Apoyo que recoge el Ceapat en: www.catalogo-ceapat.org Ceapat-Imserso Calle Los Extremeños, 1 (esquina avenida Pablo Neruda) 28018 Madrid Teléfono: 91 703 31 00 [email protected] www.ceapat.es Desde el Ceapat-Imserso, presentamos con enorme satisfacción y compromiso, un nuevo documento con el título Infórmate sobre.. -

Instruction Manual

EN7528563-00 07 - 2017 LGN power DYNACIAT Instruction manual EN CONTENTS PAGE 1 INTRODUCTION 2 15 INSTALLATION ANTIFREEZE PROTECTION 13 2 SHIPMENT OF THE UNIT 3 16 ELECTRICAL CONNECTIONS 13 3 RECEIPT OF GOODS 3 16.1 Power connection 13 3.1 Checking the equipment 3 16.2 Connection to the air-cooled condenser. 14 3.2 Identifying the equipment 3 16.3 Customer connection for remote 4 SAFETY INSTRUCTIONS 4 control functions. 15 5 MACHINE COMPLIANCE 4 17 CONTROL AND SAFETY DEVICES 16 17.1 Electronic control and display module 16 6 WARRANTY 4 17.2 Main functions 16 7 UNIT LOCATION 4 17.3 Safety device management 16 8 HANDLING AND POSITIONING 5 17.4 Phase controller kit 17 17.5 Location of the safety sensors and devices 18 9 LOCATION 6 17.6 Adjusting the control and safety devices 19 9.1 Location of the unit 6 18 COMMISSIONING 19 10 OPERATING LIMITS 7 18.1 Commissioning 19 10.1 Operating range 7 18.2 Essential points that must be checked 20 10.2 Limits 7 19 TECHNICAL CHARACTERISTICS 21 10.3 Evaporator limits 7 10.4 Minimum/maximum water flow rates 7 20 ELECTRICAL SPECIFICATIONS 22 11 LOCATION OF THE MAIN COMPONENTS 8 21. SERVICING AND MAINTENANCE 23 12 MAIN COMPONENTS OF THE 21.1 Operating readings 23 REFRIGERATING CIRCUIT 8 21.2 Unit maintenance and servicing 23 13 HYDRAULIC CONNECTIONS 9 22 ECODESIGN 25 13.1 Diameters of the hydraulic connections 9 23 PERMANENT SHUTDOWN 25 13.2 Connections 10 24 TROUBLESHOOTING OPERATING 13.3 FLANGE/VICTAULIC adapter kit (OPTION) 10 PROBLEMS 26 14 REFRIGERANT CONNECTIONS 11 25 SYSTEM SCHEMATICS 27 14.1 General information 11 25.1 ooling installation with drycooler 27 14.2 Accessories 11 14.3 Routing and sizing 11 14.4 Installation 12 ORIGINAL TEXT: FRENCH VERSION EN - 1 1 INTRODUCTION DYNACIATpower LGN series water chillers are designed to meet the air conditioning requirements of residential and office buildings as well as the requirements of manufacturing processes. -

Replacement Parts Price List

REPLACEMENT PARTS PRICE LIST Product Catalog 2021 Replacement Parts Price List 607 PENTAIR 2021 Parts Price Eff. 09-14-2020 PART NO. DESCRIPTION US LIST CAN. LIST PART NO. DESCRIPTION US LIST CAN. LIST 00B7027 ORNG ADPT 13.03 15.66 071019Z KIT HOLDNG WHEEL 2000 45 39.26 47.17 00B8083 CLMP ASY V-BAND 209.27 251.46 071037 SCR 3/8 16X1 SCKT HD CAP 18 8 SS 7.48 8.99 012484 KIT XFMR/CRCT BRKR 167.83 201.66 071046 KEY IMPELLER 3/16 SQ C 29.42 35.35 05055-0003 LENS CLEAR 7.33"DIA 99.30 119.32 071048 WSHR IMP RTNR C SERIES 16.91 20.32 05057-0098 RNG LG REPAIR SS NICHE 241.24 289.87 071131Z DRAIN PLUG WFE ALMD 6.96 8.36 05057-0118 GSKT COLOR KIT 57.16 68.68 071136Z KIT KNB PLSTC LOOP ASY 26.10 31.36 05101-0002 GSKT SUNSAVER LENS 18.29 21.98 071389 NIPPLE BRASS .25 7.30 8.77 05101-0004 SCR LEADER 10-24 2" FH SUNSAVER 07-521 8.74 10.50 071390 NIPPLE 1/4 PVC NPT CLOSE 7.30 8.77 05101-0005 SCR RTNR RUBB 07-1667 1.86 2.23 071403 NUT 3/8-16 BRS BRIGHT NICKEL PLATED 1.74 2.09 05103-0001 NUT SUNSTAR 07-1411 26.30 31.60 071404Z NUT WING KIT 1.4-20 SS 8200 16.06 19.30 05103-0101 GASKET WALL FTG 8099 61-4566 11.63 13.97 071406 NUT 1/4-20 SS HEX 1.74 2.09 05103-0103 FTG WALL LENS SUNSTAR 07-1261 52.53 63.12 071407 NUT 5/8-18.75 HEX 17/6 13.64 16.39 05166-0001 GASKET VNYL SM NICHE 07-5802 4.27 5.13 071412 NUT HEX NO. -

Original Sport Performance Indicators in Football 7- A

Rev.int.med.cienc.act.fís.deporte - vol. 19 - número 74 - ISSN: 1577-0354 Gamonales, J.M.; León, K.; Jiménez, A. y Muñoz, J. (2019) Indicadores de rendimiento deportivo en el fútbol-7 para personas con parálisis cerebral / Sport Performance Indicators in Football 7- A-Side for People with Cerebral Palsy. Revista Internacional de Medicina y Ciencias de la Actividad Física y el Deporte vol. 19 (74) pp. 309-328 Http://cdeporte.rediris.es/revista/revista74/artindicadores1023.htm DOI: http://doi.org/10.15366/rimcafd2019.74.009 ORIGINAL SPORT PERFORMANCE INDICATORS IN FOOTBALL 7- A-SIDE FOR PEOPLE WITH CEREBRAL PALSY INDICADORES DE RENDIMIENTO DEPORTIVO EN EL FÚTBOL-7 PARA PERSONAS CON PARÁLISIS CEREBRAL Gamonales, J.M.1; León, K.1,2; Jiménez, A.1 y Muñoz-Jiménez, J.1,2 1 Facultad de Ciencias de la Actividad Física y el Deporte. Universidad de Extremadura (España) [email protected], [email protected], [email protected], [email protected] 2 Universidad Autónoma de Chile (Chile) [email protected], [email protected] Spanish-English translator: Rocío Domínguez Castells. [email protected] ACKNOWLEDGEMENTS AND/OR FUNDING This work was developed by the Research Group for the Optimization of Training and Sport Performance (Grupo de Optimización del Entrenamiento y Rendimiento Deportivo, G.O.E.R.D.) of the Faculty of Sport Sciences of the University of Extremadura. This work has been supported by the funding for research groups (GR15122) of the Government of Extremadura (Employment and infrastructure officeConsejería de Empleo e Infraestructuras), with the contribution of the European Union through the European Regional Development Fund (ERDF). -

2019 NFCA Texas High School Leadoff Classic Main Bracket Results

2019 NFCA Texas High School Leadoff Classic Main Bracket Results Bryan College Station BHS CSHS 1 Bryan College Station 17 Thu 3pm Thu 3pm Cedar Creek BHS CSHS EP Eastlake SA Brandeis 49 Brandeis College Station 57 Cy Woods 1 BHS Thu 5pm Thu 5pm CSHS 2 18 Thu 1pm Brandeis Robinson Thu 1pm EP Montwood BHS CSHS Robinson 11 Huntsville 3 89 Klein Splendora 93 Splendora 9 BHS Fri 2pm Fri 2pm CSHS 3 Fredericksburg Splendora 19 Thu 9am Thu 9am Fredericksburg 6 VET1 VET2 Belton 6 Grapevine 50 58 Richmond Foster 11 BHS Thu 5pm Klein Splendora Thu 5pm CSHS 4 20 Thu 11am Klein Richmond Foster Thu 11am Klein 11 BHS CSHS Rockwall 2 SA Southwest 9 97 SA Southwest Cedar Ridge 99 Cy Ranch 7 VET1 Fri 4pm Fri 4pm CP3 5 Southwest Cy Ranch 21 Thu 11am Thu 1pm Temple 5 VET1 CP3 Plano East 5 Clear Springs 2 51 Southwest Alvin 59 Alvin VET1 Thu 3pm Thu 5pm CP3 6 22 Thu 9am Vandegrift Alvin Thu 3pm Vandegrift 5 BHS CSHS Lufkin San Marcos 5 90 94 Flower Mound 0 VET2 Fri 12pm Southwest Cedar Ridge Fri 12pm CP4 7 San Marcos Cedar Ridge 23 Thu 9am Thu 1pm Magnolia West 3 VET2 CHAMPIONSHIP CP4 RR Cedar Ridge 12 McKinney Boyd 3 52 Game 192 60 SA Johnson VET2 Thu 3pm San Marcos BHS Cedar Ridge Thu 5 pm CP4 8 4:00 PM 24 Thu 11am M. Boyd BHS 5 10 BHS Johnson Thu 3pm Manvel 0 129 Southwest vs. Cedar Ridge 130 Kingwood Park Bellaire 3 Sat 10am Sat 8am Deer Park VET4 BRAC-BB 9 Cedar Park Deer Park 25 Thu 11am Thu 1pm Cedar Park 5 VET4 BRAC-BB Leander Clements 13 53 Cedar Park MacArthur 61 SA MacArthur VET4 Thu 3pm Thu 5pm BRAC-BB 10 26 Thu 9am Clements MacArthur Thu 3pm Waco University 0 BHS CSHS Tomball Memorial Cy Fair 4 91 Friendswood Woodlands 95 Woodlands 2 VET5 Fri 8am Fri 8am BRAC-YS 11 San Benito Woodlands 27 Thu 11am Thu 1pm San Benito 10 VET5 BRAC-YS SA Holmes 1 Friendswood 10 54 62 Santa Fe VET5 Thu 3pm Friendswood Woodlands Thu 5pm BRAC-YS 12 28 Thu 9am Friendswood Santa Fe Thu 3pm Henderson 0 VET1 VET2 Lake Travis Ridge Point 16 98 100 B. -

Publication 938 15:26 - 30-MAR-2011

Userid: SD_5PQGB DTD tipx Leadpct: 0% Pt. size: 8 J Draft J Ok to Print PAGER/SGML Fileid: ...uments_1\Pub_938\4th Quarter_2010\P938_4Qtr_RPG_Final_Ron.xml (Init. & date) Page 1 of 100 of Publication 938 15:26 - 30-MAR-2011 The type and rule above prints on all proofs including departmental reproduction proofs. MUST be removed before printing. Publication 938 Introduction (Rev. March 2011) Section references are to the Internal Revenue Department Cat. No. 10647L Code unless otherwise noted. of the This publication contains directories relating Treasury to real estate mortgage investment conduits Internal (REMICs) and collateralized debt obligations Revenue Real Estate (CDOs). The directory for each calendar quarter Service is based on information submitted to the IRS during that quarter. This publication is only avail- Mortgage able on the Internet. For each quarter, there is a directory of new REMICs and CDOs, and a section containing Investment amended listings. You can use the directory to find the representative of the REMIC or the is- suer of the CDO from whom you can request tax Conduits information. The amended listing section shows changes to previously listed REMICs and CDOs. The update for each calendar quarter will (REMICs) be added to this publication approximately six weeks after the end of the quarter. Reporting Other information. Publication 550, Invest- ment Income and Expenses, discusses the tax treatment that applies to holders of these invest- ment products. For other information about Information REMICs, see sections 860A through 860G of the Internal Revenue Code (IRC) and any regu- lations issued under those sections. (And Other Publication 938 is only available electroni- cally. -

Nielsons (Well)

? ? I1 A’ Feet below 100+ the 0 datum Feet Entrance Prole of Upper Ancient Stream, A-A’ -550 feet Elevation: SS8 550 Mega 7,600 Feet 0 (Projected Prole Looking NW) ? (Surface) ? SS9 Dome ? I2 0 Datum (Horizontal and vertical 4 ? scales the same in this profile view) 12 (Down to I7) 2 600 0 30 60 Feet Mega I6 7 I4 I3 0 5 10 20 Meters Dome 10 650 I5 Partial Prole View ? ? 100 See Upper Ancient Stream ? ? ? Parallel Projected View ? ? Offset Box ? Well Looking NW (upper black lines), looking E (lower gray lines) I14 31 I15 Nielsons 700 Well 0 30 60 Feet Spiffy Deluxe (To Ancient ? Stream) 0 5 10 20 Meters Pit I16 (Rigging Upper Ancient ? I17 Tree) 0 Datum 15 (Horizontal and vertical E6 Stream Mudball 14 scales the same in profile view) Nielsons 750 Canyon -750 feet ? E7 I18 Well (To Bowlingball I20 29 200 Big Canyon) (To Sump) 34 Room E8 Entrance Pit Blind I19 Big Dolline I21 19 E13 Barrier ? TT Room ? Pit E14 ? TT TT ? Upper E16 13 I22 Ancient ? TT ? (Down to I9) (Dig) I8 734 Stream TT DDS8 5 ? 300 ? TT I7 I (Up to I6) 620 I Slither Bat 32 ? I DDS7 I F7 I Third I I I 27 6 I Quartzite I Pit Trap I I Dixie Cup I Upper Middle Ancient Stream I Pit Crawl I I23 Duplicate I I F6 80+ Room I 10 I I24 Offset Box I Dentist I I (Up to F8 Twin I ? Dome 30 I 10 I F4) Office 8 F14 Dixiecup I25 Domes 808 100+ Pit 43 Fools F15 (Up to I8) F9 I9 Bear Claw Pit Surface Sinkholes Bear Claw 6 19 DDS6 Pit Pit (Up to F10 (Choked) (Down to I11) TT F11) 4 45 I26 I10 727 (Plan View) F11 (Down to F14) ? Lower Level Bear 20 4 400 Upper Bear Claw Claw Pit Offset Box -

Classification Made Easy Class 1

Classification Made Easy Class 1 (CP1) The most severely disabled athletes belong to this classification. These athletes are dependent on a power wheelchair or assistance for mobility. They have severe limitation in both the arms and the legs and have very poor trunk control. Sports Available: • Race Runner (RR1) – using the Race Runner frame to run, track events include 100m, 200m and 400m. • Boccia o Boccia Class 1 (BC1) – players who fit into this category can throw the ball onto the court or a CP2 Lower who chooses to push the ball with the foot. Each BC1 athlete has a sport assistant on court with them. o Boccia Class 3 (BC3) – players who fit into this category cannot throw the ball onto the court and have no sustained grasp or release action. They will use a “chute” or “ramp” with the help from their sport assistant to propel the ball. They may use head or arm pointers to hold and release the ball. Players with a impairment of a non cerebral origin, severely affecting all four limbs, are included in this class. Class 2 (CP2) These athletes have poor strength or control all limbs but are able to propel a wheelchair. Some Class 2 athletes can walk but can never run functionally. The class 2 athletes can throw a ball but demonstrates poor grasp and release. Sports Available: • Race Runner (RR2) - using the Race Runner frame to run, track events include 100m, 200m and 400m. • Boccia o Boccia Class 2 (BC2) – players can throw the ball into the court consistently and do not need on court assistance. -

18418 JAPANESE Public Disclosure Authorized

18418 JAPANESE Public Disclosure Authorized ,* I 1 1998 Public Disclosure Authorized , - -~i iJr NN '., -- ~ ; : $e Public Disclosure Authorized F i.a IIf .,,, Public Disclosure Authorized I tFivJI4 rlvi i'> T2' D.C. vi Ar: Michele lannacci ''I' if xi l:f Jean-Louis Sarbib 15. 54, 71. 88 fl: Richard Lord 28, 36. 45. 62, 67. 74 ffi: Curt Carnemark/ ' ii' 'I > t * A-4U4 : Joyce Petruzzelli, Graphic Design Unit, III ',,' [lttr< f, : Spot Color Y5-797 - 1- : Debra Malovany, Graphic Design Unit, II '' ' rY'11 - if 2FF: Lesley Anne Simmons, Office of the Publisher, III ' ii'jiY)11- '"'I C-' X72bd Carolyn Knapp and John McCain, Office of the Publisher, 1'1 Stephanie Gerard, Office of the Publisher, 'I Fr 7$N< *t-At&-)frf f > Sherry Holmberg, Office of the Publisher, I"I ' f ISSN: 0252-2934 ISBN: 0-8213-4095-6 .',1' , ' ,' . 1998 1gW$RtiW4* 1998 . .tJ.. IBRD.. IFC..ICSiD..M.GA............................ vi JL7 IBRD, IDA, IFC6 ICSID MIGA... ............................. viii 1998.......................................................... xi 1998 W) W5t0fF ................................................... xii 1 998 I6!t......R.... .......................................................... 1 m Y &Ts I=-^, ..............................................................................13 2 X...it ...... 1998 .t ............................................ 13 7>?XA... ')''.........................................................2 2 77 >77 ............................................................ 30 3 -E ) / 7 >7 ..................................................