Assembler Instructions (BS2000/OSD)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Oracle Database User's Guide for Fujitsu Siemens BS2000/OSD

Oracle® Database User's Guide 10g Release 2 (10.2) for Fujitsu Siemens BS2000/OSD E10320-01 August 2007 Oracle Database User's Guide, 10g Release 2 (10.2) for Fujitsu Siemens BS2000/OSD E10320-01 Copyright © 2007, Oracle. All rights reserved. Primary Author: Brintha Bennet Contributing Author: Janelle Simmons The Programs (which include both the software and documentation) contain proprietary information; they are provided under a license agreement containing restrictions on use and disclosure and are also protected by copyright, patent, and other intellectual and industrial property laws. Reverse engineering, disassembly, or decompilation of the Programs, except to the extent required to obtain interoperability with other independently created software or as specified by law, is prohibited. The information contained in this document is subject to change without notice. If you find any problems in the documentation, please report them to us in writing. This document is not warranted to be error-free. Except as may be expressly permitted in your license agreement for these Programs, no part of these Programs may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose. If the Programs are delivered to the United States Government or anyone licensing or using the Programs on behalf of the United States Government, the following notice is applicable: U.S. GOVERNMENT RIGHTS Programs, software, databases, and related documentation and technical data delivered to U.S. Government customers are "commercial computer software" or "commercial technical data" pursuant to the applicable Federal Acquisition Regulation and agency-specific supplemental regulations. As such, use, duplication, disclosure, modification, and adaptation of the Programs, including documentation and technical data, shall be subject to the licensing restrictions set forth in the applicable Oracle license agreement, and, to the extent applicable, the additional rights set forth in FAR 52.227-19, Commercial Computer Software--Restricted Rights (June 1987). -

BS2000/OSD-BC ≥ V4.0, OSD-SVP V4.0 and OSD/XC V1.0 with SPOOL ≥ V4.4A – Openft for BS2000 As of V7.0 Und Openft-AC for BS2000 As of V7.0

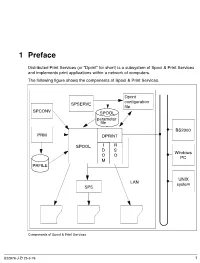

1Preface Distributed Print Services (or “Dprint” for short) is a subsystem of Spool & Print Services and implements print applications within a network of computers. The following figure shows the components of Spool & Print Services. Dprint configuration SPSERVE file SPCONV SPOOL parameter file BS2000 PRM DPRINT SPOOL I R D S Windows O O PC M PRFILE UNIX LAN system SPS Components of Spool & Print Services U22878-J-Z125-6-76 1 Brief product description Preface 1.1 Brief product description Distributed Print Services (known as “Dprint” for short) implements print applications in a network consisting of computers which use the BS20000/OSD, UNIX and Windows operating systems. Dprint utilizes TCP/IP, ISO or NEA (TRANSDATA) transport protocols. Dprint requires SPOOL as its execution unit and expands the print capabilities of SPOOL in respect of host-wide and network-wide utilization of the local BS2000 high-performance printers. Dprint supports network-wide access to BS2000 printers, printers attached to UNIX systems and Windows printers, i.e. interoperability between BS2000, Xprint and Wprint is possible. This means that data from a Windows PC can be output to a BS2000 printer. It is also possible to output data from BS2000 on a printer which is connected to a Windows PC. This then runs via a UNIX system. Dprint is designed as a client/server model and comprises the following components: – DPRINTCL (client component: print job generation) – DPRINTSV (server component: print job management) – DPRINTCM (implements management services, file transfer, communication, etc.) These components are installed as independent subsystems. DPRINTCL and DPRINTCM are combined to form the selectable unit DPRINT-CL, and DPRINTSV is supplied as the selectable unit DPRINT-SV. -

Přehled Serverových Řešení Fujitsu

Fujitsu – nejen DC HW ORTEX - WS 25.10.2018 [email protected] 0 © 2018 FUJITSU Fujitsu DC portfolio ETERNUS storage PRIMERGY servery včetně SW partnerů ETERNUS CS Data Protection Appliances ETERNUS CS200c Octo PQ Quad BS2000 Software TX & RX Služby Dual Scale Up/SMP Computing Up/SMP Scale ETERNUS CD ETERNUS DX/AF 10000 JX40/JX60 Disk Storage Hyper-scale LT JBOD system Mono Storage Tape Storage Kooperace s partnery CX Scale Out/Distributed Computing 1 © 2018 FUJITSU Portfolio serverů Fujitsu Fujitsu jako jediná firma na světě s kompletní nabídkou serverů. PRIMERGY PRIMEQUEST SPARC BS2000 Zkušenosti s vývojem a x86 servery pro provoz UNIX servery s jasnou Mainframe výrobou x86 serverů již od Mission-critical aplikací. roadmapou roku 1994 2 © 2018 FUJITSU Více než 20 let zkušeností Servery inspirované požadavky zákazníků First First x86 Converged Infrastructure First massive scale-out Cool-safe® ATD PRIMERGY First blade server Platform (PRIMERGY computing platform for web New levels of In- with support for server (PRIMERGY BX300) BladeFrame) hosters and telcos Memory computing up to 45°C 1994/95 2002 2005 2009 2014 2016 1998/99 2004 2008 2012 2015 First scale-up 8- Best-in-class cooling Virtual I/O First vendor offering a Cool-Central Liquid way x86 server concept (Cool-safe® management ‘Cluster-in-a-box’ solution Cooling Technology technology) … vývoj se zaměřením na jednoduchou obsluhu a nízké TCO Management Highest Highest-levels across the Usability & Versatile efficiency of reliability lifecycle Serviceability performance 3 © 2018 FUJITSU Doživotní záruka www.zatorucim.cz 4 © 2018 FUJITSU FUJITSU Server PRIMERGY Tower systems Robust and cost-efficient tower servers which are performance oriented, affordable and expandable. -

Datasheet Search Site |

Datasheet Fujitsu SPARC Enterprise M8000 server Datasheet Fujitsu SPARC Enterprise M8000 server Provides the enterprise start point for large database. ERP and OLTP applications plus total stability, flexibility and asset protection. Only the best with Fujitsu SPARC Enterprise A SPARC of steel Based on robust SPARC architecture and As you would expect in a server aimed at your running the leading Oracle Solaris 11, Fujitsu most important tasks, Fujitsu SPARC Enterprise SPARC Enterprise servers are ideal for M8000 has all the qualities of a mainframe. customers needing highly scalable, reliable Absolutely rock solid, dependable and servers that increase their system utilization sophisticated, it has the total Solaris binary and performance through virtualization. compatibility necessary to both protect your investments and enhance your business. The combined leverage of Fujitsu’s expertise in mission-critical computing technologies and Its rich virtualization eco-system of extended high-performance processor design, with partitioning and Solaris Containers coupled Oracle’s expertise in open, scalable, with dynamic reconfiguration, means partition-based network computing, provides non-stop operation and total resource the overall flexibility to meet any task. utilization at no extra cost. Benchmark leading performance with the world’s best applications and outstanding processor scalability just add to the capabilities of this attractive open system platform. Page 1 of 8 www.fujitsu.com/sparcenterprise Datasheet Fujitsu SPARC Enterprise M8000 server Features and benefits Main features Benefits Flexible investment protection All SPARC64 VI dual-core processor and SPARC64 VII/VII+ quad-core Investment protection for years to come, less risk and lower cost of processor can be mixed and matched in the servers and even ownership. -

Fujitsu Product Support Services – at a Glance

FUJITSU Product Support Services Fujitsu Product Support Services – At a Glance In addition to cutting-edge products, Fujitsu delivers worldwide Product Support Services. A comprehensive product support portfolio containing standard break/fix services as well as proactive support helps our customers to save time and money and reduces the burden on internal IT staff. Fujitsu delivers Product Support Services through certified support engineers for individual products as well as for IT infrastructures as a “one stop shop” support offering. The services range from installing new products to providing fast and responsive support for Fujitsu hardware, software and IT infrastructures for solution business. The right mix of Product Support Services from Fujitsu enables optimal early planning for the availability of our customers’ IT systems required for their state-of-the art business operation. Fujitsu Startup Services Hardware Fujitsu Product Support Hardware and Software Fujitsu Product Support Hardware InstallationPacks support the customer in the installation of storage The offerings are available as Product Support Hardware complements Fujitsu’s product warranty. It and server products including the related operating software, as ■ Fujitsu Support Pack Hardware and Software comprises reactive service elements focusing on diagnosis of hardware applicable. They grant fast start and reliable operation of the purchased with a defined service period between 1 and 5 years and up-front faults and their elimination by repair or replacement. The service is system in the customer environment. payment. Prolongation is possible. delivered remotely, offsite or onsite. Customers may choose: ■ Fujitsu ServiceContract Hardware and Software ■ Service time, onsite response time and recovery time. starting with service duration of 12 months and automatic ■ Proactive Support for selected products to enhance availability prolongation. -

Datasheet Fujitsu SPARC M10-4S

Datasheet Fujitsu SPARC M10-4S Datasheet Fujitsu SPARC M10-4S Everything your mission critical enterprise application needs in stability, scalability and asset protection Only the best with Fujitsu SPARC Enterprise A SPARC of steel Based on robust SPARC architecture and running the Fujitsu SPARC M10-4S server is the nearest thing you leading Oracle Solaris 11, Fujitsu SPARC M10-4S can get to an open mainframe. Absolutely rock servers are ideal for customers needing highly solid, dependable and sophisticated, but with the scalable, reliable servers that increase their system total Solaris binary compatibility necessary to both utilization and performance through virtualization. protect your investments and enhance your business. The combined leverage of Fujitsu’s expertise in mission-critical computing technologies and Its rich virtualization eco-system of extended high-performance processor design, with Oracle’s partitioning and Solaris Containers coupled with expertise in open, scalable, partition-based network dynamic reconfiguration, means non-stop operation computing, provides the overall flexibility to meet and total resource utilization at no extra cost. any task. Benchmark leading performance with the world’s best applications and outstanding processor scalability just add to the capabilities of this most expandable of system platform. Page 1 of 6 www.fujitsu.com/sparc Datasheet Fujitsu SPARC M10-4S Features and benefits Main features Benefits Supreme performance The supreme performance in all commercial servers Highest performance -

Fujitsu-Siemens BS2000/OSD Mainframes

SCORE® ADAPTIVE BRIDGES™ Maximize your ROEI ... ... Return On Existing Investment Fujitsu-Siemens BS2000/OSD Mainframes This platform guide helps you to learn about the way SCORE Adaptive Bridges generates server-side code to implement adaptive services for business critical applications on Fujitsu-Siemens BS2000/OSD business servers. Reuse your BS2000/OSD applications and data stores in a service-oriented architecture. SCORE® Adaptive Bridges™ – the latest ported on the BS2000/OSD platform. version of Delta’s proven legacy inte- gration technology that enables you to 18 Years BS2000 increase the value of your enterprise Delta has supported the BS2000/OSD projects by reducing the cost of integrat- platform since the mid 1980s with the ing your existing application assets. Delta/ADS and Delta/DBI COBOL code generators. Delta leverages this experi- Application Reuse ence in the design, implementation and SCORE Adaptive Bridges enables your testing of SCORE Adaptive Bridges for existing BS2000/OSD applications and the BS2000/OSD platform. databases to participate, unchanged, as adaptive services in a flexible service- BS2000/OSD oriented architeture. SCORE Adaptive Bridges generates adaptive services in COBOL2000 for Adaptive services are generated as a BS2000/OSD running on the S model series of layers. Please see the Runtime (/390 CMOS), SR model (MIPS RISC View flyer or our Web site for an intro- CMOS) and the SX model (SPARC64) duction to the layer architecture and series. There are no specific hardware “what goes where.” This flyer focuses or operating system requirements. on how the server-side layers are sup- Model Driven Legacy Integration™ Solaris application program that integrates seamlessly with your adaptive services. -

BS2000/OSD Partners

Issue June 2009 BS2000/OSD Partners Use External Pages 4 Optimal solutions due to cooperation with partners In supplying applications Fujitsu Technology Solutions closely cooperates with partners. Their tailor-made solutions fulfill optimally the IT needs of our customers and extend the product portfolio of Fujitsu Technology Solutions to a complete offer of industry-sector-specific products, solutions and services. Software partners offer solutions whose strengths can be exploited to the full under BS2000/OSD. hardware partners supplement the hardware offering of Fujitsu Technology Solutions with their own products. Service partners carry out a whole range of services in the BS2000/OSD environment. Contents Optimal solutions due to cooperation with partners 1 BS2000/OSD Service Partners 2 BS2000/OSD Software and Hardware Partners 3 Additional information in the internet on partners and their products 4 Summary ⏐ Issue: June 2009 ⏐ BS2000/OSD Partners ⏐ Use: External Page 2 / 4 BS2000/OSD Service Partners Company Description best-blu Systems GmbH The best-blu systems GmbH is a consultancy that focuses on the design and optimization of processes in data centers. The portfolio spans from consulting, via design and implementation through to extensive operational support for complete IT solutions. Operational and consulting as well as implementation services are provided. www.mysec.de/content/en/bbgroup/1start.php CCP GmbH CCP provides services in the IT sector embraced by the term “IT modeling” and provides assistance in the sales and marketing departments of its customers embraced by the term “sales and marketing optimization". www.ccp1.eu ( German ) GRASS-MERKUR AG & Co. KG The Grass GmbH is the professional partner dealing with all aspects of equipment, operation, optimization of IT services for companies, no matter if centrally aligned in your data center or spread out over client server environments. -

FUJITSU Software BS2000 VM2000 Version V11.0A October 2019

FUJITSU Software BS2000 VM2000 Version V11.0A October 2019 Release Notice All rights reserved, including intellectual property rights. Technical data subject to modifications and delivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded. Designations may be trademarks and/or copyrights of the respective manufacturer, the use of which by third parties for their own purposes may infringe the rights of such owner. © 2019 Fujitsu Technology Solutions GmbH Fujitsu and the Fujitsu logo are trademarks or registered trademarks of Fujitsu Limited in Ja- pan and other countries. BS2000 is a trademark of Fujitsu Technology Solutions GmbH in Ger- many and other countries. 1 General 3 1.1 Ordering 3 1.2 Delivery 3 1.3 Documentation 4 2 Software extensions 5 2.1 Persistent VMs 5 2.2 Time slice extension for nucleus lock 5 2.3 VM2000 functions in the SE Manager 5 2.4 Command extensions 5 3 Technical information 6 3.1 Resource requirements 6 3.2 Software configuration 6 3.3 Product installation 6 3.4 Product use 6 3.5 Discontinued functions (and those to be discontinued) 7 3.6 Incompatibilities 7 3.7 Restrictions 7 3.8 Procedure in the event of errors 7 4 Hardware requirements 8 Release Notice VM2000 V11.0A Edition October 2019 1 General VM2000 is a virtual machine system that allows different, completely encapsulated system environments to be operated simultaneously on one system with a perfor- mance comparable to the "native" mode. Depending on the type of system, up to 32 BS2000 operating systems can be used simultaneously as guest systems. -

Installation in UNIX Systems

Print Server Installation in UNIX Systems Installation Manual Manufactured by: SEH Computertechnik GmbH Suedring 11 33647 Bielefeld Germany Phone: +49 (0)521 94226-29 Fax: +49 (0)521 94226-99 Document: Support: +49 (0)521 94226-44 Type: Installation Manual Email: [email protected] Title: Installation in UNIX Systems Web: http://www.seh.de Version: 1.0 Online Links to important Internet Resources: Free Guarantee Extention: http://www.seh-technology.com/guarantee Support Contacts and Informationen: http://www.seh-technology.com/support Sales Contact and Informationen: http://www.seh-technology.com/sales InterCon is a registered trademark of SEH Computertechnik GmbH. SEH Computertechnik GmbH has endeavoured to ensure that the information in all manuals is correct. If you detect any inaccuracies please inform us at the address indicated below. SEH Computertechnik GmbH will not accept any liability for any error or omission. The information in this manual is subject to change without notification. All rights are reserved. Copying, other reproduction or translation without the prior written consent from SEH Computertechnik GmbH is prohibited. © 2007 SEH Computertechnik GmbH All trademarks, registered trademarks, logos and product names are property of their respective owners. Table of Contents 1 Information. 5 1.1 ... about the Documentation . 6 1.2 ... about Support and Current Services . 8 1.3 ... about Your Safety. 9 1.4 ... about the Printing Methods and Installation Procedures . 10 1.5 ... about the Assignment of the IP Address to the Host Name . 12 1.6 ... about the Saving of the IP Address in the Print Server . 13 2 Printing via the LPD Protocol . -

FUJITSU Software BS2000 Support for ETERNUS AF650 S3 April 2020

FUJITSU Software BS2000 Support for ETERNUS AF650 S3 April 2020 Release Notice All rights reserved, including intellectual property rights. Technical data subject to modifications and delivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded. Designations may be trademarks and/or copyrights of the respective manufacturer, the use of which by third parties for their own purposes may infringe the rights of such owner. © 2020 Fujitsu Technology Solutions GmbH Fujitsu and the Fujitsu logo are trademarks or registered trademarks of Fujitsu Limited in Japan and other countries. BS2000 is a trademark of Fujitsu Technology Solutions GmbH in Germany. 1 General 3 Ordering 3 Delivery 3 Documentation 3 2 Software-Extensions 4 3 Technical Information 4 Software-Configuration 4 Product use 4 Discontinued functions (and those to be discontinued) 4 Restrictions 4 Procedure in the event of errors 5 4 Hardware-Requirements 5 X2000 Requirements 5 Special Functions 5 5 Firmware-Levels 5 ETERNUS AF650 S3 Storage-Systems 5 Brocade FC-Switches 5 Release notice ETERNUS AF650 S3 under BS2000 Edition April 2020 1 General This Release Notice is a summary of the major extensions, dependencies and operating information with respect to connections of Fujitsu disk controller of the ETERNUS1 AF650 S3 under the BS2000 operating system. The release level is of: April 2020. This and other current Release Notices are shipped on the SoftBooks DVD and are available online at https://bs2manuals.ts.fujitsu.com. Additionally, the release notices of OSD/BC, OSD/XC and SHC-OSD have to be taken into account (depending on the installed hardware and software): The disk controller AF650 S3 of the Fujitsu company can be used as peripheral system in a BS2000 environment. -

BS2000/OSD) Version 3.6A January 2009

Fujitsu Technology Solutions RSO (BS2000/OSD) Version 3.6A January 2009 Release Notice All rights reserved, including intellectual property rights. Technical data subject to modifications and delivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded. Designations may be trademarks and/or copyrights of the respective manufacturer, the use of which by third parties for their own purposes may infringe the rights of such owner. Copyright © Fujitsu Technology Solutions 2009 Release Notice RSO V3.6A (BS2000 V/OSD) 1 General 2 1.1 Ordering 2 1.2 Delivery 2 1.3 Documentation 4 2 Software extensions 5 3 Technical information 6 3.1 Resource requirements 6 3.2 Software configuration 6 3.3 Product installation 6 3.4 Product use 8 3.5 Discontinued functions (and functions to be discontinued) 9 3.6 Incompatibilities 9 3.7 Restrictions 9 3.8 Procedure in the event of errors 10 4 Hardware support 10 1 1 General This Release Notice contains outline descriptions of the major expansions, interdependencies and application notes pertaining to RSO V3.6 under the operating system BS2000/OSD-BC >= V6.0 (1). The contents correspond to release status of January 2009. The Release Notice is supplied as a text file. The typogra- phical conventions for uppercase and lowercase are observed in the file. Updated versions of the file will be supplied as and when modifications to the product are registered. The command for printing this file (English version) is /PRINT-DOCUMENT SYSFGM.RSO.036.E, - / DOCUMENT-FORMAT=*TEXT(LINE-SPACING=*BY-EBCDIC-CONTROL) or /PRINT-FILE SYSFGM.RSO.036.E,CONTROL-CHARACTER=EBCDIC If the use of this product version means that one or more predecessor versions are skipped, the notes in the Release Notices (or README files) of the predecessor version or versions must also be taken into account.