Chapter VIII: Design and Operation of Automatic Gain Control Loops For

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Wideband Automatic Gain Control Design in 130 Nm CMOS Process for Wireless Receiver Applications

Wideband Automatic Gain Control Design in 130 nm CMOS Process for Wireless Receiver Applications A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering By Joseph Benito Strzelecki, B.S. Wright State University, 2013 2015 Wright State University WRIGHT STATE UNIVERSITY GRADUATE SCHOOL _August 19, 2015_______ I HEREBY RECOMMEND THAT THE THESIS PREPARED UNDER MY SUPERVISION BY Joseph Benito Strzelecki ENTITLED Wideband Automatic Gain Control Design in 130 nm CMOS Process for Wireless Receiver Applications BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Master of Science in Engineering. ___________________________________ Saiyu Ren, Ph.D. Thesis Director ___________________________________ Brian D. Rigling, Ph.D. Department Chair Committee on Final Examination ________________________________ Saiyu Ren, Ph.D. ________________________________ Raymond E. Siferd, Ph.D. ________________________________ John M. Emmert, Ph.D. ________________________________ Arnab K. Shaw, Ph.D. ________________________________ Robert E. W. Fyffe, Ph.D. Vice President for Research and Dean of the Graduate School Abstract Strzelecki, Joseph Benito, M.S.Egr, Department of Electrical Engineering, Wright State University, 2015. “Wideband Automatic Gain Control Design in 130 nm CMOS Process for Wireless Receiver Applications” An analog automatic gain control circuit (AGC) and mixer were implemented in 130 nm CMOS technology. The proposed AGC was intended for implementation into a wireless receiver chain. Design specifications required a 60 dB tuning range on the output of the AGC, a settling time within several microseconds, and minimum circuit complexity to reduce area usage and power consumption. Desired AGC functionality was achieved through the use of four nonlinear variable gain amplifiers (VGAs) and a single LC filter in the forward path of the circuit and a control loop containing an RMS power detector, a multistage comparator, and a charging capacitor. -

A Wide Range and High Speed Automatic Gain Control

11111,.o 0 c_ SSCL-Preprint-407 = May 1993 "_ Distribution Category: 400 ' E. Tacconi rar_ t.. ' _ C Christiansen or3 ._ A Wide Range and High Speed Automatic Gain Control Superconductl "n g Super Collider Laboratory DISTRIIBLITION OF THIS DOCUMENT IS UNLIMITEi_ Disclaimer Notice This reportwas preparedas an account of work sponsoredby an agency of the UnitedStates Government. Neither the United States Governmentor any agency thereof, nor any of their employees,makesany warranty,expressor implied,or assumesanylegal liabilityor responsibility for the accuracy,completeness,or usefulnessof any information,apparatus,product,or process disclosed,or representsthat its usewouldnotinfringeprivatelyowned rights.Reference hereinto any specificcommercial product,process,or serviceby trade name, trademark, manufacturer,or otherwise, does notnecessarilyconstituteor implyits endorsement,recommendation,or favoring by the United States Government or any agency thereof. The views and opinionsof authors expressed herein donot necessadlystate or reflectthose ofthe UnitedStates Governmentor any agency thereof. Superconducting Super Collider Laboratory is an equal opportunity employer. SSCL-Preprint-407 A Wide Range and High Speed Automatic Gain Control* E. Tacconi and C. Christiansen Superconducting Super Collider Laboratory t 2550 Beckleymeade Ave. Dallas, TX 75237 May 1993 _ _' -12 -. _" *Presented at the 1993 IEEE Particle Accelerator Conference on May 17-20, Washington, D.C. *Operated by the Universities Research Association, Inc., for the U.S. Department of Energy under Contract No. DE-AC35-89ER40486. 131STRIBUI'ION OF THIS DOCUMENT IS UNLIMIT i=-O A Wide Range and High Speed Automatic Gain Control Eugenio J. Tacconit and Carlos F. Christiansen t Superconducting Super Collider Laboratory* 2550 Beckleymeade Avenue Dallas, Texas 75237 Abstract maximum loop gain, and a poor dynamic behavior is obtained Automatic gain control (AGC) techniques have been largely for low-gain operating points. -

An Empirical Characterization of Concrete Channel and Modulation Schemes with Piezoelectric Transducers Based Transceivers

AN EMPIRICAL CHARACTERIZATION OF CONCRETE CHANNEL AND MODULATION SCHEMES WITH PIEZO ELECTRIC TRANSDUCERS BASED TRANSCEIVERS A Thesis Presented to the Faculty of the Department of Electrical and Computer Engineering University of Houston In Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering by Sai Shiva Kailaswar August 2012 AN EMPIRICAL CHARACTERIZATION OF CONCRETE CHANNEL AND MODULATION SCHEMES WITH PIEZOELECTRIC TRANSDUCERS BASED TRANSCEIVERS _______________________________________ Sai Shiva Kailaswar Approved: ______________________________ Chair of the Committee Dr. Rong Zheng, Associate Professor Electrical and Computer Engineering Committee Members: ______________________________ Dr. Zhu Han, Associate Professor Electrical and Computer Engineering ______________________________ Dr. Yuhua Chen, Associate Professor Electrical and Computer Engineering ______________________________ ______________________________ Dr. Suresh Khator, Dr. Badri Roysam, Associate Dean Professor and Chairman Cullen College of Engineering Electrical and Computer Engineering ACKNOWLEDGEMENTS This research would not have been possible without the support of God Almighty and all praise to him. I owe my deepest gratitude to Dr. Rong Zheng for giving me an opportunity to pursue my Master’s thesis under her esteemed guidance. Without her support and assistance, this project would not have been possible. Her timely support, encouragement, and logical thinking have greatly inspired me to keep my spirits high throughout the research. I would like to thank Dr. Zhu Han and Dr. Yuhua Chen for accepting my invitation to serve on my thesis committee. It gives me pleasure to thank all the members of the Wireless System Research Group, especially Mr. Guanbo Zheng. I would like to dedicate my work to my beloved parents, brother, Mr. Kishore Potta, and sister-in-law Mrs. -

Replacing the Automatic Gain Control Loop in a Mobile, Digital TV Broadcast Receiver by a Software Based Solution

Replacing the automatic gain control loop in a mobile, digital TV broadcast receiver by a software based solution diploma thesis Patrick Boettcher Technische Fachhochschule Wildau Fachbereich Betriebswirtschaft/Wirtschaftsinformatik Date: 09.03.2008 Erstbetreuer: Prof. Dr. Christian Müller Zweitbetreuer: Prof. Dr. Bernd Eylert ii A part of this diploma thesis is not available until April 2010, because it is protected by a lock flag. The complete work can and will be made available by that time. The parts affected are – Chapter 4, – Chapter 5, – Appendix C and – Appendix D. If by that time you cannot find the complete work anywhere, please contact the author. iii Danksagung An dieser Stelle möchte ich all jenen danken, die durch ihre fachliche und persönliche Unterstützung zum Gelingen dieser Diplomarbeit beigetragen haben. Besonderer Dank gebührt meiner Lebenspartnerin Ariane und meinen Eltern, die mir dieses Studium durch ihre Unterstützung ermöglicht haben und mir fortwährend Vorbild und Ansporn waren. Weiterhin bedanke ich mich bei Professor Dr. Christian Müller und Professor Dr. Bernd Eylert für die Betreuung dieser Diplomarbeit. Großer Dank gilt ebenfalls meinen Kollegen bei DiBcom S.A., die mir die Möglichkeit gaben, diese Arbeit zu verfassen und mich technich sehr stark unterstützten. Vor allem möchte ich mich in diesem Zusammenhang bei Jean-Philippe Sibers bedanken, der mir immer mit einer Inspriration zur Seite stand. Gleiches gilt für das „Physical Layer Software Team“: Luc Banda, Frédéric Tarral und Vincent Recrosio. Acknowledgment I want to use this opportunity to thank everyone who supported me personally and professionally to create this diploma thesis. Special thanks appertain to my partner Ariane and my parents, who supported me during my studies and who continuously guided and motivated me. -

A Wide Range and High Speed Automatic Gain Control Eugenio J

© 1993 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. A Wide Range and High Speed Automatic Gain Control Eugenio J. Tacconit and Carlos F. Christiansen~ Superconducting Super Collider Laboratory* 2550 Beckleymeade Avenue, MS 4004 Dallas, Texas 75237 Abstract The gain of the controlled amplifier is a function of the Automatic gain control (AGC) techniques have been control voltage x(t). Thus, the control system is non linear largely used since the beginning of electronics but in most of and gain loop and stability are usually dependent on the the applications the dynamic responseis slow compared with operating point. The system has to be designed in order to be the carrier frequency. The problem of developing an stable for the maximum loop gain and a poor dynamic automatic gain control having simultaneously high dynamic behavior is obtained for low gain operating points. The effect response‘and wide control range is analyzed in this work. An of the gain control law on the loop gain variation range is ideal gain control law, having the property that the total loop analyzed in the next section. gain remains constant independent of the carrier amplitude, is obtained. The resulting AGC behavior is compared, by It. GAINCONTROL LAW computer simulations, with a linear multiplier AGC. The ideal gain control law can be approximated by using a The output of the variable gain amplifier is given by: transconductanceamplifier. -

Automatic Gain Control and Multi-Style Training for Robust Small-Footprint Keyword Spotting with Deep Neural Networks

AUTOMATIC GAIN CONTROL AND MULTI-STYLE TRAINING FOR ROBUST SMALL-FOOTPRINT KEYWORD SPOTTING WITH DEEP NEURAL NETWORKS Rohit Prabhavalkar1, Raziel Alvarez1, Carolina Parada1, Preetum Nakkiran2∗, Tara N. Sainath1 1Google Inc., Mountain View, USA; 2University of California, Berkeley, Department of EECS, USA fprabhavalkar, raziel, carolinap, [email protected] [email protected] ABSTRACT We explore techniques to improve the robustness of small-footprint keyword spotting models based on deep neural networks (DNNs) in the presence of background noise and in far-field conditions. We find that system performance can be improved significantly, with rel- ative improvements up to 75% in far-field conditions, by employing a combination of multi-style training and a proposed novel formula- tion of automatic gain control (AGC) that estimates the levels of both Fig. 1: Block diagram of DNN-based KWS system proposed in [2]. speech and background noise. Further, we find that these techniques allow us to achieve competitive performance, even when applied to method was shown to significantly outperform a baseline keyword- DNNs with an order of magnitude fewer parameters than our base- filler system. This system is appealing for our task because it can line. be implemented very efficiently to run in real-time on devices, and Index Terms— keyword spotting, automatic gain control, memory and power consumption can be easily adjusted by chang- multi-style training, small-footprint models ing the number of parameters in the DNN. Although the proposed system works extremely well in clean conditions, performance de- grades significantly when speech is corrupted by noise, or when the 1. INTRODUCTION distance between the speaker and the microphone increases (i.e., in far-field conditions). -

Application of AGC Technology in Software Radio

International Journal of Advanced Network, Monitoring and Controls Volume 03, No.04, 2018 Application of AGC Technology in Software Radio Wu Hejing East University of Heilongjiang 150086 e-mail: [email protected] Abstract—The characteristics of software radio are flexibility, (2) openness. Software radio adopts a standardized and openness, scalability. The hardware platform of software radio modular structure. Its hardware can be updated or expanded should be a general platform. This paper discusses automatic with the development of devices and technologies. gain control(AGC) technology in software radio receiver and (3) scalability. Software radio can be upgraded by introduces an AGC algorithm applicable for DSP implement. loading new software. This algorithm is tested in matlab and simulation results are III. ARCHITECTURE OF SOFTWARE RADIO provided. Software radio architecture is the concrete design Keywords-Software Radio; Characteristics; AGC; Matlab structure torealize the concept of software radio. It includes hardware, software and interface protocol. The design I. INTRODUCTION content must take into account the current situation and At present, software radio technology is widely used in long-term development of wireless communication wireless communication, its basic idea is to use hardware as technology. Really unifies each standard. The structure of the basic platform of wireless communication. The A/D ideal software radio is mainly composed of antenna, RF front sampling data of signals are processed by various algorithms, end, broadband A/D-D/A soft converter, General and special and various communication functions are realized by means digital signal processors and various software components. of software. This paper discusses the automatic gain control The antenna of software radio generally covers a wide (AGC) algorithm in software radio. -

MT-033: Voltage Feedback Op Amp Gain and Bandwidth

MT-033 TUTORIAL Voltage Feedback Op Amp Gain and Bandwidth INTRODUCTION This tutorial examines the common ways to specify op amp gain and bandwidth. It should be noted that this discussion applies to voltage feedback (VFB) op amps—current feedback (CFB) op amps are discussed in a later tutorial (MT-034). OPEN-LOOP GAIN Unlike the ideal op amp, a practical op amp has a finite gain. The open-loop dc gain (usually referred to as AVOL) is the gain of the amplifier without the feedback loop being closed, hence the name “open-loop.” For a precision op amp this gain can be vary high, on the order of 160 dB (100 million) or more. This gain is flat from dc to what is referred to as the dominant pole corner frequency. From there the gain falls off at 6 dB/octave (20 dB/decade). An octave is a doubling in frequency and a decade is ×10 in frequency). If the op amp has a single pole, the open-loop gain will continue to fall at this rate as shown in Figure 1A. A practical op amp will have more than one pole as shown in Figure 1B. The second pole will double the rate at which the open- loop gain falls to 12 dB/octave (40 dB/decade). If the open-loop gain has dropped below 0 dB (unity gain) before it reaches the frequency of the second pole, the op amp will be unconditionally stable at any gain. This will be typically referred to as unity gain stable on the data sheet. -

Stri-C 9, His Attorney

April 24, 1956 R. L. SNK 2,743,355 AUTOMATIC GAIN CONTROL CIRCUITS FOR PULSE RECEIVERS Filed April 21, 1948 2. Sheets-Sheet lb :-------? la 2. Fiidb. stri-cR -- 9, 2 PUSE TRANSMER PostON COntrol SYNChroniz NG CRCUS ANDrACKNG RANGE - circuits FS GATED video DYNERECEIVER FUSE h Anof1 r 7 NdICAOR CATHODe CONTRO rAY CRCU NOICATOr 76 VOAGEoutput 67 Error SGNAul OUT put InVentor : hrobert L. Simk, His attorney. April 24, 1956 R, L, SINK 2,743,355 AUTOMATIC GAIN CONTROL CIRCUITS FOR PULSE RECEIVERS Filed April 21, 1948 2 Sheets-Sheet 2 CYCLE OF 8Ob Fig3A.-- is 3. u CYCLE kD 79 OF 8Oc d - 2 O an -63a - -- - - -<1. 83b a Fe3C, "Ali. f N / N N M M Pyte N M N / O Fig3D." s al : r Sa er O N1 --> In Wentor: hrobert L. Sink, His attorney. 2,743,355 United States Patent Office Patented Apr. 24, 1956 and also to the appended claims in which the features 2,743,355 pointedof the inventionout. believed to be novel are particularly In the drawings: AUTOMATIC GAIN CONTROL CIRCUITS FOR Fig. 1 is a simplified block diagram of automatic radar PULSE RECEIVERS tracking system in which my invention is suitably em Robert L. Sink, Altadena, Calif., assignor to General Elec bodied; tric Company, a corporation of New York Fig. 2 is a schematic circuit diagram of an automatic gain control and error signal system which may be em Application April 21, 1948, Serial No. 22,421 0. ployed in the radar system of Fig. 1; 6 Claims. (C. -

Laboratory Exercise #7

ECEN4002/5002 Digital Signal Processing Laboratory Spring 2002 Laboratory Exercise #7 Nonlinear and Adaptive Processing Introduction An important area of real time DSP involves nonlinear and adaptive algorithms. Nonlinear systems include modulation/demodulation in communications, automatic gain control, noise and interference suppression, and various types of pulse forming and wave shaping schemes. In this experiment you will investigate a few processing tasks with data-dependent behavior, and systems in which signals are multiplied together. While for linear systems we have a great deal of analytical muscle in the form of transforms and decompositions based on the superposition property, for nonlinear systems we often must use “linearizing” assumptions like small signal models and perturbation analysis. Dynamic Range Compression There are a variety of situations in which it is desirable to modify the level of a signal using some sort of automatic adjustment. For example, we may have a detection algorithm that works best if its input signal is maintained at a relatively constant amplitude even if the signal itself varies greatly with time. Another example is compensation for channel characteristics. We may find that the dynamic range of a signal is too great to fit within the dynamic range of a channel due to the presence of low-level noise or high-level distortion. In this case we would like to adjust automatically the level of the input signal so that it stays within the allowable dynamic range. This sort of automatic level adjustment is known as an automatic gain control (AGC), a dynamic range compressor/expander, or as a signal limiter. -

Loop Stability Compensation Technique for Continuous-Time Common-Mode Feedback Circuits

Loop Stability Compensation Technique for Continuous-Time Common-Mode Feedback Circuits Young-Kyun Cho and Bong Hyuk Park Mobile RF Research Section, Advanced Mobile Communications Research Department Electronics and Telecommunications Research Institute (ETRI) Daejeon, Korea Email: [email protected] Abstract—A loop stability compensation technique for continuous-time common-mode feedback (CMFB) circuits is presented. A Miller capacitor and nulling resistor in the compensation network provide a reliable and stable operation of the fully-differential operational amplifier without any performance degradation. The amplifier is designed in a 130 nm CMOS technology, achieves simulated performance of 57 dB open loop DC gain, 1.3-GHz unity-gain frequency and 65° phase margin. Also, the loop gain, bandwidth and phase margin of the CMFB are 51 dB, 27 MHz, and 76°, respectively. Keywords-common-mode feedback, loop stability compensation, continuous-time system, Miller compensation. Fig. 1. Loop stability compensation technique for CMFB circuit. I. INTRODUCTION common-mode signal to the opamp. In Fig. 1, two poles are The differential output amplifiers usually contain common- newly generated from the CMFB loop. A dominant pole is mode feedback (CMFB) circuitry [1, 2]. A CMFB circuit is a introduced at the opamp output and the second pole is located network sensing the common-mode voltage, comparing it with at the VCMFB node. Typically, the location of these poles are a proper reference, and feeding back the correct common-mode very close which deteriorates the loop phase margin (PM) and signal with the purpose to cancel the output common-mode makes the closed loop system unstable. -

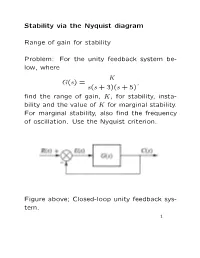

Stability Via the Nyquist Diagram Range of Gain for Stability Problem

Stability via the Nyquist diagram Range of gain for stability Problem: For the unity feedback system be- low, where K G(s)= , s(s + 3)(s + 5) find the range of gain, K, for stability, insta- bility and the value of K for marginal stability. For marginal stability, also find the frequency of oscillation. Use the Nyquist criterion. Figure above; Closed-loop unity feedback sys- tem. 1 Solution: K G(jω)= s jω s(s + 3)(s + 5)| → 8Kω j K(15 ω2) = − − · − 64ω3 + ω(15 ω2)2 − When K = 1, 8ω j (15 ω2) G(jω)= − − · − 64ω3 + ω(15 ω2)2 − Important points: Starting point: ω = 0, G(jω)= 0.0356 j − − ∞ Ending point: ω = , G(jω) = 0 270 ∞ 6 − ◦ Real axis crossing: found by setting the imag- inary part of G(jω) as zero, K ω = √15, , j0 {−120 } 2 When K = 1, P = 0, from the Nyquist plot, N is zero, so the system is stable. The real axis crossing K does not encircle [ 1, j0)] −120 − until K = 120. At that point, the system is marginally stable, and the frequency of oscilla- tion is ω = √15 rad/s. Nyquist Diagram Nyquist Diagram 0.05 2 0.04 0.03 1.5 0.02 System: G 1 Real: −0.00824 0.01 Imag: 1e−005 Frequency (rad/sec): −3.91 0.5 0 0 Imaginary Axis −0.01 Imaginary Axis −0.5 −0.02 −1 −0.03 −0.04 −1.5 −0.05 −2 −0.1 −0.08 −0.06 −0.04 −0.02 0 0.02 0.04 0.06 0.08 0.1 −3 −2.5 −2 −1.5 −1 −0.5 0 Real Axis Real Axis (a) (b) Figure above; Nyquist plots of ( )= K ; G s s(s+3)(s+5) (a) K = 1; (b)K = 120.