K0000384-PCIE-Host-Adapter-Card

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Rocketraid 2224 SATAII Host Adapter User's Guide

RocketRAID 2224 SATAII Host Adapter User’s Guide Revision: 1.0 Date: August 2005 HighPoint Technologies, Inc. HighPoint Technologies, Inc. Copyright Copyright © 2005 HighPoint Technologies, Inc. This document contains materials protected by International Copyright Laws. All rights reserved. No part of this manual may be reproduced, transmitted or transcribed in any form and for any purpose without the express written permission of HighPoint Technologies, Inc. Trademarks Companies and products mentioned in this manual are for identification purpose only. Product names or brand names appearing in this manual may or may not be registered trademarks or copyrights of their respective owners. Backup your important data before using HighPoint's products and use at your own risk. In no event shall HighPoint be liable for any loss of profits, or for direct, indirect, special, incidental or consequential damages arising from any defect or error in HighPoint's products or manuals. Information in this manual is subject to change without notice and does not represent a commitment on the part of HighPoint. Notice Reasonable effort has been made to ensure that the information in this manual is accurate. HighPoint assumes no liability for technical inaccuracies, typographical, or other errors contained herein. ii HighPoint Technologies, Inc. Table of Contents ABOUT THIS GUIDE ............................................................................................................ 1 INTRODUCING THE ROCKETRAID 2224 HOST ADAPTER............................... -

PPC7A10 at Our Website: Click HERE Powerx Product Manual PPC7A

Full-service, independent repair center -~ ARTISAN® with experienced engineers and technicians on staff. TECHNOLOGY GROUP ~I We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins. Custom engineering Your definitive source so your equipment works exactly as you specify. for quality pre-owned • Critical and expedited services • Leasing / Rentals/ Demos equipment. • In stock/ Ready-to-ship • !TAR-certified secure asset solutions Expert team I Trust guarantee I 100% satisfaction Artisan Technology Group (217) 352-9330 | [email protected] | artisantg.com All trademarks, brand names, and brands appearing herein are the property o f their respective owners. Find the Abaco Systems / Radstone PPC7A10 at our website: Click HERE PowerX Product Manual PPC7A Appendix C - PPC7A This appendix contains hardware information for PPC7A boards. The information contained in this document must be used in conjunction with PowerX Quick Start, PowerX User Guides and/or the PowerX product Manual. Link Settings...................................................................................................................................... C-3 Default Link Settings............................................................................................................................... C-3 RTC Standby Supply Voltage Link (E1)................................................................................................. C-4 FLASH Write Enable Links (E3 and E9)............................................................................................... -

A Not So Short Introduction to Pcie

Practical introduction to PCI Express with FPGAs Michal HUSEJKO, John EVANS [email protected] IT-PES-ES v 1.0 Agenda • What is PCIe ? o System Level View o PCIe data transfer protocol • PCIe system architecture • PCIe with FPGAs o Hard IP with Altera/Xilinx FPGAs o Soft IP (PLDA) o External PCIe PHY (Gennum) v 1.0 System Level View • Interconnection • Top-down tree hierarchy • PCI/PCIe configuration space • Protocol v 1.0 Interconnection • Serial interconnection • Dual uni-directional • Lane, Link, Port • Scalable o Gen1 2.5/ Gen2 5.0/ Gen3 8.0 GT/s o Number of lanes in FPGAs: x1, x2, x4, x8 • Gen1/2 8b10b • Gen3 128b/130b v 1.0 Image taken from “Introduction to PCI Express” Tree hierarchy • Top-down tree hierarchy with single host • 3 types of devices: Root Complex, Endpoint, Switch • Point-to-point connection between devices without sideband signalling • 2 types of ports: downstream/upstream • Configuration space Image taken from “Introduction to PCI Express” v 1.0 PCIe Configuration space • Similar to PCI conf space – binary compatible for first 256 bytes • Defines device(system) capabilities • Clearly identifies device in the system o Device ID o Vendor ID o Function ID o All above • and defines memory space allocated to device. v 1.0 PCIe transfer protocol • Transaction categories • Protocol • Implementation of the protocol v 1.0 Transaction categories • Configuration – move downstream • Memory – address based routing • IO – address based routing • Message – ID based routing v 1.0 Transaction Types v 1.0 Table taken from “PCI -

HP A5150A PCI Dual Port Ultra2 SCSI Host Bus Adapter

HP A5150A PCI Dual Port Ultra2 SCSI Host Bus Adapter Service and User Guide Edition 2 Customer Order Number: A5150-90001 Manufacturing Part Number: A5150-96002 E0201 U.S.A. © Copyright 2001, Hewlett-Packard Company. Legal Notices The information in this document is subject to change without notice. Hewlett-Packard makes no warranty of any kind with regard to this manual, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Hewlett-Packard shall not be held liable for errors contained herein or direct, indirect, special, incidental or consequential damages in connection with the furnishing, performance, or use of this material. Warranty. A copy of the specific warranty terms applicable to your Hewlett-Packard product and replacement parts can be obtained from your local Sales and Service Office. Restricted Rights Legend. Use, duplication or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 for DOD agencies, and subparagraphs (c) (1) and (c) (2) of the Commercial Computer Software Restricted Rights clause at FAR 52.227-19 for other agencies. HEWLETT-PACKARD COMPANY 3000 Hanover Street Palo Alto, California 94304 U.S.A. Use of this manual and flexible disk(s) or tape cartridge(s) supplied for this pack is restricted to this product only. Additional copies of the programs may be made for security and back-up purposes only. Resale of the programs in their present form or with alterations, is expressly prohibited. -

Sun Storedge PCI/PCI-X Dual Ultra320 SCSI Host Adapter Installation Guide • January 2007 Preface

Sun StorEdge™ PCI/PCI-X Dual Ultra320 SCSI Host Adapter Installation Guide Sun Microsystems, Inc. www.sun.com Part No. 817-5827-13 January 2007, Revision A Submit comments about this document at: http://www.sun.com/hwdocs/feedback Copyright 2007 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved. Sun Microsystems, Inc. has intellectual property rights relating to technology that is described in this document. In particular, and without limitation, these intellectual property rights may include one or more of the U.S. patents listed at http://www.sun.com/patents and one or more additional patents or pending patent applications in the U.S. and in other countries. This document and the product to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of the product or of this document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers. Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and in other countries, exclusively licensed through X/Open Company, Ltd. Sun, Sun Microsystems, the Sun logo, AnswerBook2, docs.sun.com, Sun StorEdge, SunVTS, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and in other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. -

Hypertransport?

HT.book Page 99 Monday, January 13, 2003 12:12 PM 5 Flow Control The Previous Chapter The previous chapter described the use of HyperTransport control and data packets to construct HyperTransport link transactions. Control packet types include Information, Request, and Response variants; data packets contain a payload of 0-64 valid bytes. The transmission, structure, and use of each packet type is presented. This Chapter This chapter describes HyperTransport flow control, used to throttle the move- ment of packets across each link interface. On a high-performance connection such as HyperTransport, efficient management of transaction flow is nearly as important as the raw bandwidth made possible by clock speed and data bus width. Topics covered here include background information on bus flow control and the initialization and use of the HyperTransport virtual channel flow con- trol buffer mechanism defined for each transmitter-receiver pair. The Next Chapter The next chapter describes the rules governing acceptance, forwarding, and rejection of packets seen by HyperTransport devices. Several factors come into play in routing, including the packet type, the direction it is moving, and the device type which sees it. A related topic also covered in this chapter is the fair- ness algorithm used by a tunnel device as it inserts its own packets into the traf- fic it forwards upstream on behalf of devices below it. The HyperTransport specification provides a fairness algorithm and a hardware method for tunnel management packet insertion. The Problem On any bus where an agent initiates the exchange of information (commands, data, status, etc.) with a target, a number of things can cause a delay (or even end) the normal completion of the intended transfer. -

Comparison of High Performance Northbridge Architectures in Multiprocessor Servers

Comparison of High Performance Northbridge Architectures in Multiprocessor Servers Michael Koontz MS CpE Scholarly Paper Advisor: Dr. Jens-Peter Kaps Co-Advisor: Dr. Daniel Tabak - 1 - Table of Contents 1. Introduction ...............................................................................................................3 2. The x86-64 Instruction Set Architecture (ISA) ...................................................... 3 3. Memory Coherency ...................................................................................................4 4. The MOESI and MESI Cache Coherency Models.................................................8 5. Scalable Coherent Interface (SCI) and HyperTransport ....................................14 6. Fully-Buffered DIMMS ..........................................................................................16 7. The AMD Opteron Northbridge ............................................................................19 8. The Intel Blackford Northbridge Architecture .................................................... 27 9. Performance and Power Consumption .................................................................32 10. Additional Considerations ..................................................................................34 11. Conclusion ............................................................................................................ 36 - 2 - 1. Introduction With the continuing growth of today’s multi-media, Internet based culture, businesses are becoming more dependent -

TMS320C6452 DSP Host Port Interface (HPI)

TMS320C6452 DSP Host Port Interface (HPI) User's Guide Literature Number: SPRUF87A October 2007–Revised May 2008 2 SPRUF87A–October 2007–Revised May 2008 Submit Documentation Feedback Contents Preface ........................................................................................................................................ 6 1 Introduction......................................................................................................................... 9 1.1 Purpose of the Peripheral................................................................................................ 9 1.2 Features .................................................................................................................... 9 1.3 Functional Block Diagram .............................................................................................. 10 1.4 Industry Standard(s) Compliance Statement ........................................................................ 11 1.5 Terminology Used in This Document ................................................................................. 11 2 Peripheral Architecture ....................................................................................................... 12 2.1 Clock Control............................................................................................................. 12 2.2 Memory Map ............................................................................................................ 12 2.3 Signal Descriptions ..................................................................................................... -

1 Signal Definitions

PI7C8140A 2-Port PCI-to-PCI Bridge REVISION 1.01 3545 North First Street, San Jose, CA 95134 Telephone: 1-877-PERICOM, (1-877-737-4266) Fax: 408-435-1100 Internet: http://www.pericom.com 07-0067 PI7C8140A 2-PORT PCI-TO-PCI BRIDGE LIFE SUPPORT POLICY Pericom Semiconductor Corporation’s products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of PSC. 1) Life support devices or system are devices or systems which: a) Are intended for surgical implant into the body or b) Support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 2) A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Pericom Semiconductor Corporation reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom Semiconductor does not assume any responsibility for use of any circuitry described other than the circuitry embodied in a Pericom Semiconductor product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. -

Upgrading and Repairing Pcs, 21St Edition Editor-In-Chief Greg Wiegand Copyright © 2013 by Pearson Education, Inc

Contents at a Glance Introduction 1 1 Development of the PC 5 2 PC Components, Features, and System Design 19 3 Processor Types and Specifications 29 4 Motherboards and Buses 155 5 BIOS 263 UPGRADING 6 Memory 325 7 The ATA/IDE Interface 377 AND 8 Magnetic Storage Principles 439 9 Hard Disk Storage 461 REPAIRING PCs 10 Flash and Removable Storage 507 21st Edition 11 Optical Storage 525 12 Video Hardware 609 13 Audio Hardware 679 14 External I/O Interfaces 703 15 Input Devices 739 16 Internet Connectivity 775 17 Local Area Networking 799 18 Power Supplies 845 19 Building or Upgrading Systems 929 20 PC Diagnostics, Testing, and Maintenance 975 Index 1035 Scott Mueller 800 East 96th Street, Indianapolis, Indiana 46240 Upgrading.indb i 2/15/13 10:33 AM Upgrading and Repairing PCs, 21st Edition Editor-in-Chief Greg Wiegand Copyright © 2013 by Pearson Education, Inc. Acquisitions Editor All rights reserved. No part of this book shall be reproduced, stored in a retrieval Rick Kughen system, or transmitted by any means, electronic, mechanical, photocopying, Development Editor recording, or otherwise, without written permission from the publisher. No patent Todd Brakke liability is assumed with respect to the use of the information contained herein. Managing Editor Although every precaution has been taken in the preparation of this book, the Sandra Schroeder publisher and author assume no responsibility for errors or omissions. Nor is any Project Editor liability assumed for damages resulting from the use of the information contained Mandie Frank herein. Copy Editor ISBN-13: 978-0-7897-5000-6 Sheri Cain ISBN-10: 0-7897-5000-7 Indexer Library of Congress Cataloging-in-Publication Data in on file. -

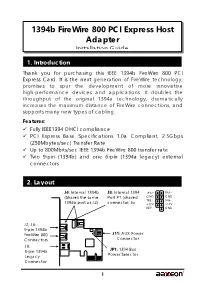

1394B Firewire 800 PCI Express Host Adapter Installation Guide

1394b FireWire 800 PCI Express Host Adapter Installation Guide 1. Introduction Thank you for purchasing this IEEE 1394b FireWire 800 PCI Express Card. It is the next generation of FireWire technology, promises to spur the development of more innovative high-performance devices and applications. It doubles the throughput of the original 1394a technology, dramatically increases the maximum distance of FireWire connections, and supports many new types of cabling. Features: 9 Fully IEEE1394 OHCI compliance 9 PCI Express Base Specifications 1.0a Compliant, 2.5Gbps (250Mbytes/sec) Transfer Rate 9 Up to 800Mbits/sec IEEE 1394b FireWire 800 transfer rate 9 Two 9-pin (1394b) and one 6-pin (1394a legacy) external connectors 2. Layout J4: Internal 1394b J8: Internal 1394 TPA+ TPA- (Shares the same Port #1 (shared GND GND TPB+ TPB- 1394b port as J2) connector, to +12V +12V KEY GND J2, J6: 9-pin 1394b FireWire 800 J11: AUX Power Connectors Connector J9: JP1: 1394 Bus 6-pin 1394a Power Selector Legacy Connector 1 IEEE 1394b FireWire 800 PCI Host Adapter JP1: IEEE1394 Bus Power Selector Settings Use +12V from PCI Express Slot PCIE AUX (motherboard’s PCB) for 1394 Bus (default) Power Use Auxiliary Power from J5 (in this PCIE AUX setting, please connect a power split cable from power supply to J6 of the Card) 3. Installing the IEEE 1394b PCIe Host Adapter 1. Turn the system power OFF before installation! 2. Use static electricity discharge precautions. Remove possible static discharge potential from any objects that the host adapter may come in contact with before installation. -

Tsi340 User Manual 80E3000 MA001 05 4 Contents

® IDT Tsi340™ PCI-to-PCI Bridge User Manual 80E3000_MA001_05 September 2009 6024 Silver Creek Valley Road, San Jose, California 95138 Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775 Printed in U.S.A. ©2009 Integrated Device Technology, Inc. GENERAL DISCLAIMER Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc. CODE DISCLAIMER Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICU- LAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES.