Mpeg 2.5 Layer Iii Audio Decoder with Adpcm Capability Product Preview

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Lossless Compression of Audio Data

CHAPTER 12 Lossless Compression of Audio Data ROBERT C. MAHER OVERVIEW Lossless data compression of digital audio signals is useful when it is necessary to minimize the storage space or transmission bandwidth of audio data while still maintaining archival quality. Available techniques for lossless audio compression, or lossless audio packing, generally employ an adaptive waveform predictor with a variable-rate entropy coding of the residual, such as Huffman or Golomb-Rice coding. The amount of data compression can vary considerably from one audio waveform to another, but ratios of less than 3 are typical. Several freeware, shareware, and proprietary commercial lossless audio packing programs are available. 12.1 INTRODUCTION The Internet is increasingly being used as a means to deliver audio content to end-users for en tertainment, education, and commerce. It is clearly advantageous to minimize the time required to download an audio data file and the storage capacity required to hold it. Moreover, the expec tations of end-users with regard to signal quality, number of audio channels, meta-data such as song lyrics, and similar additional features provide incentives to compress the audio data. 12.1.1 Background In the past decade there have been significant breakthroughs in audio data compression using lossy perceptual coding [1]. These techniques lower the bit rate required to represent the signal by establishing perceptual error criteria, meaning that a model of human hearing perception is Copyright 2003. Elsevier Science (USA). 255 AU rights reserved. 256 PART III / APPLICATIONS used to guide the elimination of excess bits that can be either reconstructed (redundancy in the signal) orignored (inaudible components in the signal). -

4. MPEG Layer-3 Audio Encoding

MPEG Layer-3 An introduction to MPEG Layer-3 K. Brandenburg and H. Popp Fraunhofer Institut für Integrierte Schaltungen (IIS) MPEG Layer-3, otherwise known as MP3, has generated a phenomenal interest among Internet users, or at least among those who want to download highly-compressed digital audio files at near-CD quality. This article provides an introduction to the work of the MPEG group which was, and still is, responsible for bringing this open (i.e. non-proprietary) compression standard to the forefront of Internet audio downloads. 1. Introduction The audio coding scheme MPEG Layer-3 will soon celebrate its 10th birthday, having been standardized in 1991. In its first years, the scheme was mainly used within DSP- based codecs for studio applications, allowing professionals to use ISDN phone lines as cost-effective music links with high sound quality. In 1995, MPEG Layer-3 was selected as the audio format for the digital satellite broadcasting system developed by World- Space. This was its first step into the mass market. Its second step soon followed, due to the use of the Internet for the electronic distribution of music. Here, the proliferation of audio material – coded with MPEG Layer-3 (aka MP3) – has shown an exponential growth since 1995. By early 1999, “.mp3” had become the most popular search term on the Web (according to http://www.searchterms.com). In 1998, the “MPMAN” (by Saehan Information Systems, South Korea) was the first portable MP3 player, pioneering the road for numerous other manufacturers of consumer electronics. “MP3” has been featured in many articles, mostly on the business pages of newspapers and periodicals, due to its enormous impact on the recording industry. -

The H.264 Advanced Video Coding (AVC) Standard

Whitepaper: The H.264 Advanced Video Coding (AVC) Standard What It Means to Web Camera Performance Introduction A new generation of webcams is hitting the market that makes video conferencing a more lifelike experience for users, thanks to adoption of the breakthrough H.264 standard. This white paper explains some of the key benefits of H.264 encoding and why cameras with this technology should be on the shopping list of every business. The Need for Compression Today, Internet connection rates average in the range of a few megabits per second. While VGA video requires 147 megabits per second (Mbps) of data, full high definition (HD) 1080p video requires almost one gigabit per second of data, as illustrated in Table 1. Table 1. Display Resolution Format Comparison Format Horizontal Pixels Vertical Lines Pixels Megabits per second (Mbps) QVGA 320 240 76,800 37 VGA 640 480 307,200 147 720p 1280 720 921,600 442 1080p 1920 1080 2,073,600 995 Video Compression Techniques Digital video streams, especially at high definition (HD) resolution, represent huge amounts of data. In order to achieve real-time HD resolution over typical Internet connection bandwidths, video compression is required. The amount of compression required to transmit 1080p video over a three megabits per second link is 332:1! Video compression techniques use mathematical algorithms to reduce the amount of data needed to transmit or store video. Lossless Compression Lossless compression changes how data is stored without resulting in any loss of information. Zip files are losslessly compressed so that when they are unzipped, the original files are recovered. -

Lossy Audio Compression Identification

2018 26th European Signal Processing Conference (EUSIPCO) Lossy Audio Compression Identification Bongjun Kim Zafar Rafii Northwestern University Gracenote Evanston, USA Emeryville, USA [email protected] zafar.rafi[email protected] Abstract—We propose a system which can estimate from an compression parameters from an audio signal, based on AAC, audio recording that has previously undergone lossy compression was presented in [3]. The first implementation of that work, the parameters used for the encoding, and therefore identify the based on MP3, was then proposed in [4]. The idea was to corresponding lossy coding format. The system analyzes the audio signal and searches for the compression parameters and framing search for the compression parameters and framing conditions conditions which match those used for the encoding. In particular, which match those used for the encoding, by measuring traces we propose a new metric for measuring traces of compression of compression in the audio signal, which typically correspond which is robust to variations in the audio content and a new to time-frequency coefficients quantized to zero. method for combining the estimates from multiple audio blocks The first work to investigate alterations, such as deletion, in- which can refine the results. We evaluated this system with audio excerpts from songs and movies, compressed into various coding sertion, or substitution, in audio signals which have undergone formats, using different bit rates, and captured digitally as well lossy compression, namely MP3, was presented in [5]. The as through analog transfer. Results showed that our system can idea was to measure traces of compression in the signal along identify the correct format in almost all cases, even at high bit time and detect discontinuities in the estimated framing. -

ARM MPEG-2 Audio Layer III Decoder Version 1

ARM MPEG-2 Audio Layer III Decoder Version 1 Programmer’s Guide Copyright © 1999 ARM Limited. All rights reserved. ARM DUI 0121B Copyright © 1999 ARM Limited. All rights reserved. Release Information The following changes have been made to this document. Change history Date Issue Change May 1999 A First release June 1999 B Second release, minor changes Proprietary Notice ARM, the ARM Powered logo, Thumb, and StrongARM are registered trademarks of ARM Limited. The ARM logo, AMBA, Angel, ARMulator, EmbeddedICE, ModelGen, Multi-ICE, ARM7TDMI, ARM9TDMI, TDMI, and STRONG are trademarks of ARM Limited. All other products or services mentioned herein may be trademarks of their respective owners. Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder. The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded. This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product. ii Copyright © 1999 ARM Limited. All rights reserved. ARM DUI 0121B Preface This preface introduces the ARM Moving Pictures Experts Group (MPEG)-2 Audio Layer III (MP3) Decoder. -

Methods of Sound Data Compression \226 Comparison of Different Standards

See discussions, stats, and author profiles for this publication at: https://www.researchgate.net/publication/251996736 Methods of sound data compression — Comparison of different standards Article CITATIONS READS 2 151 2 authors, including: Wojciech Zabierowski Lodz University of Technology 123 PUBLICATIONS 96 CITATIONS SEE PROFILE Some of the authors of this publication are also working on these related projects: How to biuld correct web application View project All content following this page was uploaded by Wojciech Zabierowski on 11 June 2014. The user has requested enhancement of the downloaded file. 1 Methods of sound data compression – comparison of different standards Norbert Nowak, Wojciech Zabierowski Abstract - The following article is about the methods of multimedia devices, DVD movies, digital television, data sound data compression. The technological progress has transmission, the Internet, etc. facilitated the process of recording audio on different media such as CD-Audio. The development of audio Modeling and coding data compression has significantly made our lives One's requirements decide what type of compression he easier. In recent years, much has been achieved in the applies. However, the choice between lossy or lossless field of audio and speech compression. Many standards method also depends on other factors. One of the most have been established. They are characterized by more important is the characteristics of data that will be better sound quality at lower bitrate. It allows to record compressed. For instance, the same algorithm, which the same CD-Audio formats using "lossy" or lossless effectively compresses the text may be completely useless compression algorithms in order to reduce the amount in the case of video and sound compression. -

SPIRIT MP3 Encoder

DATASHEET SPIRIT MP3 Encoder MP3, also known as MPEG-1/MPEG-2 Audio Layer 3, is a popular Benefits digital audio encoding and lossy compression format standardized by Moving Picture Experts Group (MPEG). Three layers (layer 1, 2, 3) • Highly optimized code are supported based on the complexity, compression and quality. • Ideal for resource constrained Layer 3 offers the highest compression for a given audio fidelity. applications MPEG-2 Audio standard extends MPEG-1 standard with: • Easy integration and fast time to market • forward and backwards compatible coding of multichannel signals • Industry-leading encoding quality • support for 16, 22.05 and 24 kHz sampling frequencies. • Low CPU usage for longest battery life SPIRIT MP3 Encoder supports MPEG 1, 2 Audio Layer III standards and their low bit rate extension MPEG 2.5. It can be effectively used in such applications as portable audio systems, wireless Key Features communications, car audio systems, set-top boxes, Internet • Full MPEG compliance appliances and PDAs. • High accuracy • Only 20 MHz* CPU load Perceptual Model Noise Control Loop • Small memory footprint • Simple API Scale Factors Filter Joint Bank Stereo Coding PCM Bitstream Quantizer Loop Applications Control • Audio streaming/Digital radio Huffman Coding • Set-top boxes • Mobile phones Control Bitstream Multiplex Data • Portable media players MP3 Bitstream • Internet appliances • Car electronics Features Availability • Low CPU load (as little as 20 MHz peak load) • ARM9E Now • Low memory requirements • Cortex-M3 Now • Highest objective encoding quality scores • Blackfin Now • MPEG 1 / 2 / 2.5 LAYER III, compliant to ISO MPEG standards • AudioDE Now • Supports bitrates from 8 Kb/s up to 320 Kb/s • Tensilica HiFi2 Now • 1- or 2-channel modes are supported • TI OMAP3 Call • TI C6xx Call Specifications • TI C5xx Call The MP3 (MPEG layer 3) audio encoder supports ISO/IEC 11172-3 • MIPS Call MPEG-1 and ISO/IEC 13818-3 MPEG-2 formats, Layer 3, VBR and Free-Format streams, mono or stereo output streams as well as MPEG-2.5 low bit rate extension. -

Creating Content for Ipod + Itunes

Apple Education Creating Content for iPod + iTunes This guide provides information about the file formats you can use when creating content compatible with iTunes and iPod. This guide also covers using and editing metadata. To prepare for creating content, you should know a few basics about file formats and metadata. Knowing about file formats will guide you in choosing the correct format for your material based on your needs and the content. Knowing how to use metadata will help you provide your audience with information about your content. In addition, metadata makes browsing and searching easier. This guide also includes recommended tools for creating content. Understanding File Formats To create and distribute materials for playback on iPod and in iTunes, you need to get the materials (primarily audio or video) into compatible file formats. Understanding file formats and how they compare with each other will help you decide the best way to prepare your materials. Apple recommends using the following file formats for iPod and iTunes content: • AAC (Advanced Audio Coding) for audio content AAC is a state-of-the-art, open (not proprietary) format. It is the audio format of choice for Internet, wireless, and digital broadcast arenas. AAC provides audio encoding that compresses much more efficiently than older formats, yet delivers quality rivaling that of uncompressed CD audio. • H.264 for video content H.264 uses the latest innovations in video compression technology to provide incredible video quality from the smallest amount of video data. This means you see crisp, clear video in much smaller files, saving you bandwidth and storage costs over previous generations of video codecs. -

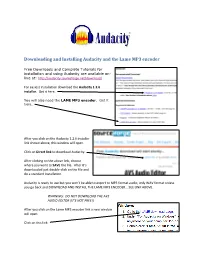

Downloading and Installing Audacity and the Lame MP3 Encoder

Downloading and Installing Audacity and the Lame MP3 encoder Free Downloads and Complete Tutorials for installation and using Audacity are available on- line at: http://audacity.sourceforge.net/download/ For easiest installation download the Audacity 1.2.6 installer. Get it here. You will also need the LAME MP3 encoder. Get it here. After you click on the Audacity 1.2.6 installer link shown above, this window will open. Click on Direct link to download Audacity. After clicking on the above link, choose where you want to SAVE the file. After it’s downloaded just double-click on the file and do a standard installation. Audacity is ready to use but you won’t be able to export to MP3 format audio, only WAV format unless you go back and DOWNLOAD AND INSTALL THE LAME MP3 ENCODER… SEE LINK ABOVE. WARNING: DO NOT DOWNLOAD THE AVS AUDIO EDITOR (IT’S NOT FREE!) After you click on the Lame MP3 encoder link a new window will open. Click on this link. In the window that opens, choose this link Then choose SAVE and save it to the desktop This is what the downloaded Lame MP3 encoder installer will look like on your desktop. Double-click it to install. Let it install the encoder to the default location, C:\Program Files\Lame for Audacity as shown on the right. When you’re done editing your AUDACITY PROJECT, you have to EXPORT it as an MP3 audio file. Choose File > Export As MP3 as shown on the left. Name your file. The save as type will be MP3 files (*.mp3) When you click Save this window will open. -

DVP5960/12 Philips DVD Player with Video Upscaling up to 1080I

Philips DVD player with Video Upscaling up to 1080i HDMI DivX playback DVP5960 Turn up your experience With high definition JPEG playback Be impressed with this Philips DVD player with HDMI digital video and audio connection. Step into another home entertainment arena as you immerse yourself with High Definition video (720p / 1080i). Unrivalled video performance • HDMI digital output for easy connection with only one cable • Video Upscaling for improved resolution of up to 1080i • High definition JPEG playback for images in true resolution Enrich your movie experience • Progressive Scan component video for optimized image quality Play it all • Movies: DVD, DVD+R/RW, DVD-R/RW, (S)VCD, DivX • DivX Ultra Certified for enhanced playback of DivX videos • Music: CD, MP3-CD, CD-R/RW & Windows Media™ Audio • Picture CD (JPEG) with music (MP3) playback Fits everywhere, goes anywhere • Ultra-slim design DVD player DVP5960/12 HDMI DivX playback Highlights HDMI for simple AV connection friends and family in the comfort of your living RW, and DVD recordable discs. DivX Ultra HDMI stands for High Definition Multimedia room. combines DivX playback with great features Interface. It is a direct digital connection that like integrated subtitles, multiple audio can carry digital HD video as well as digital Progressive Scan languages, multiple tracks and menus into one multichannel audio. By eliminating the Progressive Scan doubles the vertical convenient file format. conversion to analog signals it delivers perfect resolution of the image resulting in a noticeably picture and sound quality, completely free sharper picture. Instead of sending a field Music: Windows Media™ Audio from noise. -

Audio Decoding on the C54X

Audio Decoding on the C54X Alec Robinson, Chuck Lueck, Jon Rowlands AbstractFueled by the excitement over music distribution on the Internet, audio decompression has become a popular topic. There are several different algorithms available, which makes the programmable DSP a nice choice for systems supporting multiple formats. This paper discusses our efforts in porting two audio compression algorithms, MPEG-1 Layer 3 (MP3) and MPEG-2 Advanced Audio Coding (AAC), to the fixed-point C54X DSP. Introduction Within the last year, the popularity of downloadable, compressed audio formats via the internet has skyrocketed. This paper discusses our efforts in porting the decoders of two such compressed audio formats, MPEG-1 Layer 3 (MP3) and MPEG-2 Advanced Audio Coding (AAC), to the C54X fixed-point DSP. MPEG-1 Layer 3 is currently perhaps the most popular compressed audio format, while MPEG-2 AAC offers better audio quality at the same compression ratios. Platform Description The target processor for development was the C54X, TI’s low-power, 16-bit fixed-point DSP. Our initial design goal was to have both decoders running on the C5410 processor, which has 64 kwords of RAM available and up to 100 MIPS of computation power, while our ultimate goal is to get the same functionality running on the C5409, which has 32 kwords of RAM along with a 16 kword ROM for holding tables, constants, etc. For code development, we made significant use of the Spectrum Digital C54X EVM. With this, it was possible to profile the software, perform functional and diagnostic testing on the C54X, etc. -

Lecture #2 – Digital Audio Basics

CSC 170 – Introduction to Computers and Their Applications Lecture #2 – Digital Audio Basics Digital Audio Basics • Digital audio is music, speech, and other sounds represented in binary format for use in digital devices. • Most digital devices have a built-in microphone and audio software, so recording external sounds is easy. 1 Digital Audio Basics • To digitally record sound, samples of a sound wave are collected at periodic intervals and stored as numeric data in an audio file. • Sound waves are sampled many times per second by an analog-to-digital converter . • A digital-to-analog converter transforms the digital bits into analog sound waves. Digital Audio Basics 2 Digital Audio Basics • Sampling rate refers to the number of times per second that a sound is measured during the recording process. • Higher sampling rates increase the quality of the recording but require more storage space. Digital Audio File Formats • A digital file can be identified by its type or its file extension, such as Thriller.mp3 (an audio file). • The most popular digital audio formats are: AAC, MP3, Ogg, Vorbis, WAV, FLAC, and WMA . 3 Digital Audio File Formats AUDIO FORMAT EXTENSION ADVANTAGES DISADVANTAGES AAC (Advanced Audio .aac, .m4p, or .mp4 Very good sound quality Files can be copy protected Coding) based on MPEG-4; lossy so that use is limited to compression; used for approved devices iTunes music MP3 (also called MPEG-1 .mp3 Good sound quality; lossy Might require a standalone Layer 3) compression; can be player or browser plugin streamed over the