Modern Vlsi Analogue Filter Design: Methodology and Software Development

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Active Control of Loudspeakers: an Investigation of Practical Applications

Downloaded from orbit.dtu.dk on: Dec 18, 2017 Active control of loudspeakers: An investigation of practical applications Bright, Andrew Paddock; Jacobsen, Finn; Polack, Jean-Dominique; Rasmussen, Karsten Bo Publication date: 2002 Document Version Early version, also known as pre-print Link back to DTU Orbit Citation (APA): Bright, A. P., Jacobsen, F., Polack, J-D., & Rasmussen, K. B. (2002). Active control of loudspeakers: An investigation of practical applications. General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study or research. • You may not further distribute the material or use it for any profit-making activity or commercial gain • You may freely distribute the URL identifying the publication in the public portal If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim. Active Control of Loudspeakers: An Investigation of Practical Applications Andrew Bright Ørsted·DTU – Acoustic Technology Technical University of Denmark Published by: Ørsted·DTU, Acoustic Technology, Technical University of Denmark, Building 352, DK-2800 Kgs. Lyngby, Denmark, 2002 3 This work is dedicated to the memory of Betty Taliaferro Lawton Paddock Hunt (1916-1999) and to Samuel Raymond Bright, Jr. (1936-2001) 4 5 Table of Contents Preface 9 Summary 11 Resumé 13 Conventions, notation, and abbreviations 15 Conventions...................................................................................................................................... -

LABORATORY 3: Transient Circuits, RC, RL Step Responses, 2Nd Order Circuits

Alpha Laboratories ECSE-2010 LABORATORY 3: Transient circuits, RC, RL step responses, 2nd Order Circuits Note: If your partner is no longer in the class, please talk to the instructor. Material covered: RC circuits Integrators Differentiators 1st order RC, RL Circuits 2nd order RLC series, parallel circuits Thevenin circuits Part A: Transient Circuits RC Time constants: A time constant is the time it takes a circuit characteristic (Voltage for example) to change from one state to another state. In a simple RC circuit where the resistor and capacitor are in series, the RC time constant is defined as the time it takes the voltage across a capacitor to reach 63.2% of its final value when charging (or 36.8% of its initial value when discharging). It is assume a step function (Heavyside function) is applied as the source. The time constant is defined by the equation τ = RC where τ is the time constant in seconds R is the resistance in Ohms C is the capacitance in Farads The following figure illustrates the time constant for a square pulse when the capacitor is charging and discharging during the appropriate parts of the input signal. You will see a similar plot in the lab. Note the charge (63.2%) and discharge voltages (36.8%) after one time constant, respectively. Written by J. Braunstein Modified by S. Sawyer Spring 2020: 1/26/2020 Rensselaer Polytechnic Institute Troy, New York, USA 1 Alpha Laboratories ECSE-2010 Written by J. Braunstein Modified by S. Sawyer Spring 2020: 1/26/2020 Rensselaer Polytechnic Institute Troy, New York, USA 2 Alpha Laboratories ECSE-2010 Discovery Board: For most of the remaining class, you will want to compare input and output voltage time varying signals. -

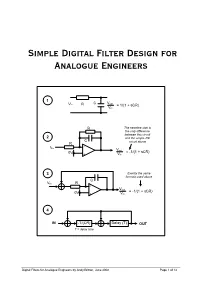

Simple Simple Digital Filter Design for Analogue Engineers

Simple Digital Filter Design for Analogue Engineers 1 C Vout Vin R = 1/(1 + sCR) Vin R The negative sign is the only difference between this circuit 2 and the simple RC C R circuit above - Vin Vout 0V = -1/(1 + sCR) + Vin 3 Exactly the same formula used above C Vin R - Vout 0V = -1/(1 + sCR) + Vin 4 IN -T/(CR) Delay (T) OUT T = delay time Digital Filters for Analogue Engineers by Andy Britton, June 2008 Page 1 of 14 Introduction If I’d read this document years ago it would have saved me countless hours of agony and confusion understanding what should be conceptually very simple. My biggest discontent with topical literature is that they never cleanly relate digital filters to “real world” analogue filters. This article/document sets out to: - • Describe the function of a very basic RC low pass analogue filter • Convert this filter to an analogue circuit that is digitally realizable • Explain how analogue functions are converted to digital functions • Develop a basic 1st order digital low-pass filter • Develop a 2nd order filter with independent Q and frequency control parameters • Show how digital filters can be proven/designed using a spreadsheet such as excel • Demonstrate digital filters by showing excel graphs of signals • Explain the limitations of use of digital filters i.e. when they become unstable • Show how these filters fit in to the general theory (yawn!) Before the end of this article you should hopefully find something useful to guide you on future designs and allow you to successfully implement a digital filter. -

Simulating the Directivity Behavior of Loudspeakers with Crossover Filters

Audio Engineering Society Convention Paper Presented at the 123rd Convention 2007 October 5–8 New York, NY, USA The papers at this Convention have been selected on the basis of a submitted abstract and extended precis that have been peer reviewed by at least two qualified anonymous reviewers. This convention paper has been reproduced from the author's advance manuscript, without editing, corrections, or consideration by the Review Board. The AES takes no responsibility for the contents. Additional papers may be obtained by sending request and remittance to Audio Engineering Society, 60 East 42nd Street, New York, New York 10165-2520, USA; also see www.aes.org. All rights reserved. Reproduction of this paper, or any portion thereof, is not permitted without direct permission from the Journal of the Audio Engineering Society. Simulating the Directivity Behavior of Loudspeakers with Crossover Filters Stefan Feistel1, Wolfgang Ahnert2, and Charles Hughes3, and Bruce Olson4 1 Ahnert Feistel Media Group, Arkonastr.45-49, 13189 Berlin, Germany [email protected] 2 Ahnert Feistel Media Group, Arkonastr.45-49, 13189 Berlin, Germany [email protected] 3 Excelsior Audio Design & Services, LLC, Gastonia, NC, USA [email protected] 4 Olson Sound Design, Brooklyn Park, MN, USA [email protected] ABSTRACT In previous publications the description of loudspeakers was introduced based on high-resolution data, comprising most importantly of complex directivity data for individual drivers as well as of crossover filters. In this work it is presented how this concept can be exploited to predict the directivity balloon of multi-way loudspeakers depending on the chosen crossover filters. -

Framsida Msc Thesis Viktor Gunnarsson

Assessment of Nonlinearities in Loudspeakers Volume dependent equalization Master’s Thesis in the Master’s programme in Sound and Vibration VIKTOR GUNNARSSON Department of Civil and Environmental Engineering Division of Applied Acoustics Chalmers Room Acoustics Group CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2010 Master’s Thesis 2010:27 MASTER’S THESIS 2010:27 Assessment of Nonlinearities in Loudspeakers Volume dependent equalization VIKTOR GUNNARSSON Department of Civil and Environmental Engineering Division of Applied Acoustics Roomacoustics Group CHALMERS UNIVERSITY OF TECHNOLOGY Goteborg,¨ Sweden 2010 CHALMERS, Master’s Thesis 2010:27 ii Assessment of Nonlinearities in Loudspeakers Volume dependent equalization © VIKTOR GUNNARSSON, 2010 Master’s Thesis 2010:27 Department of Civil and Environmental Engineering Division of Applied Acoustics Roomacoustics Group Chalmers University of Technology SE-41296 Goteborg¨ Sweden Tel. +46-(0)31 772 1000 Reproservice / Department of Civil and Environmental Engineering Goteborg,¨ Sweden 2010 Assessment of Nonlinearities in Loudspeakers Volume dependent equalization Master’s Thesis in the Master’s programme in Sound and Vibration VIKTOR GUNNARSSON Department of Civil and Environmental Engineering Division of Applied Acoustics Roomacoustics Group Chalmers University of Technology Abstract Digital room correction of loudspeakers has become popular over the latest years, yield- ing great gains in sound quality in applications ranging from home cinemas and cars to audiophile HiFi-systems. However, -

Classic Filters There Are 4 Classic Analogue Filter Types: Butterworth, Chebyshev, Elliptic and Bessel. There Is No Ideal Filter

Classic Filters There are 4 classic analogue filter types: Butterworth, Chebyshev, Elliptic and Bessel. There is no ideal filter; each filter is good in some areas but poor in others. • Butterworth: Flattest pass-band but a poor roll-off rate. • Chebyshev: Some pass-band ripple but a better (steeper) roll-off rate. • Elliptic: Some pass- and stop-band ripple but with the steepest roll-off rate. • Bessel: Worst roll-off rate of all four filters but the best phase response. Filters with a poor phase response will react poorly to a change in signal level. Butterworth The first, and probably best-known filter approximation is the Butterworth or maximally-flat response. It exhibits a nearly flat passband with no ripple. The rolloff is smooth and monotonic, with a low-pass or high- pass rolloff rate of 20 dB/decade (6 dB/octave) for every pole. Thus, a 5th-order Butterworth low-pass filter would have an attenuation rate of 100 dB for every factor of ten increase in frequency beyond the cutoff frequency. It has a reasonably good phase response. Figure 1 Butterworth Filter Chebyshev The Chebyshev response is a mathematical strategy for achieving a faster roll-off by allowing ripple in the frequency response. As the ripple increases (bad), the roll-off becomes sharper (good). The Chebyshev response is an optimal trade-off between these two parameters. Chebyshev filters where the ripple is only allowed in the passband are called type 1 filters. Chebyshev filters that have ripple only in the stopband are called type 2 filters , but are are seldom used. -

Experiment 12: AC Circuits - RLC Circuit

Experiment 12: AC Circuits - RLC Circuit Introduction An inductor (L) is an important component of circuits, on the same level as resistors (R) and capacitors (C). The inductor is based on the principle of inductance - that moving charges create a magnetic field (the reverse is also true - a moving magnetic field creates an electric field). Inductors can be used to produce a desired magnetic field and store energy in its magnetic field, similar to capacitors being used to produce electric fields and storing energy in their electric field. At its simplest level, an inductor consists of a coil of wire in a circuit. The circuit symbol for an inductor is shown in Figure 1a. So far we observed that in an RC circuit the charge, current, and potential difference grew and decayed exponentially described by a time constant τ. If an inductor and a capacitor are connected in series in a circuit, the charge, current and potential difference do not grow/decay exponentially, but instead oscillate sinusoidally. In an ideal setting (no internal resistance) these oscillations will continue indefinitely with a period (T) and an angular frequency ! given by 1 ! = p (1) LC This is referred to as the circuit's natural angular frequency. A circuit containing a resistor, a capacitor, and an inductor is called an RLC circuit (or LCR), as shown in Figure 1b. With a resistor present, the total electromagnetic energy is no longer constant since energy is lost via Joule heating in the resistor. The oscillations of charge, current and potential are now continuously decreasing with amplitude. -

ELECTRICAL CIRCUIT ANALYSIS Lecture Notes

ELECTRICAL CIRCUIT ANALYSIS Lecture Notes (2020-21) Prepared By S.RAKESH Assistant Professor, Department of EEE Department of Electrical & Electronics Engineering Malla Reddy College of Engineering & Technology Maisammaguda, Dhullapally, Secunderabad-500100 B.Tech (EEE) R-18 MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY II Year B.Tech EEE-I Sem L T/P/D C 3 -/-/- 3 (R18A0206) ELECTRICAL CIRCUIT ANALYSIS COURSE OBJECTIVES: This course introduces the analysis of transients in electrical systems, to understand three phase circuits, to evaluate network parameters of given electrical network, to draw the locus diagrams and to know about the networkfunctions To prepare the students to have a basic knowledge in the analysis of ElectricNetworks UNIT-I D.C TRANSIENT ANALYSIS: Transient response of R-L, R-C, R-L-C circuits (Series and parallel combinations) for D.C. excitations, Initial conditions, Solution using differential equation and Laplace transform method. UNIT - II A.C TRANSIENT ANALYSIS: Transient response of R-L, R-C, R-L-C Series circuits for sinusoidal excitations, Initial conditions, Solution using differential equation and Laplace transform method. UNIT - III THREE PHASE CIRCUITS: Phase sequence, Star and delta connection, Relation between line and phase voltages and currents in balanced systems, Analysis of balanced and Unbalanced three phase circuits UNIT – IV LOCUS DIAGRAMS & RESONANCE: Series and Parallel combination of R-L, R-C and R-L-C circuits with variation of various parameters.Resonance for series and parallel circuits, concept of band width and Q factor. UNIT - V NETWORK PARAMETERS:Two port network parameters – Z,Y, ABCD and hybrid parameters.Condition for reciprocity and symmetry.Conversion of one parameter to other, Interconnection of Two port networks in series, parallel and cascaded configuration and image parameters. -

Lecture 4: RLC Circuits and Resonant Circuits

Lecture 4: R-L-C Circuits and Resonant Circuits RLC series circuit: ● What's VR? ◆ Simplest way to solve for V is to use voltage divider equation in complex notation: V R X L X C V = in R R + XC + XL L C R Vin R = Vin = V0 cosω t 1 R + + jωL jωC ◆ Using complex notation for the apply voltage V = V cosωt = Real(V e jωt ): j t in 0 0 V e ω R V = 0 R $ 1 ' € R + j& ωL − ) % ωC ( ■ We are interested in the both the magnitude of VR and its phase with respect to Vin. ■ First the magnitude: jωt V0e R € V = R $ 1 ' R + j& ωL − ) % ωC ( V R = 0 2 2 $ 1 ' R +& ωL − ) % ωC ( K.K. Gan L4: RLC and Resonance Circuits 1 € ■ The phase of VR with respect to Vin can be found by writing VR in purely polar notation. ❑ For the denominator we have: 0 * 1 -4 2 ωL − $ 1 ' 2 $ 1 ' 2 1, /2 R + j& ωL − ) = R +& ωL − ) exp1 j tan− ωC 5 % C ( % C( , R / ω ω 2 , /2 3 + .6 ❑ Define the phase angle φ : Imaginary X tanφ = Real X € 1 ωL − = ωC R ❑ We can now write for VR in complex form: V R e jωt V = o R 2 € jφ 2 % 1 ( e R +' ωL − * Depending on L, C, and ω, the phase angle can be & ωC) positive or negative! In this example, if ωL > 1/ωC, j(ωt−φ) then VR(t) lags Vin(t). = VR e ■ Finally, we can write down the solution for V by taking the real part of the above equation: j(ωt−φ) V R e V R cos(ωt −φ) V = Real 0 = 0 R 2 2 € 2 % 1 ( 2 % 1 ( R +' ωL − * R +' ωL − * & ωC ) & ωC ) K.K. -

Lecture 14 - AC Circuits, Resonance Y&F Chapter 31, Sec

Physics 121 - Electricity and Magnetism Lecture 14 - AC Circuits, Resonance Y&F Chapter 31, Sec. 3 - 8 • The Series RLC Circuit. Amplitude and Phase Relations • Phasor Diagrams for Voltage and Current • Impedance and Phasors for Impedance • Resonance • Power in AC Circuits, Power Factor • Examples • Transformers • Summaries Copyright R. Janow – Fall 2013 Current & voltage phases in pure R, C, and L circuits Current is the same everywhere in a single branch (including phase) Phases of voltages in elements are referenced to the current phasor • Apply sinusoidal voltage E (t) = EmCos(wDt) • For pure R, L, or C loads, phase angles are 0, +p/2, -p/2 • Reactance” means ratio of peak voltage to peak current (generalized resistances). VR& iR in phase VC lags iC by p/2 VL leads iL by p/2 Resistance Capacitive Reactance Inductive Reactance 1 V /i R Vmax /iC C Vmax /iL L wDL max R wDC Copyright R. Janow – Fall 2013 The impedance is the ratio of peak EMF to peak current peak applied voltage Em Z [Z] ohms peak current that flows im 2 2 2 Magnitude of Em: Em VR (VL VC) 1 Reactances: L wDL C wDC L VL /iL C VC /iC R VR /iR im iR,max iL,max iC,max For series LRC circuit, divide Em by peak current 2 2 1/2 Applies to a single Magnitude of Z: Z [ R (L C) ] branch with L, C, R VL VC L C Phase angle F: tan(F) see diagram VR R F measures the power absorbed by the circuit: P Em im Em im cos(F) • R ~ 0 tiny losses, no power absorbed im normal to Em F ~ +/- p/2 • XL=XC im parallel to Em F 0 Z=R maximum currentCopyright (resonance) R. -

AC Power • Resonant Circuits • Phasors (2-Dim Vectors, Amplitude and Phase) What Is Reactance ? You Can Think of It As a Frequency-Dependent Resistance

Physics-272 Lecture 20 • AC Power • Resonant Circuits • Phasors (2-dim vectors, amplitude and phase) What is reactance ? You can think of it as a frequency-dependent resistance. 1 For high ω, χ ~0 X = C C ωC - Capacitor looks like a wire (“short”) For low ω, χC∞ - Capacitor looks like a break For low ω, χL~0 - Inductor looks like a wire (“short”) XL = ω L For high ω, χL∞ - Inductor looks like a break (inductors resist change in current) ("XR "= R ) An RL circuit is driven by an AC generator as shown in the figure. For what driving frequency ω of the generator, will the current through the resistor be largest a) ω large b) ω small c) independent of driving freq. The current amplitude is inversely proportional to the frequency of the ω generator. (X L= L) Alternating Currents: LRC circuit Figure (b) has XL>X C and (c) has XL<X C . Using Phasors, we can construct the phasor diagram for an LRC Circuit. This is similar to 2-D vector addition. We add the phasors of the resistor, the inductor, and the capacitor. The inductor phasor is +90 and the capacitor phasor is -90 relative to the resistor phasor. Adding the three phasors vectorially, yields the voltage sum of the resistor, inductor, and capacitor, which must be the same as the voltage of the AC source. Kirchoff’s voltage law holds for AC circuits. Also V R and I are in phase. Phasors R ε ω Problem : Given Vdrive = m sin( t), C L find VR, VL, VC, IR, IL, IC ε ∼ Strategy : We will use Kirchhoff’s voltage law that the (phasor) sum of the voltages VR, VC, and VL must equal Vdrive . -

Chapter 14 Frequency Response

CHAPTER 14 FREQUENCYRESPONSE One machine can do the work of fifty ordinary men. No machine can do the work of one extraordinary man. — Elbert G. Hubbard Enhancing Your Career Career in Control Systems Control systems are another area of electrical engineering where circuit analysis is used. A control system is designed to regulate the behavior of one or more variables in some desired manner. Control systems play major roles in our everyday life. Household appliances such as heating and air-conditioning systems, switch-controlled thermostats, washers and dryers, cruise controllers in automobiles, elevators, traffic lights, manu- facturing plants, navigation systems—all utilize control sys- tems. In the aerospace field, precision guidance of space probes, the wide range of operational modes of the space shuttle, and the ability to maneuver space vehicles remotely from earth all require knowledge of control systems. In the manufacturing sector, repetitive production line opera- tions are increasingly performed by robots, which are pro- grammable control systems designed to operate for many hours without fatigue. Control engineering integrates circuit theory and communication theory. It is not limited to any specific engi- neering discipline but may involve environmental, chemical, aeronautical, mechanical, civil, and electrical engineering. For example, a typical task for a control system engineer might be to design a speed regulator for a disk drive head. A thorough understanding of control systems tech- niques is essential to the electrical engineer and is of great value for designing control systems to perform the desired task. A welding robot. (Courtesy of Shela Terry/Science Photo Library.) 583 584 PART 2 AC Circuits 14.1 INTRODUCTION In our sinusoidal circuit analysis, we have learned how to find voltages and currents in a circuit with a constant frequency source.