Here I Led Subcommittee Reports Related to Data-Intensive Science and Post-Moore Computing) and in CRA’S Board of Directors Since 2015

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Communications of the Acm

COMMUNICATIONS CACM.ACM.ORG OF THEACM 11/2014 VOL.57 NO.11 Scene Understanding by Labeling Pixels Evolution of the Product Manager The Data on Diversity On Facebook, Most Ties Are Weak Keeping Online Reviews Honest Association for Computing Machinery tvx-full-page.pdf-newest.pdf 1 11/10/2013 12:03 3-5 JUNE, 2015 BRUSSELS, BELGIUM Course and Workshop C proposals by M 15 November 2014 Y CM Paper Submissions by MY 12 January 2015 CY CMY K Work in Progress, Demos, DC, & Industrial Submissions by 2 March 2015 Welcoming Submissions on Content Production Systems & Infrastructures Devices & Interaction Techniques Experience Design & Evaluation Media Studies Data Science & Recommendations Business Models & Marketing Innovative Concepts & Media Art TVX2015.COM [email protected] ACM Books M MORGAN& CLAYPOOL &C PUBLISHERS Publish your next book in the ACM Digital Library ACM Books is a new series of advanced level books for the computer science community, published by ACM in collaboration with Morgan & Claypool Publishers. I’m pleased that ACM Books is directed by a volunteer organization headed by a dynamic, informed, energetic, visionary Editor-in-Chief (Tamer Özsu), working closely with a forward-looking publisher (Morgan and Claypool). —Richard Snodgrass, University of Arizona books.acm.org ACM Books ◆ will include books from across the entire spectrum of computer science subject matter and will appeal to computing practitioners, researchers, educators, and students. ◆ will publish graduate level texts; research monographs/overviews of established and emerging fields; practitioner-level professional books; and books devoted to the history and social impact of computing. ◆ will be quickly and attractively published as ebooks and print volumes at affordable prices, and widely distributed in both print and digital formats through booksellers and to libraries and individual ACM members via the ACM Digital Library platform. -

Bypassing Portability Pitfalls of High-Level Low-Level Programming

Bypassing Portability Pitfalls of High-level Low-level Programming Yi Lin, Stephen M. Blackburn Australian National University [email protected], [email protected] Abstract memory-safety, encapsulation, and strong abstraction over hard- Program portability is an important software engineering consider- ware [12], which are desirable goals for system programming as ation. However, when high-level languages are extended to effec- well. Thus, high-level languages are potential candidates for sys- tively implement system projects for software engineering gain and tem programming. safety, portability is compromised—high-level code for low-level Prior research has focused on the feasibility and performance of programming cannot execute on a stock runtime, and, conversely, applying high-level languages to system programming [1, 7, 10, a runtime with special support implemented will not be portable 15, 16, 21, 22, 26–28]. The results showed that, with proper ex- across different platforms. tension and restriction, high-level languages are able to undertake We explore the portability pitfall of high-level low-level pro- the task of low-level programming, while preserving type-safety, gramming in the context of virtual machine implementation tasks. memory-safety, encapsulation and abstraction. Notwithstanding the Our approach is designing a restricted high-level language called cost for dynamic compilation and garbage collection, the perfor- RJava, with a flexible restriction model and effective low-level ex- mance of high-level languages when used to implement a virtual tensions, which is suitable for different scopes of virtual machine machine is still competitive with using a low-level language [2]. implementation, and also suitable for a low-level language bypass Using high-level languages to architect large systems is bene- for improved portability. -

Techniques for Real-System Characterization of Java Virtual Machine Energy and Power Behavior Gilberto Contreras Margaret Martonosi

Techniques for Real-System Characterization of Java Virtual Machine Energy and Power Behavior Gilberto Contreras Margaret Martonosi Department of Electrical Engineering Princeton University 1 Why Study Power in Java Systems? The Java platform has been adopted in a wide variety of devices Java servers demand performance, embedded devices require low-power Performance is important, power/energy/thermal issues are equally important How do we study and characterize these requirements in a multi-layer platform? 2 Power/Performance Design Issues Java Application Java Virtual Machine Operating System Hardware 3 Power/Performance Design Issues Java Application Garbage Class Runtime Execution Collection LoaderJava VirtualCompiler MachineEngine Operating System Hardware How do the various software layers affect power/performance characteristics of hardware? Where should time be invested when designing power and/or thermally aware Java virtual Machines? 4 Outline Approaches for Energy/Performance Characterization of Java virtual machines Methodology Breaking the JVM into sub-components Hardware-based power/performance characterization of JVM sub-components Results Jikes & Kaffe on Pentium M Kaffe on Intel XScale Conclusions 5 Power & Performance Analysis of Java Simulation Approach √ Flexible: easy to model non-existent hardware x Simulators may lack comprehensiveness and accuracy x Thermal studies require tens of seconds granularity Accurate simulators are too slow Hardware Approach √ Able to capture full-system characteristics -

Curriculum Vitae

Massachusetts Institute of Technology School of Engineering Faculty Personnel Record Date: April 1, 2020 Full Name: Charles E. Leiserson Department: Electrical Engineering and Computer Science 1. Date of Birth November 10, 1953 2. Citizenship U.S.A. 3. Education School Degree Date Yale University B. S. (cum laude) May 1975 Carnegie-Mellon University Ph.D. Dec. 1981 4. Title of Thesis for Most Advanced Degree Area-Efficient VLSI Computation 5. Principal Fields of Interest Analysis of algorithms Caching Compilers and runtime systems Computer chess Computer-aided design Computer network architecture Digital hardware and computing machinery Distance education and interaction Fast artificial intelligence Leadership skills for engineering and science faculty Multicore computing Parallel algorithms, architectures, and languages Parallel and distributed computing Performance engineering Scalable computing systems Software performance engineering Supercomputing Theoretical computer science MIT School of Engineering Faculty Personnel Record — Charles E. Leiserson 2 6. Non-MIT Experience Position Date Founder, Chairman of the Board, and Chief Technology Officer, Cilk Arts, 2006 – 2009 Burlington, Massachusetts Director of System Architecture, Akamai Technologies, Cambridge, 1999 – 2001 Massachusetts Shaw Visiting Professor, National University of Singapore, Republic of 1995 – 1996 Singapore Network Architect for Connection Machine Model CM-5 Supercomputer, 1989 – 1990 Thinking Machines Programmer, Computervision Corporation, Bedford, Massachusetts 1975 -

Fedora Core, Java™ and You

Fedora Core, Java™ and You Gary Benson Software Engineer What is Java? The word ªJavaº is used to describe three things: The Java programming language The Java virtual machine The Java platform To support Java applications Fedora needs all three. What Fedora uses: GCJ and ECJ GCJ is the core of Fedora©s Java support: GCJ includes gcj, a compiler for the Java programming language. GCJ also has a runtime and class library, collectively called libgcj. The class library is separately known as GNU Classpath. ECJ is the Eclipse Compiler for Java: GCJ©s compiler gcj is not used for ªtraditionalº Java compilation. More on that later... Why libgcj? There are many free Java Virtual machines: Cacao, IKVM, JamVM, Jikes RVM, Kaffe, libgcj, Sable VM, ... There are two main reasons Fedora uses libgcj: Availability on many platforms. Ability to use precompiled native code. GNU Classpath Free core class library for Java virtual machines and compilers. The JPackage Project A collection of some 1,600 Java software packages for Linux: Distribution-agnostic RPM packages. Both runtimes/development kits and applications. Segregation between free and non-free packages. All free packages built entirely from source. Multiple runtimes/development kits may be installed. Fedora includes: JPackage-compatible runtime and development kit packages. A whole bunch of applications. JPackage JOnAS Fedora©s Java Compilers gcj can operate in several modes: Java source (.java) to Java bytecode (.class) Java source (.java) to native machine code (.o) Java bytecode (.class, .jar) to native machine code (.o) In Fedora: ECJ compiles Java source to bytecode. gcj compiles that bytecode to native machine code. -

Java in Embedded Linux Systems

Java in Embedded Linux Systems Java in Embedded Linux Systems Thomas Petazzoni / Michael Opdenacker Free Electrons http://free-electrons.com/ Created with OpenOffice.org 2.x Java in Embedded Linux Systems © Copyright 2004-2007, Free Electrons, Creative Commons Attribution-ShareAlike 2.5 license http://free-electrons.com Sep 15, 2009 1 Rights to copy Attribution ± ShareAlike 2.5 © Copyright 2004-2008 You are free Free Electrons to copy, distribute, display, and perform the work [email protected] to make derivative works to make commercial use of the work Document sources, updates and translations: Under the following conditions http://free-electrons.com/articles/java Attribution. You must give the original author credit. Corrections, suggestions, contributions and Share Alike. If you alter, transform, or build upon this work, you may distribute the resulting work only under a license translations are welcome! identical to this one. For any reuse or distribution, you must make clear to others the license terms of this work. Any of these conditions can be waived if you get permission from the copyright holder. Your fair use and other rights are in no way affected by the above. License text: http://creativecommons.org/licenses/by-sa/2.5/legalcode Java in Embedded Linux Systems © Copyright 2004-2007, Free Electrons, Creative Commons Attribution-ShareAlike 2.5 license http://free-electrons.com Sep 15, 2009 2 Best viewed with... This document is best viewed with a recent PDF reader or with OpenOffice.org itself! Take advantage of internal -

Ultra-Large-Scale Sites

Ultra-large-scale Sites <working title> – Scalability, Availability and Performance in Social Media Sites (picture from social network visualization?) Walter Kriha With a forword by << >> Walter Kriha, Scalability and Availability Aspects…, V.1.9.1 page 1 03/12/2010 Copyright <<ISBN Number, Copyright, open access>> ©2010 Walter Kriha This selection and arrangement of content is licensed under the Creative Commons Attribution License: http://creativecommons.org/licenses/by/3.0/ online: www.kriha.de/krihaorg/ ... <a rel="license" href="http://creativecommons.org/licenses/by/3.0/de/"><img alt="Creative Commons License" style="border-width:0" src="http://i.creativecommons.org/l/by/3.0/de/88x31.png" /></a><br /><span xmlns:dc="http://purl.org/dc/elements/1.1/" href="http://purl.org/dc/dcmitype/Text" property="dc:title" rel="dc:type"> Building Scalable Social Media Sites</span> by <a xmlns:cc="http://creativecommons.org/ns#" href="wwww.kriha.de/krihaorg/books/ultra.pdf" property="cc:attributionName" rel="cc:attributionURL">Walter Kriha</a> is licensed under a <a rel="license" href="http://creativecommons.org/licenses/by/3.0/de/">Creative Commons Attribution 3.0 Germany License</a>.<br />Permissions beyond the scope of this license may be available at <a xmlns:cc="http://creativecommons.org/ns#" href="www.kriha.org" rel="cc:morePermissions">www.kriha.org</a>. Walter Kriha, Scalability and Availability Aspects…, V.1.9.1 page 2 03/12/2010 Acknowledgements <<master course, Todd Hoff/highscalability.com..>> Walter Kriha, Scalability and Availability Aspects…, V.1.9.1 page 3 03/12/2010 ToDo’s - The role of ultra fast networks (Infiniband) on distributed algorithms and behaviour with respect to failure models - more on group behaviour from Clay Shirky etc. -

Optimizing Applications for Multicore by Intel Software Engineer Levent Akyil Welcome to the Parallel Universe

Letter to the Editor by parallelism author and expert James Reinders Are You Ready to Enter a Parallel Universe: Optimizing Applications for Multicore by Intel software engineer Levent Akyil Welcome to the Parallel Universe Contents Think Parallel or Perish, BY JAMES REINDERS .........................................................................................2 James Reinders, Lead Evangelist and a Director with Intel® Software Development Products, sees a future where every software developer needs to be thinking about parallelism first when programming. He first published“ Think Parallel or Perish“ three years ago. Now he revisits his comments to offer an update on where we have gone and what still lies ahead. Parallelization Methodology...................................................................................................................... 4 The four stages of parallel application development addressed by Intel® Parallel Studio. Writing Parallel Code Safely, BY PETER VARHOL ........................................................................... 5 Writing multithreaded code to take full advantage of multiple processors and multicore processors is difficult. The new Intel® Parallel Studio should help us bridge that gap. Are You Ready to Enter a Parallel Universe: Optimizing Applications for Multicore, BY LEVENT AKYIL .............................................. 8 A look at parallelization methods made possible by the new Intel® Parallel Studio—designed for Microsoft Visual Studio* C/C++ developers of Windows* applications. -

AWARDS SESSION New Orleans Convention Center New Orleans, Louisiana Tuesday, 18 November 2014

Association for Computing Machinery AWARDS SESSION New Orleans Convention Center New Orleans, Louisiana Tuesday, 18 November 2014 SC14 Awards Session will honor the following individuals for their contributions to the computing profession: Charles E. Leiserson 2014 ACM/IEEE Computer Society Ken Kennedy Award Satoshi Matsuoka 2014 IEEE Computer Society Sidney Fernbach Award Gordon Bell 2014 IEEE Computer Society Seymour Cray Computer Engineering Award The Kennedy Award is presented by ACM President Alexander L. Wolf and Computer Society President Dejan S. Milojičić. The IEEE Computer Society Seymour Cray and Sidney Fernbach Awards are presented by 2014 IEEE Computer Society President Dejan S. Milojičić. The 2014 ACM/IEEE Computer Society Ken Kennedy Award ACM/IEEE Computer Society Ken Kennedy Award The Ken Kennedy Award was established in memory of Ken Kennedy, the founder of Rice University’s nationally ranked computer science program and one of the world’s foremost experts on high-performance computing. The award consists of a certificate and a $5,000 honorarium and is awarded jointly by the ACM and the IEEE Computer Society for outstanding contributions to programmability or productivity in high-performance computing together with significant community service or mentoring contributions. http://awards.acm.org http://computer.org/awards PREVIOUS RECIPIENTS — ACM/IEEE COMPUTER SOCIETY KEN KENNEDY AWARD 2013 - Jack Dongarra 2012 - Mary Lou Soffa 2011 - Susan L. Graham 2010 - David Kuck 2009 - Francine Berman 2014 ACM/IEEE COMPUTER SOCIETY KEN KENNEDY AWARD SUBCOMMITTEE Mary Hall, University of Utah, Chair David Rosenblum, National University of Randy Allen, National Instruments Singapore Keith Cooper, Rice University Valentina Salapura, IBM Susan Graham, University of California, Berkeley* David Padua, University of Illinois at Urbana- Champaign *Previous recipient Charles E. -

Design and Analysis of a Scala Benchmark Suite for the Java Virtual Machine

Design and Analysis of a Scala Benchmark Suite for the Java Virtual Machine Entwurf und Analyse einer Scala Benchmark Suite für die Java Virtual Machine Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) genehmigte Dissertation von Diplom-Mathematiker Andreas Sewe aus Twistringen, Deutschland April 2013 — Darmstadt — D 17 Fachbereich Informatik Fachgebiet Softwaretechnik Design and Analysis of a Scala Benchmark Suite for the Java Virtual Machine Entwurf und Analyse einer Scala Benchmark Suite für die Java Virtual Machine Genehmigte Dissertation von Diplom-Mathematiker Andreas Sewe aus Twistrin- gen, Deutschland 1. Gutachten: Prof. Dr.-Ing. Ermira Mezini 2. Gutachten: Prof. Richard E. Jones Tag der Einreichung: 17. August 2012 Tag der Prüfung: 29. Oktober 2012 Darmstadt — D 17 For Bettina Academic Résumé November 2007 – October 2012 Doctoral studies at the chair of Prof. Dr.-Ing. Er- mira Mezini, Fachgebiet Softwaretechnik, Fachbereich Informatik, Techni- sche Universität Darmstadt October 2001 – October 2007 Studies in mathematics with a special focus on com- puter science (Mathematik mit Schwerpunkt Informatik) at Technische Uni- versität Darmstadt, finishing with a degree of Diplom-Mathematiker (Dipl.- Math.) iii Acknowledgements First and foremost, I would like to thank Mira Mezini, my thesis supervisor, for pro- viding me with the opportunity and freedom to pursue my research, as condensed into the thesis you now hold in your hands. Her experience and her insights did much to improve my research as did her invaluable ability to ask the right questions at the right time. I would also like to thank Richard Jones for taking the time to act as secondary reviewer of this thesis. -

Two Students Named Recipients of 2014 ACM/IEEE-CS George Michael Memorial HPC Fellowships

FOR IMMEDIATE RELEASE Contacts: Virginia Gold Margo McCall 212-626-0505 714-816-2182 [email protected] [email protected] ACM AND IEEE COMPUTER SOCIETY RECOGNIZE CHARLES E. LEISERSON FOR ADVANCES IN PARALLEL COMPUTING SYSTEMS MIT Professor Developed Cilk Multithreaded Programming Technology NEW YORK, September 12, 2014 -- Charles E. Leiserson of Massachusetts Institute of Technology (MIT) will receive the 2014 ACM-IEEE Computer Society Ken Kennedy Award for his influence on parallel computing systems and their adoption into mainstream use through scholarly research and development. He was also cited for his mentoring of computer science leaders and students. Leiserson introduced the notion of cache-oblivious algorithms, which can exploit the memory hierarchy near optimally despite having no tuning parameters for cache size or cache-line length. He also developed the Cilk multithreaded programming technology, and led the development of several Cilk-based parallel chess-playing programs which won numerous prizes in international competition. The award will be presented at the SC14 supercomputing conference on Tuesday, November 18 in New Orleans. The coauthor of “Introduction to Algorithms,” one of computer science’s most cited publications, Leiserson is also the creator of MIT undergraduate courses on algorithms and on discrete mathematics for computer science. He headed the computer science program for the pioneering Singapore-MIT Alliance distance- education program and developed MIT’s undergraduate class on software performance engineering, which teaches parallel programming as one of several techniques for writing fast code. Leiserson’s annual workshop on Leadership Skills for Engineering and Science Faculty has educated hundreds of faculty at MIT and around the world in the human issues involved in leading technical teams in academia. -

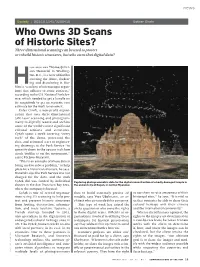

Who Owns 3D Scans of Historic Sites? Three-Dimensional Scanning Can Be Used to Protect Or Rebuild Historic Structures, but Who Owns That Digital Data?

news Society | DOI:10.1145/3290410 Esther Shein Who Owns 3D Scans of Historic Sites? Three-dimensional scanning can be used to protect or rebuild historic structures, but who owns that digital data? IGH ATOP THE Thomas Jeffer- son Memorial in Washing- ton, D.C., is a layer of biofilm covering the dome, darken- ing and discoloring it. Bio- Hfilm is “a colony of microscopic organ- isms that adheres to stone surfaces,” according to the U.S. National Park Ser- vice, which needed to get a handle on its magnitude to get an accurate cost estimate for the work to remove it. Enter CyArk, a non-profit organi- zation that uses three-dimensional (3D) laser scanning and photogram- metry to digitally record and archive some of the world’s most significant cultural artifacts and structures. CyArk spent a week covering “every inch” of the dome, processed the data, and returned a set of engineer- ing drawings to the Park Service “to quantify down to the square inch how much biofilm is on the monument,’’ says CEO John Ristevski. “This is an example of where data is being used to solve a problem,” to help preserve a historical structure, he says. Ristevski says the Park Service was not charged for the data, and the work CyArk did was funded by individual Capturing photogrammetric data for the digital reconstruction of a badly damaged temple in donors in the San Francisco Bay Area, the ancient city of Bagan, in central Myanmar. where the company is located. CyArk is one of several organiza- data to build extremely precise 3D to use them to raise awareness of their tions using 3D scanning to help pro- models, says Yves Ubelmann, an ar- historical sites,’’ he says.