The CRAY- 1 Computer System

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Unit 18. Supercomputers: Everything You Need to Know About

GAUTAM SINGH UPSC STUDY MATERIAL – Science & Technology 0 7830294949 Unit 18. Supercomputers: Everything you need to know about Supercomputers have a high level of computing performance compared to a general purpose computer. In this post, we cover all details of supercomputers like history, performance, application etc. We will also see top 3 supercomputers and the National Supercomputing Mission. What is a supercomputer? A computer with a high level of computing performance compared to a general purpose computer and performance measured in FLOPS (floating point operations per second). Great speed and great memory are the two prerequisites of a super computer. The performance is generally evaluated in petaflops (1 followed by 15 zeros). Memory is averaged around 250000 times of the normal computer we use on a daily basis. THANKS FOR READING – VISIT OUR WEBSITE www.educatererindia.com GAUTAM SINGH UPSC STUDY MATERIAL – Science & Technology 0 7830294949 Housed in large clean rooms with high air flow to permit cooling. Used to solve problems that are too complex and huge for standard computers. History of Supercomputers in the World Most of the computers on the market today are smarter and faster than the very first supercomputers and hopefully, today’s supercomputer would turn into future computers by repeating the history of innovation. The first supercomputer was built in 1957 for the United States Department of Defense by Seymour Cray in Control Data Corporation (CDC) in 1957. CDC 1604 was one of the first computers to replace vacuum tubes with transistors. In 1964, Cray’s CDC 6600 replaced Stretch as the fastest computer on earth with 3 million floating-point operations per second (FLOPS). -

CRAY X-MP Series of Computer Systems

For close to a decade, Cray Research has been the industry leader in large-scale computer systems. Today, about 70 percent of all supercomputers installed worldwide are Cray systems. They are used in advanced scientific and research Eaboratories around the world and have gained strong acceptance in diverse industrial environments. No other manufacturer has Cray Research's breadth of success and experience in supercomputer development. The company's initial product, the CRAY-I Computer System, was first installed in 1976and quickly became the standard for large-scale scientific computers -and the first commercially successful vector processor. For some time previously, the potential advantages of vector processing had been understood, but effective practical implementation had eluded computer architects. The CRAY-1 broke that barrier, and today vectorization techniques are used commonly by scientists and engineers in a wide variety of disciplines. The field-proven GRAY X-MP Computer Systems now offer significantly more power tosolve new and bigger problems while providing better value than any other systems available. Large memory size options allow a wider range of problems to be solved, while innovative multiprocessor design provides practical opportunities to exploit multitasking, the next dimension of parallel processing beyond vectorization. Once again, Cray Research, has moved supercomputing forward, offering new levels of hardware performance and software techniques to serve the needs of scientists and engineers today and in the future. Introducing the CRAY X-MP Series of Computer Systems Announcing expanded capabilities to serve the needs of a broadening marketplace: the CRAY X-MP Series of Computer Systems. The CRAY X-MP Series now comprises nine models, ranging from a uniprocessor version with one million words of central memory to a top-end system with four processors and a 16-million-word memory. -

Musings RIK FARROWOPINION

Musings RIK FARROWOPINION Rik is the editor of ;login:. While preparing this issue of ;login:, I found myself falling down a rabbit hole, like [email protected] Alice in Wonderland . And when I hit bottom, all I could do was look around and puzzle about what I discovered there . My adventures started with a casual com- ment, made by an ex-Cray Research employee, about the design of current super- computers . He told me that today’s supercomputers cannot perform some of the tasks that they are designed for, and used weather forecasting as his example . I was stunned . Could this be true? Or was I just being dragged down some fictional rabbit hole? I decided to learn more about supercomputer history . Supercomputers It is humbling to learn about the early history of computer design . Things we take for granted, such as pipelining instructions and vector processing, were impor- tant inventions in the 1970s . The first supercomputers were built from discrete components—that is, transistors soldered to circuit boards—and had clock speeds in the tens of nanoseconds . To put that in real terms, the Control Data Corpora- tion’s (CDC) 7600 had a clock cycle of 27 .5 ns, or in today’s terms, 36 4. MHz . This was CDC’s second supercomputer (the 6600 was first), but included instruction pipelining, an invention of Seymour Cray . The CDC 7600 peaked at 36 MFLOPS, but generally got 10 MFLOPS with carefully tuned code . The other cool thing about the CDC 7600 was that it broke down at least once a day . -

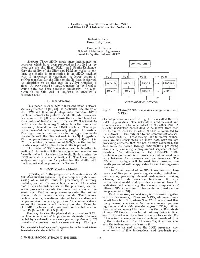

Performing the Shuffle with the PM2I and Illiac SIMD Interconnection Networks

Performing the Shuffle with the PM2I and Illiac SIMD Interconnection Networks Robert R. Seban Howard Jay Siegel Purdue University School of Electrical Engineering West Lafayette, Indiana 47907 Abstract—Three SIMD single stage interconnection networks which have been proposed and studied in the literature are the Illiac, PM2I, and Shuffle-Exchange. Here the ability of the Illiac and PM2I networks to per- form the shuffle interconnection in an SIMD machine with N processors is examined. A lower bound of 3\/N/2 transfers for the Illiac to shuffle data is derived. An algorithm to do this task in 2\/N-l transfers is given. A lower bound of log2N transfers for the PM2I to shuffle data has been published previously. An algo- rithm to do this task in log2N + l in transfers is presented here. 1. Introduction This paper extends SIMD interconnection network studies presented in [28, 31]. In particular, the ability of Fig. 1: PE-to-PE SIMD machine configuration, with the PM2I and Illiac single stage interconnection SIMD machine networks to perform the shuffle interconnection NPEs. is examined. In [28] it is shown that a lower bound on of configuration is shown in Fig. 1. It is called the PE- the number of transfers needed for the PM2I network to to-PE organization. The network is unidirectional and perform the shuffle is log2N, where N is the number of connects each PE to some subset of the other PEs. A processing elements in the SIMD machine. The algo- transfer instruction causes data to be moved from each rithm presented here requires only (log2N) + l transfers. -

Magnetic Peripherals Inc Storage Module Drive Vintage: C.1975 Synopsis: 14-Inch Cartridge Disk Drive

AccessionIndex: TCD-SCSS-T.20121208.028 Accession Date: 8-Dec-2012 Accession By: Tom Kearney Object name: Magnetic Peripherals Inc Storage Module Drive Vintage: c.1975 Synopsis: 14-inch cartridge disk drive. S/N: 652128. Description: Magnetic Peripherals Inc (MPI), of Minneapolis, Minnesota , was a joint venture formed by Control Data Corporation (CDC) and Honeywell Bull in 1975. CDC contributed their disk drive facilities at Normandale and Omaha, USA. Honeywell contributed its ex-GE disk plant at Oklahoma City and CII-Honeywell Bull’s plant at Heppenheim, Germany. Its early products were IBM-3330-like third generation disk drives, superceded by IBM-3340/3350/3370-like drives, all with IBM interfaces or Storage Module Device (SMD) interfaces. It became a major player in the hard disk drive market. It was the world wide leader in 14-inch disk drive technology in the OEM marketplace in the 1970s and early 1980s, especially with its SMD and CMD (Cartridge Module Drive) interfaces, and with its 24-hour/7-days-a-week plant at Brynmawr in South Wales, which celebrated the production of 1 million disks and 3 million magnetic tapes in Oct-1979. MPI was renamed Imprimus in 1988 and was bought by Seagate in 1989. The drive in this collection looks almost identical to a CDC9762 80MB disk drive, introduced in 1974 by CDC, see Figures 21 and 22. However, the drive in this collection was made in Portugal by Magnetic Peripherals Inc, and from the rear can be seen to have a different interface, which looks very like an SMD interface. -

Internet Engineering Task Force January 18-20, 1989 at University

Proceedings of the Twelfth Internet Engineering Task Force January 18-20, 1989 at University of Texas- Austin Compiled and Edited by Karen Bowers Phill Gross March 1989 Acknowledgements I would like to extend a very special thanks to Bill Bard and Allison Thompson of the University of Texas-Austin for hosting the January 18-20, 1989 IETF meeting. We certainly appreciated the modern meeting rooms and support facilities made available to us at the new Balcones Research Center. Our meeting was especially enhanced by Allison’s warmth and hospitality, and her timely response to an assortment of short notice meeting requirements. I would also like to thank Sara Tietz and Susie Karlson of ACE for tackling all the meeting, travel and lodging logistics and adding that touch of class we all so much enjoyed. We are very happy to have you on our team! Finally, a big thank you goes to Monica Hart (NRI) for the tireless and positive contribution she made to the compilation of these Proceedings. Phill Gross TABLE OF CONTENTS 1. CHAIRMANZS MESSAGE 2. IETF ATTENDEES 3. FINAL AGENDA do WORKING GROUP REPORTS/SLIDES UNIVERSITY OF TEXAS-AUSTIN JANUARY 18-20, 1989 NETWORK STATUS BRIEFINGS AND TECHNICAL PRESENTATIONS O MERIT NSFNET REPORT (SUSAN HARES) O INTERNET REPORT (ZBIGNIEW 0PALKA) o DOEESNET REPORT (TONY HAIN) O CSNET REPORT (CRAIG PARTRIDGE) O DOMAIN SYSTEM STATISTICS (MARK LOTTOR) O SUPPORT FOR 0SI PROTOCOLS IN 4.4 BSD (ROB HAGENS) O TNTERNET WORM(MICHAEL KARELS) PAPERS DISTRIBUTED AT ZETF O CONFORMANCETESTING PROFILE FOR D0D MILITARY STANDARD DATA COMMUNICATIONS HIGH LEVEL PROTOCOL ~MPLEMENTATIONS (DCA CODE R640) O CENTER FOR HIGH PERFORMANCE COMPUTING (U OF TEXAS) Chairman’s Message Phill Gross NRI Chair’s Message In the last Proceedings, I mentioned that we were working to improve the services of the IETF. -

RATFOR User's Guide B

General Disclaimer One or more of the Following Statements may affect this Document This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible. This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available. This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white. This document is paginated as submitted by the original source. Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission. Produced by the NASA Center for Aerospace Information (CASI) NASA CONTRACTOR REPORT 166601 Ames RATFOR User's Guide b Leland C. Helmle (NASA—CH-166601) RATFOR USERS GUIDE 0 (Informatics General Corp,) N85-16490 51 p HC A04/mZ A01 CSCL 09B Unclas G3/61 13243 CONTRACT NAS2— 11555 January 1985 v NASA NASA CONTRACTOR REPORT 166601 *i Ames RATF'OR User's Guide Leland C. Helmle Informatics General Corporation 1121 San Antonio Road Palo Alto, CA 94303 i i _I Prepared for Ames Research Center under Contract NAS2-11555 i n ASA National Aeronautics and 1 Space Administration Ames Research Center Moffett Field, California 94035 '^ I I w Ames R.A.TFOR User's Guide Version 2.0 by Loland C. Helmle Informatics General Corporation July 16, 1983 Prepared under Contract NA52-11555, Task 101 ^ Table of Contents page v 1 Introduction . -

Cielo Computational Environment Usage Model

Cielo Computational Environment Usage Model With Mappings to ACE Requirements for the General Availability User Environment Capabilities Release Version 1.1 Version 1.0: Bob Tomlinson, John Cerutti, Robert A. Ballance (Eds.) Version 1.1: Manuel Vigil, Jeffrey Johnson, Karen Haskell, Robert A. Ballance (Eds.) Prepared by the Alliance for Computing at Extreme Scale (ACES), a partnership of Los Alamos National Laboratory and Sandia National Laboratories. Approved for public release, unlimited dissemination LA-UR-12-24015 July 2012 Los Alamos National Laboratory Sandia National Laboratories Disclaimer Unless otherwise indicated, this information has been authored by an employee or employees of the Los Alamos National Security, LLC. (LANS), operator of the Los Alamos National Laboratory under Contract No. DE-AC52-06NA25396 with the U.S. Department of Energy. The U.S. Government has rights to use, reproduce, and distribute this information. The public may copy and use this information without charge, provided that this Notice and any statement of authorship are reproduced on all copies. Neither the Government nor LANS makes any warranty, express or implied, or assumes any liability or responsibility for the use of this information. Bob Tomlinson – Los Alamos National Laboratory John H. Cerutti – Los Alamos National Laboratory Robert A. Ballance – Sandia National Laboratories Karen H. Haskell – Sandia National Laboratories (Editors) Cray, LibSci, and PathScale are federally registered trademarks. Cray Apprentice2, Cray Apprentice2 Desktop, Cray C++ Compiling System, Cray Fortran Compiler, Cray Linux Environment, Cray SHMEM, Cray XE, Cray XE6, Cray XT, Cray XTm, Cray XT3, Cray XT4, Cray XT5, Cray XT5h, Cray XT5m, Cray XT6, Cray XT6m, CrayDoc, CrayPort, CRInform, Gemini, Libsci and UNICOS/lc are trademarks of Cray Inc. -

Sperry Corporation, UNIVAC Division Photographs and Audiovisual Materials 1985.261

Sperry Corporation, UNIVAC Division photographs and audiovisual materials 1985.261 This finding aid was produced using ArchivesSpace on September 14, 2021. Description is written in: English. Describing Archives: A Content Standard Audiovisual Collections PO Box 3630 Wilmington, Delaware 19807 [email protected] URL: http://www.hagley.org/library Sperry Corporation, UNIVAC Division photographs and audiovisual materials 1985.261 Table of Contents Summary Information .................................................................................................................................... 3 Historical Note ............................................................................................................................................... 4 Scope and Content ......................................................................................................................................... 5 Arrangement ................................................................................................................................................... 6 Administrative Information ............................................................................................................................ 6 Related Materials ........................................................................................................................................... 7 Controlled Access Headings .......................................................................................................................... 8 Bibliography -

Online Sec 6.15.Indd

6.155.9 Historical Perspective and Further Reading Th ere is a tremendous amount of history in multiprocessors; in this section we divide our discussion by both time period and architecture. We start with the SIMD approach and the Illiac IV. We then turn to a short discussion of some other early experimental multiprocessors and progress to a discussion of some of the great debates in parallel processing. Next we discuss the historical roots of the present multiprocessors and conclude by discussing recent advances. SIMD Computers: Attractive Idea, Many Attempts, No Lasting Successes Th e cost of a general multiprocessor is, however, very high and further design options were considered which would decrease the cost without seriously degrading the power or effi ciency of the system. Th e options consist of recentralizing one of the three major components. Centralizing the [control unit] gives rise to the basic organization of [an] . array processor such as the Illiac IV. Bouknight et al. [1972] Th e SIMD model was one of the earliest models of parallel computing, dating back to the fi rst large-scale multiprocessor, the Illiac IV. Th e key idea in that multiprocessor, as in more recent SIMD multiprocessors, is to have a single instruction that operates on many data items at once, using many functional units (see Figure 6.15.1). Although successful in pushing several technologies that proved useful in later projects, it failed as a computer. Costs escalated from the $8 million estimate in 1966 to $31 million by 1972, despite construction of only a quarter of the planned multiprocessor. -

(U) NSA's Key Role in Major Developments in Computer Science

.............. -· ,.. , __ .,,...... ___ , _.,.._ ~ __ ....:" -..... .. Doc ID: 6586785 _ __ I 5 SSRFI;';'?Et U 'f'; !! i; I llJ l!llft, I dL& (U) NSA's Key Role in Major Developments in Computer Science PART ONE (U) Cryptology has historically entailed an intensive application of labor. But since the middle of the last century, automation has been used as a way to greatly ease the making and breaking of codes. The formation and maturation of the National Security Agency (NSA) and the evolution of its missions paralleled in large part the advent of the computer age. A!J a consequence, the NSA and its predecessor agencies have historically been at the forefront of computer development in the United States. {U) But the use of computational machines in American cryptology long predated the official birth ofNSA. During World War I, the military incorporated use of encryption equipment. During the 1930s, both the Army and Navy cryptologic components acquired devices from International Business Machines {IBM), which allowed them to sort large amounts of data. By the time World War II had broken out, all of the major combatants possessed sophisticated cipher machines for most of their communications generation and security programs. {U) As the war progressed, the U.S. military services placed many electronic accounting machines into the field in order to process a wide array of enemy signals. The services developed relationships with industry -- Bell Laboratories and Teletype Corporation in the case of the Army, and IBM, Eastman Kodak, and National Cash Register (NCR) in the case of the Navy. A prime example of the benefits of such relationships was the construction of the Navy's cryptanalytic "Bombe," a machine built by NCR to decipher messages from the German ENIGMA machine. -

Seymour Cray: the Father of World Supercomputer

History Research 2019; 7(1): 1-6 http://www.sciencepublishinggroup.com/j/history doi: 10.11648/j.history.20190701.11 ISSN: 2376-6700 (Print); ISSN: 2376-6719 (Online) Seymour Cray: The Father of World Supercomputer Si Hongwei Department of the History of Science, Tsinghua University, Beijing, China Email address: To cite this article: Si Hongwei. Seymour Cray: The Father of World Supercomputer. History Research. Vol. 7, No. 1, 2019, pp. 1-6. doi: 10.11648/j.history.20190701.11 Received : May 14, 2019; Accepted : June 13, 2019; Published : June 26, 2019 Abstract: Seymour R. Cray was an American engineer and supercomputer developer who designed a series of the fastest computers in the world in 1960-1980s. The difference between Cray and most other corporate engineers is that he often won those business battles. His success was attributable to his existence in a postwar culture where engineers were valued. He was able to also part of an extraordinary industry where revolutionary developments were encouraged, and even necessary. Lastly Cray is recognized as "the father of world supercomputer". From the perspective of science and technology history, this paper describes the history of Cray and his development of supercomputer. It also sums up his innovative ideas and scientific spirit. It provides a reference for supercomputer enthusiasts and peers in the history of computer research. Keywords: Seymour R. Cray, Supercomputer, Science and Technology History 1. Introduction 2. The Genius Seymour Supercomputer refers to the most advanced electronic computer system with the most advanced technology, the Seymour Cray was born on September 28th, 1925 in the fastest computing speed, the largest storage capacity and the town of Chippewa, Wisconsin.