ESP32 Hardware Design Guidelines

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

17 Electronics Assembly Basic Expe- Riments with Breadboard

118.381 17 Electronics Assembly Basic Expe- riments with BreadboardTools Required: Stripper Side Cutters Please Note! The Opitec Range of projects is not intended as play toys for young children. They are teaching aids for young people learning the skills of craft, design and technology. These projects should only be undertaken and operated with the guidance of a fully qualified adult. The finished pro- jects are not suitable to give to children under 3 years old. Some parts can be swallowed. Danger of suffocation! Article List Quantity Size (mm) Designation Part-No. Plug-in board/ breadboard 1 83x55 Plug-in board 1 Loudspeaker 1 Loudspeaker 2 Blade receptacle 2 Connection battery 3 Resistor 120 Ohm 2 Resistor 4 Resistor 470 Ohm 1 Resistor 5 Resistor 1 kOhm 1 Resistor 6 Resistor 2,7 kOhm 1 Resistor 7 Resistor 4,7 kOhm 1 Resistor 8 Resistor 22 kOhm 1 Resistor 9 Resistor 39 kOhm 1 Resistor 10 Resistor 56 kOhm 1 Resistor 11 Resistor 1 MOhm 1 Resistor 12 Photoconductive cell 1 Photoconductive cell 13 Transistor BC 517 2 Transistor 14 Transistor BC 548 2 Transistor 15 Transistor BC 557 1 Transistor 16 Capacitor 4,7 µF 1 Capacitor 17 Elko 22µF 2 Elko 18 elko 470µF 1 Elko 19 LED red 1 LED 20 LED green 1 LED 21 Jumper wire, red 1 2000 Jumper Wire 22 1 Instruction 118.381 17 Electronics Assembly Basic Experiments with Breadboard General: How does a breadboard work? The breadboard also called plug-in board - makes experimenting with electronic parts immensely easier. The components can simply be plugged into the breadboard without soldering them. -

Introduction to Electronics and Breadboarding Circuits

Introduction to Electronics and Breadboarding Circuits What we're going to learn today: What is an electronic circuit? What kind of power is needed for these projects? What are the fundamental principles of electronics? What are the basic electronic components used in DC analog circuits? How do these principles combine to make interesting things? We're going to make some of those things, and you can take the kit, and the projects home with you. Class Parts List Breadboard 1 10uf capacitor 1 Wire kit 1 47uf 1 Red LEDs 3 100uf 1 Green LEDs 3 1000uf Cap 1 Yellow LEDs 1 1500uf cap 6.3v 1 Photoresistor 1 10k Resistors 1 xPiezo sensor 1 1k Resistors 1 Button 3 330 ohm Resistors 1 Slide button, switch 1 Reed switch 1 Potentiometer Hall effect sensor 1 Rare Earth Magnet 1 Tilt ball switch 1 Transistor pn2222 1 TIP120 1 Relay 1 RGB led 1 Dc toy motor 1 Diode 1n4001 1 Lm7805 1 Power connector 1 9v snap power connector 1 About parts Symmetric vs Asymmetric Polarized Physics and chemistry in a tiny package Explain Data Sheets What is electricity? What kinds are there? What can it do? What are the dangers? Batteries as a power source What kinds of batteries are there? What is a circuit? Combination of electronic parts, wires connected between power sources. It's like a physical program. It's also like setting up dominoes in sequence. What is a breadboard? What are they good for? Creatings, organizing, and prototyping a circuit. Literally started out as a bread board with nails. -

Breadboards for Beginners Created by Lady Ada

Breadboards for Beginners Created by lady ada Last updated on 2018-08-22 03:56:03 PM UTC Guide Contents Guide Contents 2 Introduction 3 What's up with the name? 4 ~~ Interlude ~~ (Wire Wrapping) 5 1971 - The Breadboard Is Invented! 6 Breadboards 8 The curse of the flaky breadboard 10 Other Breadboard Sizes 11 Half Size 11 Tiny Breadboard 12 Little Breadboard Bits 13 Large Breadboard 15 Breadboard Usage 17 Adding DIPs and Modules 19 Jumper Wires 21 DIY Solid Core Wire Jumpers 21 Multi-size wire stripper & cutter 21 Hook-up Wire Spool Set - 22AWG Solid Core - 6 x 25 ft 21 Pre-made Jumper Wires 26 Premium Male/Male Jumper Wires - 40 x 3" (75mm) 26 Premium Male/Male Jumper Wires - 40 x 6" (150mm) 26 Premium Male/Male Jumper Wires - 40 x 12" (300mm) 26 Perma Protos 27 Adafruit Perma-Proto Quarter-sized Breadboard PCB - Single 29 Adafruit Perma-Proto Full-sized Breadboard PCB - Single 30 Adafruit Perma-Proto Mint Tin Size Breadboard PCB 30 Adafruit Perma-Proto Small Mint Tin Size Breadboard PCB - 3 pack 30 Breadboard Tips & Tricks 31 Connecting the two power rails 31 Watch Out For Split Rails! 32 Using Fritzing! 32 © Adafruit Industries https://learn.adafruit.com/breadboards-for-beginners Page 2 of 34 Introduction When you start on your electronics journey, you will eventually need to wire up some parts to follow along with some project. And, chances are, you will be prodded towards using a breadboard. These ubiquitous pale slabs of plastic are everywhere when it comes to electronics hacking. -

(EE2490 Experiment1.Doc Nwp 8/23/16) CALIFORNIA STATE

(EE2490_Experiment1.doc nwp 8/23/16) CALIFORNIA STATE UNIVERSITY LOS ANGELES Department of Electrical and Computer Engineering EE-2449 Digital Logic Lab EXPERIMENT 1 INTRODUCTION TO ELECTRIC CIRCUITS Required hardware and tools: Breadboard with test circuitry, 15 KΩ (Kilo Ohm) resistor (brown-green- orange), 2.2 KΩ resistor (red-red-red), 330 Ω resistor (orange-orange-brown), 2 green LEDs, 2N4124 NPN Silicon Transistor, AL 21649 pushbutton switch, breadboard wires, and logic probe. Resistor Color Code Conversion Calculator: To help you determine the value of resistors, you can use this calculator: http://www.digikey.com/en/resources/conversion-calculators/conversion-calculator-resistor- color-code-4-band. Note: While conducting the experiment you should record the circuit diagrams of circuits you are building, record observations from experimenting with the circuits, and record your answers to the questions throughout the experiment in your lab journal (a composition book). If you have not had a chance to purchase the composition book, for the first experiment you can use a piece of paper that you will paste into your lab journal. Every section that requires you to build a circuit and test it has an asterisk (*). For those sections, demonstrate the working circuit to your lab instructor. They will sign off on your experiment. You can often build multiple circuits or variations before getting a sign off and then demonstrate the various versions of the circuit together to your instructor. 1.1 Simply defined, an electric circuit is a closed loop where through which charges (electrons) can continually flow. Electric circuits can be analog or digital. -

IEEE Iot Sketch01 – Blink

Internet of Things Weather Station IEEE Northern Virginia Section Hands-On Professional Development Series October 29, 2016 Montgomery College Unboxing & Sketch 01-Blink 2 10/29/2016 Course Materials All course materials are at: http://w4krl.com/projects/ieee-iot/2016october/ Download the construction slides so that you can follow along: – IEEE IoT Sketch01 – Blink – IEEE IoT Sketch02 – Hello World – IEEE IoT Sketch03 – Standalone Weather Station – IEEE IoT Sketch04 – IoT Weather Station – IEEE IoT Sketch05 – Smartphone Weather Station (if time is available) We will download Arduino sketches and libraries when needed. There are links to software, schematics, data sheets, and tutorials. 3 10/29/2016 Project Road Map 4 10/29/2016 Parts List Jumpers Power Supply Dual Voltage 4-Wire Regulator Jumper Micro USB Liquid Crystal Cable Display NodeMCU Level Shifter BME280 BH1750 LEDs (2) Resistors (2) Breadboard Switch Keep the small parts in the bag for now. 5 10/29/2016 Microcontroller A microcontroller is a System on Chip computer –Processor, memory, analog & digital I/O, & radio frequency circuits Embedded in a device with a dedicated purpose Generally low power and often battery powered Program is stored in firmware & is rarely changed Has multiple digital General Purpose Input / Output, analog-to-digital conversion, pulse width modulation, timers, special purpose I/O 6 10/29/2016 ESP8266 Timeline January 2014 - Introduced by Expressif Systems of Shanghai as a Wi-Fi modem chip. Early adopters used Hayes “AT” commands generated by an Arduino or Raspberry Pi. Not breadboard friendly. No FCC certification. October 2014 - Expressif released the Software Development Kit (SDK) making its use as a slave modem obsolete. -

Prototyping Techniques Help Verify Analog-Circuit Performance

EDN -- 02.15.96 Prototyping techniques help verify analog-circuit performance http://www.ednmag.com/reg/1996/021596/04df3.htm Design Feature: February 15, 1996 Prototyping techniques help verify analog-circuit performance Walt Kester, Analog Devices Despite the pressure for system engineers to simulate every design, a simulation of a high-speed, high-performance analog circuit cannot substitute for a quality prototype. A review of prototyping methods helps you choose a technique suitable for your design. Analog designers use as many tools as possible to ensure that the final system design performs correctly. The first step is the intelligent use of IC macromodels, if available, to simulate the circuit. The second step is the construction of a prototype board to further verify the design. The final pc-board layout should as closely as possible duplicate the prototype layout. Unfortunately, system designers are under increasing pressure to verify their designs, sometimes exclusively, with computer simulations before committing to board layouts and hardware. Simulating complex digital designs is beneficial, because such simulations often let you eliminate the prototype phase. Bypassing the prototype phase in high-speed, high-performance analog or mixed-signal circuit designs can be risky for many reasons, however. The models available to system designers are only gross approximations of the analog components they emulate (see box, "The limitations of analog-circuit simulation"). Even if semiconductor manufacturers made more detailed models available, simulation times would be impractically long, and the simulations might fail to converge. Thus, designers of analog circuits must become proficient at prototyping to experimentally verify their analog circuit's performance. -

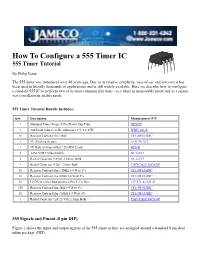

How to Configure a 555 Timer IC 555 Timer Tutorial

How To Configure a 555 Timer IC 555 Timer Tutorial By Philip Kane The 555 timer was introduced over 40 years ago. Due to its relative simplicity, ease of use and low cost it has been used in literally thousands of applications and is still widely available. Here we describe how to configure a standard 555 IC to perform two of its most common functions - as a timer in monostable mode and as a square wave oscillator in astable mode. 555 Timer Tutorial Bundle Includes: Qty. Description Manufacturer P/N 1 Standard Timer Single 8-Pin Plastic Dip Tube NE555P 1 400-Point Solderless Breadboard 3.3"L x 2.1"W WBU-301-R 10 Resistor Carbon Film 10kΩ CF1/4W103JRC 1 9V Alkaline Battery ALK 9V 522 1 9V Battery Snap with 6" 26AWG Leads BC6-R 2 3-Pin SPDT Slide Switch SS-12E17 2 Radial Capacitor 0.01µF 2.54mm Bulk SS-12E17 1 Radial Capacitor 4.7µF 2.5mm Bulk TAP475K025SCS-VP 10 Resistor Carbon Film 1.0MΩ 1/4 Watt 5% CF1/4W105JRC 10 Resistor Carbon Film 220Ω 1/4 Watt 5% CF1/4W221JRC 10 LED Uni-Color Red 660nm 2-Pin T-1¾ Box UT1871-81-M1-R 100 Resistor Carbon Film 3kΩ 1/4 Watt 5% CF1/4W302JRC 10 Resistor Carbon Film 330kΩ 1/4 Watt 5% CF1/4W334JRC 1 Radial Capacitor 1µF 25 Volt 2.5mm Bulk TAP105K025SCS-VP 555 Signals and Pinout (8 pin DIP) Figure 1 shows the input and output signals of the 555 timer as they are arranged around a standard 8 pin dual inline package (DIP). -

Using the Breadboard (Socket Board)

Using the Breadboard (Socket Board) The bread board has many strips of metal (copper usually) which run underneath theboard. The metal strips are laid out as shown below. These strips connect the holes on the top of the board. This makes it easy to connect components together to build circuits. To use the bread board, the legs of components are placed in the holes (the sockets). The holes are made so that they will hold the component in place. Each hole is connected to one of the metal strips running underneath the board. Each wire forms a node. A node is a point in a circuit where two components are connected. Connections between different components are formed by putting their legs in a common node. On the bread board, a node is the row of holes that are connected by the strip of metal underneath. The long top and bottom row of holes are usually used for power supply The rest of the circuit is built by placing components and connecting them together with jumper wires. Then when a path is formed by wires and components from the positive supply node to the negative supply node, we can turn on the power and current flows through the path and the circuit comes alive. For chips with many legs (ICs), place them in the middle of the board so that half of the legs are on one side of the middle line and half are on the other side. A completed circuit might look like the following. Both are 4 bit D/A circuits Notes: Depending on the size of the breadboard, there might be a break in the connection in the middle of the board for the ground and voltage connections. -

Title: Clap Switch

Title: Clap Switch I. Summary A Clap Switch circuit uses a microphone within the circuit to detect noises to turn the LED on. A clap switch circuit can be used in homes and businesses to turn on things such as: lights, TVs, or whatever it is set up to the clap switch. In many cases you can snap your fingers, clap your hands, or even speak to it. In fact, with modern technology, you can use commands to activate a piece/pieces of technology to allow it to turn on/off from anywhere within the room of the Clap Switch. II. Objective Individuals will construct a Clap Switch circuit and gain based knowledge on the 555 timer IC, BC547 Transistor and the condenser microphone. Also, individuals will get to see exactly how you can turn things on by a simply clap, snap, and/or the use of the voice. III. Industry Clap Switches can be installed into businesses and homes to allow individuals to turn lights and a number of technology on or off by using claps, snaps, or his/her voice. Clap Switches gives individuals the ability to remain seated or lying down to turn devices on or off. Also, this device is important to industries because technology is growing at an extreme rate and with the component within the Clap Switch it can help advance technology even more. In today’s world, we use voice control within our mobile devices, as well as, devices like the Echo, Google Home, etc. Within these devices that I previously listed, you can turn on a number of technologies by giving it simple voice commands, which is something that a great number of companies are working on – on a daily basis. -

Electronic and Electromechanical Prototyping

Electronic and electromechanical prototyping Introduction Corso LM ‘Materiali Intelligenti e Biomimetici’ – Prof. A. Ahluwalia 20/04/2017 [email protected] Electronic and electromechanical prototyping If you wanted to build a circuit prior to the 1960s, chances are you would have used a technique called wire-wrap. Wire wrap is a process that involves wrapping wires around conductive posts attached to a perfboard. As you can see, the process can get rather complex very quickly. Although this method is still used today, there is something that makes prototyping much easier, breadboards! Breadboards An electronics breadboard is actually referring to a solderless breadboard. These are great units for making temporary circuits and prototyping, and they require absolutely no soldering. Another common use of breadboards is testing out new parts, such as Integrated circuits (ICs). When you are trying to figure out how a part works and constantly rewiring things, you don’t want to have to solder your connections each time. Breadboards 2 Terminal Strips are horizontal rows of metal strips on the bottom of the breadboard. Once inserted that component will be electrically connected to anything else placed in that row. This is because the metal rows are conductive and allow current to flow from any point in that strip. Power Rails are metal strips that run vertically along the sides. When building a circuit, you tend to need power in lots of different places. The power rails give you lots of easy access to power wherever you need it in your circuit. Usually they will be labeled with a ‘+’ and a ‘-’, to indicate the positive and negative side. -

A Guide to Making an 8Bit Breadboard Computer and the Basics of Computer Science

A Guide to Making an 8bit Breadboard Computer and the Basics of Computer Science BY: PABLO LANZA Table of Contents: Introduction 3 The Basics of Computer Science 4 Component Overview 8 Making the Computer 11 The Clock 12 The Register 15 The ALU 21 The RAM Module 27 The Program Counter 35 The Bus 39 The Control Logic 41 Programing the Computer 54 Finishing Touches 56 Further Additions 58 Materials 59 Conclusion 60 Introduction Our modern everyday lives would be completely different, if not impossible without the invention of the computer. Just imagine having to go to the library looking through volumes of an encyclopedia, just to look up a simple piece of information that would’ve taken you less than a minute to google. And it’s not just out laptops and PCs that are computers, everything modern, from our cars to our TVs and the ever-expanding internet of things, have some sort of processing computer that allow it to function properly. Despite the omnipresence of computers in modern society most people live in ignorance regarding how they actually work. When asked the question of “how do computer work?” the majority of people would simply answer with an “I dunno”. However, the truth is quite complicated, as there are billions of processes happening every instant making your computer display this very guide that you are reading. In this guide I will hopefully clear up some of the mystery surrounding computers. And even though by the end of it you’ll still be equally baffled as to how modern computers work, you will know the basic concepts behind computer science, and will grow a sense of respect towards the hundreds of engineers that made this marvel of modern technology possible. -

Prototyping Techniques

Electronic Circuit Prototyping Techniques Document Revision: 1.01 Date: February, 2007 16301 Blue Ridge Road, Missouri City, Texas 77489 Telephone: 1-713-283-9970 Fax: 1-281-416-2806 E-mail: [email protected] Web: www.bipom.com This document is available for download from www.bipom.com © 2009 by BiPOM Electronics. All rights reserved. Electronic Circuit Prototyping Techniques. No part of this work may be reproduced in any manner without written permission of BiPOM Electronics. All trademarked names in this manual are the property of respective owners. Prototype Design Methodology: 1. Specifications based on requirements 2. Research 3. Schematics 4. Simulation 5. Construction (PCB Layout or other wiring technique) 6. Parts Purchase 7. Assembly 8. Firmware Development ( Assembly, C and/or BASIC ) 9. Testing and debugging Construction Breadboard: Quick way to set up a circuit. It can be used only with through-hole components although adapters for some surface mount devices exist. Not suitable for high frequencies, due to stray capacitance and inductance. Also, long connecting traces inside the breadboard act as antennas. Also, not suitable for high current and/or high voltage circuits. Breadboard cable for BiPOM boards: EXPCABLE-BR1 Point to point wiring: More permanent than breadboard. Components are soldered to a perforated board, typically known as Vero board. Radio Shack sells these. 2 Wirewrapping: It used to be popular in the 70’s and 80’s. Similar to point to point wiring except that a special tool/gun and special sockets are used. Wire is connected to endpoints by wrapping onto a rectangular pin, instead of soldering.