Fully Integrated CMOS Power Amplifier Design Using the Distributed Active-Transformer Architecture Ichiro Aoki, Student Member, IEEE, Scott D

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

What Is a Neutral Earthing Resistor?

Fact Sheet What is a Neutral Earthing Resistor? The earthing system plays a very important role in an electrical network. For network operators and end users, avoiding damage to equipment, providing a safe operating environment for personnel and continuity of supply are major drivers behind implementing reliable fault mitigation schemes. What is a Neutral Earthing Resistor? A widely utilised approach to managing fault currents is the installation of neutral earthing resistors (NERs). NERs, sometimes called Neutral Grounding Resistors, are used in an AC distribution networks to limit transient overvoltages that flow through the neutral point of a transformer or generator to a safe value during a fault event. Generally connected between ground and neutral of transformers, NERs reduce the fault currents to a maximum pre-determined value that avoids a network shutdown and damage to equipment, yet allows sufficient flow of fault current to activate protection devices to locate and clear the fault. NERs must absorb and dissipate a huge amount of energy for the duration of the fault event without exceeding temperature limitations as defined in IEEE32 standards. Therefore the design and selection of an NER is highly important to ensure equipment and personnel safety as well as continuity of supply. Power Transformer Motor Supply NER Fault Current Neutral Earthin Resistor Nov 2015 Page 1 Fact Sheet The importance of neutral grounding Fault current and transient over-voltage events can be costly in terms of network availability, equipment costs and compromised safety. Interruption of electricity supply, considerable damage to equipment at the fault point, premature ageing of equipment at other points on the system and a heightened safety risk to personnel are all possible consequences of fault situations. -

Measurement Error Estimation for Capacitive Voltage Transformer by Insulation Parameters

Article Measurement Error Estimation for Capacitive Voltage Transformer by Insulation Parameters Bin Chen 1, Lin Du 1,*, Kun Liu 2, Xianshun Chen 2, Fuzhou Zhang 2 and Feng Yang 1 1 State Key Laboratory of Power Transmission Equipment & System Security and New Technology, Chongqing University, Chongqing 400044, China; [email protected] (B.C.); [email protected] (F.Y.) 2 Sichuan Electric Power Corporation Metering Center of State Grid, Chengdu 610045, China; [email protected] (K.L.); [email protected] (X.C.); [email protected] (F.Z.) * Correspondence: [email protected]; Tel.: +86-138-9606-1868 Academic Editor: K.T. Chau Received: 01 February 2017; Accepted: 08 March 2017; Published: 13 March 2017 Abstract: Measurement errors of a capacitive voltage transformer (CVT) are relevant to its equivalent parameters for which its capacitive divider contributes the most. In daily operation, dielectric aging, moisture, dielectric breakdown, etc., it will exert mixing effects on a capacitive divider’s insulation characteristics, leading to fluctuation in equivalent parameters which result in the measurement error. This paper proposes an equivalent circuit model to represent a CVT which incorporates insulation characteristics of a capacitive divider. After software simulation and laboratory experiments, the relationship between measurement errors and insulation parameters is obtained. It indicates that variation of insulation parameters in a CVT will cause a reasonable measurement error. From field tests and calculation, equivalent capacitance mainly affects magnitude error, while dielectric loss mainly affects phase error. As capacitance changes 0.2%, magnitude error can reach −0.2%. As dielectric loss factor changes 0.2%, phase error can reach 5′. -

A Design Methodology and Analysis for Transformer-Based Class-E Power Amplifier

electronics Communication A Design Methodology and Analysis for Transformer-Based Class-E Power Amplifier Alfred Lim 1,2,* , Aaron Tan 1,2 , Zhi-Hui Kong 1 and Kaixue Ma 3,* 1 School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798, Singapore; [email protected] (A.T.); [email protected] (Z.-H.K.) 2 GLOBALFOUNDRIES, Singapore 738406, Singapore 3 School of Microelectronics, Tianjin University of China, Tianjin 300027, China * Correspondence: [email protected] (A.L.); [email protected] (K.M.) Received: 28 March 2019; Accepted: 26 April 2019; Published: 2 May 2019 Abstract: This paper proposes a new technique and design methodology on a transformer-based Class-E complementary metal-oxide-semiconductor (CMOS) power amplifier (PA) with only one transformer and two capacitors in the load network. An analysis of this amplifier is presented together with an accurate and simple design procedure. The experimental results are in good agreement with the theoretical analysis. The following performance parameters are determined for optimum operation: The current and voltage waveform, the peak value of drain current and drain-to-source voltage, the output power, the efficiency and the component values of the load network are determined to be essential for optimum operation. The measured drain efficiency (DE) and power-added efficiency (PAE) is over 70% with 10-dBm output power at 2.4 GHz, using a 65 nm CMOS process technology. Keywords: Class-E; transformer-based; silicon CMOS; wireless communication; power amplifier 1. Introduction With the explosive growth of wireless and mobile communication systems adoption, the demand for compact, low-cost and low power portable transceiver has increased dramatically. -

60 Ghz CMOS Amplifiers Using Transformer- Coupling and Artificial

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 44, NO. 5, MAY 2009 1425 60 GHz CMOS Amplifiers Using Transformer- Coupling and Artificial Dielectric Differential Transmission Lines for Compact Design Tim LaRocca, Member, IEEE, Jenny Yi-Chun Liu, Student Member, IEEE, and Mau-Chung Frank Chang, Fellow, IEEE Abstract—57–65 GHz differential and transformer-coupled power and variable-gain amplifiers using a commercial 90 nm digital CMOS process are presented. On-chip transformers com- bine bias, stability and input/interstage matching networks to enable compact designs. Balanced transmission lines with artifi- cial dielectric strips provide substrate shielding and increase the effective dielectric constant up to 54 for further size reduction. Consequently, the designed three-stage power amplifier occupies only an area of only 0.15 mmP. Under a 1.2 V supply, it consumes 70 mA and obtains small-signal gains exceeding 15 dB, saturated output power over 12 dBm and associated peak power-added efficiency (PAE) over 14% across the band. The variable-gain amplifier, based on the same principle, achieved a peak gain of 25 dB with 8 dB of gain variation. Fig. 1. Differential transmission line with floating artificial dielectric strips. Index Terms—CMOS, differential amplifiers, millimeter-wave amplifiers, power amplifiers, transformers. minimal size to allow a high level of integration within a I. INTRODUCTION low-cost 60 GHz CMOS transceiver. Artificial dielectric strips, as shown in Fig. 1, are inserted be- CMOS transformer-coupled power amplifier and vari- neath a differential line [2], [3] and coplanar waveguide [4] on A able-gain amplifier for the unlicensed 57–64 GHz CMOS as a method to reduce the physical length of the trans- spectrum are presented with high efficiency and compact mission line by increasing the effective dielectric constant while designs. -

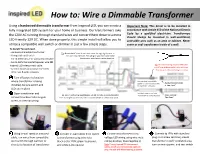

How To: Wire a Dimmable Transformer

How to: Wire a Dimmable Transformer Using a hardwired dimmable transformer from Inspired LED, you can create a Important Note: This driver is to be installed in accordance with Article 450 of the National Electric fully integrated LED system for your home or business. Our transformers take the 120V AC running through standard wires and convert them down to a more Code by a qualified electrician. Transformers should always be mounted in well-ventilated, LED friendly 12V DC. When done properly, this simple install will allow you to accessible area such as an attic or cabinet. Never utilize a compatible wall switch or dimmer in just a few simple steps… cover or seal transformer inside of a wall. To Install: You will need… - Hardwire dimmable transformer Tip: Route the AC wires from transformer through rigid spacer to - Compatible wall switch the open box extender. This will give you more room to tie 12VDC - 14-16 AWG Class 2 in-wall/armored cable transformer and dimmer wiring together. - 16-22 AWG thermostat/speaker wire OR Tip: To connect using Inspired LED cable, Inspired LED interconnect cable cut off one end connector, split and strip. - Junction box(es) (optional if needed) The side with white lettering is positive. - Wire nuts & cable strippers 1. Turn off power to location Use standard Inspired LED where transformer is being cables to run from transformer Standard end connectors installed, be sure switch and to standard 3.5mm jacks or Tiger Paws® LEDs are in place Use bulk cable to run from 2. Open transformer and Tip: For in-wall wiring applications, use 18-22 AWG 2-conductor cable transformer to screw terminals Screw Terminal remove knockout holes to gain Class 2 or higher (commonly sold as in-wall speaker or thermostat wire). -

Transformer Design & Design Parameters

Transformer Design & Design Parameters - Ronnie Minhaz, P.Eng. Transformer Consulting Services Inc. Power Transmission + Distribution GENERATION TRANSMISSION SUB-TRANSMISSION DISTRIBUTION DISTRIBUTED POWER 115/10 or 20 kV 500/230 230/13.8 132 345/161 161 161 230/115 132 230 230/132 115 345 69 500 34 Generator Step-Up Auto-transformer Step-down pads transformer transformer Transformer Consulting Services Inc. Standards U.S.A. • (ANSI) IEEE Std C57.12.00-2010, standard general requirements for liquid- immersed distribution, power and regulation transformers • ANSI C57.12.10-2010, safety requirements 230 kV and below 833/958 through 8,333/10,417 KVA, single-phase, and 750/862 through 60,000/80,000/100,000 KVA, three-phase without load tap changing; and 3,750/4,687 through 60,000/80,000/100,000 KVA with load tap changing • (ANSI) IEEE C57.12.90-2010, standard test code for liquid-immersed distribution, power and regulating transformers and guide for short-circuit testing of distribution and power transformers • NEMA standards publication no. TR1-2013; transformers, regulators and reactors Canada CAN/CSA-C88-M90(reaffirmed 2009); power transformers and reactor; electrical power systems and equipment Transformer Consulting Services Inc. Transformer Design: • Power rating [MVA] • Core • Rated voltages (HV, LV, TV) • Insulation coordination (BIL, SIL, ac tests) • Short-circuit Impedance, stray flux • Short-circuit Forces • Loss evaluation • Temperature rise limits, Temperature limits • Cooling, cooling method • Sound Level • Tap changers (DTC, LTC) Transformer Consulting Services Inc. Transformer Design: Simple Transformer • Left coil - input (primary coil) – Source – Magnetizing current • Right coil - output (secondary coil) – Load • Magnetic circuit Transformer Consulting Services Inc. -

Rectifier Troubleshooting

TROUBLESHOOTING PRELIMINARY • To troubleshoot, one must first have a working knowledge of the individual parts and their relation to one another. • Must have adequate hand tools • Must have basic instrumentation: Accurate digital voltmeter with diode test mode for silicon units Clamp-on AC – DC ammeter Voltage detectors Cell phone very useful • Observe all safety precautions RECTIFIER COMPONENTS • Cabinet - protects the rectifier components from the elements • Circuit Breaker - serves as an on - off switch and overload protection • Transformer - reduces the line voltage to a useable level for the cathodic protection system and isolates the CP system from the incoming power • Rectifier Stack - used to change A.C. to D.C. (Silicon) or (Selenium) • Fuses - to protect the more expensive components (like Diodes, ACSS,etc. • Meters - used to indicate D.C. Voltage and D.C. Current • Shunts - used to accurately measure circuit current •Arrestors - protects the rectifier from voltage and lightning surges TROUBLESHOOTING - BASIC An adequate inspection and maintenance program will greatly reduce the possibility of rectifier failure. Rectifier failures do occur, however, and the field technician must know how to find and repair troubles quickly to reduce rectifier down time. MAJOR CAUSES OF RECTIFIER FAILURES 1. NEGLECT 2. AGE 3. LIGHTNING TROUBLESHOOTING PRECAUTIONS • Turn the RECTIFIER and the MAIN DISCONNECT OFF! • Be careful when testing a rectifier which is in operation. Safety first • Consult the rectifier wiring diagram before troubleshooting • Correct polarity must be observed when using DC instruments • Rectifier should be in the OFF position before using an OHMETER • Common sense prevails TROUBLESHOOTING PROCEDURES Most rectifier troubles are simple and do not require extensive detailed troubleshooting procedures. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

TRANSFORMER and INDUCTOR DESIGN HANDBOOK Third Edition, Revised and Expanded

TRANSFORMER AND INDUCTOR DESIGN HANDBOOK Third Edition, Revised and Expanded COLONEL WM. T. MCLYMAN Kg Magnetics, Inc. Idyllwild, California, U.S.A. Copyright © 2004 by Marcel Dekker, Inc. All Rights Reserved. Although great care has been taken to provide accurate and current information, neither the author(s) nor the publisher, nor anyone else associated with this publication, shall be liable for any loss, damage, or liability directly or indirectly caused or alleged to be caused by this book. The material contained herein is not intended to provide specific advice or recommendations for any specific situation. Trademark notice: Product or corporate names may be trademarks or registered trademarks and are used only for identification and explanation without intent to infringe. Library of Congress Cataloging-in-Publication Data A catalog record for this book is available from the Library of Congress. ISBN: 0-8247-5393-3 This book is printed on acid-free paper. Headquarters Marcel Dekker, Inc. 270 Madison Avenue, New York, NY 10016, U.S.A. tel: 212-696-9000; fax: 212-685-4540 Distribution and Customer Service Marcel Dekker, Inc. Cimarron Road, Monticello, New York 12701, U.S.A. tel: 800-228-1160; fax: 845-796-1772 Eastern Hemisphere Distribution Marcel Dekker AG Hutgasse 4, Postfach 812, CH-4001 Basel, Switzerland tel: 41-61-260-6300; fax: 41-61-260-6333 World Wide Web http://www.dekker.com The publisher offers discounts on this book when ordered in bulk quantities. For more information, write to Special Sales/Professional Marketing at the headquarters address above. Copyright © 2004 by Marcel Dekker, Inc. -

Aluminum Electrolytic Capacitors Power Application Capabilities

VISHAY INTERTECHNOLOGY, INC. aluMinuM electrolYtic capacitors Power Application Capabilities Aluminum Electrolytic Capacitors in Power Applications POWER APPLICATIONS • Motor Drives • Solar Inverters • Traction in trains or rolling stock • Uninterruptible Power Supply (UPS) • Pulsed Power RESOURCES • For technical questions contact [email protected] • Sales Contacts: http://www.vishay.com/doc?99914 A WORLD OF SOLUTIONS CAPABILITIES 1/11 VMN-PL0453-1610 THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000 www.vishay.com VISHAY INTERTECHNOLOGY, INC. aluMinuM electrolYtic capacitors for Motor Drives Introduction to the Application Motor drives are used to control the speed of various motors in all kinds of systems, from the small pumps and motors in household washing machines and central heating and air-conditioning systems to the large motors found in industrial machinery. Selecting the Best Capacitor for Your Motor Drive Application Aluminum capacitors are often used as DC link capacitors in motor drives, both in 1-phase and 3-phase designs. The aluminum capacitor is used as an energy buffer to ensure stable operation of the switch mode inverter driving the motor. The aluminum capacitor also functions as a filter to prevent high-frequency components from the switch mode inverter from polluting the mains voltage. The key selection criterion for the aluminum capacitor is the required ripple current. The ripple current consists of two components, a low-frequency ripple (50 Hz to 200 Hz) from the input and a high-frequency component from the inverter, typically 8 kHz to 20 kHz. -

Degradation Effect on Reliability Evaluation of Aluminum Electrolytic Capacitor in Backup Power Converter

Aalborg Universitet Degradation Effect on Reliability Evaluation of Aluminum Electrolytic Capacitor in Backup Power Converter Zhou, Dao; Wang, Huai; Blaabjerg, Frede; Kær, Søren Knudsen; Hansen, Daniel Blom Published in: Proceedings of the 2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017 - ECCE Asia) DOI (link to publication from Publisher): 10.1109/IFEEC.2017.7992443 Publication date: 2017 Document Version Accepted author manuscript, peer reviewed version Link to publication from Aalborg University Citation for published version (APA): Zhou, D., Wang, H., Blaabjerg, F., Kær, S. K., & Hansen, D. B. (2017). Degradation Effect on Reliability Evaluation of Aluminum Electrolytic Capacitor in Backup Power Converter. In Proceedings of the 2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017 - ECCE Asia) (pp. 202-207). IEEE Press. https://doi.org/10.1109/IFEEC.2017.7992443 General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ? Take down policy If you believe that this document breaches copyright please contact us at [email protected] providing details, and we will remove access to the work immediately and investigate your claim. -

Audio Transformer Design for Tube Amplifier with Improved Quality and Reduced Cost

AUDIO TRANSFORMER DESIGN FOR TUBE AMPLIFIER WITH IMPROVED QUALITY AND REDUCED COST Project Team: Evgen Pichkalyov Meltem Sevim Evgen Dzyuba Submitted to: IEEE Standard Education Committee Supervisor: Prof., D.Sc. Julia Yamnenko Faculty of Electronics, National Technical University of Ukraine “Kyiv Polytechnic Institute” (Ukraine, Kyiv) Submitted date: December 16, 2012 INTRODUCTION Audio equipment is used in many locations and facilities. Sound quality is the most important factor in any audio equipment. There are many producers (e.g. Marshall, Fender, etc.) [1] of audio equipment and systems capable of ensuring clear professional sound. As is generally the case, cost increases with quality, since higher quality means more costly components, and therefore often the only way to get a good sound is to pay a considerable amount of money. The problem of getting high sound quality at reduced cost is thus an important issue for many people all over the world. Amplifiers are among major special audio components. Tube amplifiers are the most commonly used amplifiers for professionals and sound experts. The cost of a tube amplifier mostly consists of the cost of an output transformer and tubes that is usually a factor limiting the sound quality. Audio transformer is the primary part of a tube amplifier which generates an electromagnetic field. The objective of this project is to develop an output transformer for single-ended tube amplifiers with reduced magnetic fields while preserving an adequate sound quality. IEEE C95.6-2002, 4210-2003 National Standard of Ukraine and IEEE C95.3.1-2010 on electromagnetic fields and human exposure to these fields which are important standards for human health have been used in this project.