Mcus with XLP Technology Vs. TI's MSP430

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

OMAP2430 Applications Processor

TM Technology for Innovators OMAP2430 applications processor All-in-One Key features entertainment • Advanced Imaging, Video and Audio Accelerator (IVA™ 2) boosts video for 3G mobile performance in mobile phones by up to 4X and imaging performance by up to 1.5X phones • Delivering a multimedia experience with consumer electronics quality to the handset • Multi-engine parallel processing architecture for supporting complex usage scenarios • Built-in M-Shield™ mobile security technology enables value-added services and terminal security • Support for all major High Level Operating Systems (HLOS) aids applications development PRODUCT BULLETIN Leading imaging The new OMAP2430 processor from Texas Instruments (TI) delivers a new and video level of multimedia performance to third-generation (3G) mobile phones and performance other handheld systems. Leveraging TI’s proven OMAP™ 2 architecture, the OMAP2430 features an advanced imaging, video and audio accelerator (IVA™ 2) that provides a 4X improvement in video processing and 1.5X improvement in image processing over previously available solutions for mobile phones. The processor’s high video performance enables advanced codec algorithms that promote higher compression ratios allowing networks to support more data, bringing down costs for service providers and allowing them to deploy revenue- generating services such as mobile digital TV and mobile-to-mobile gaming. Support for these services, plus high-resolution, high-speed decode of standard video compression algorithms, brings a TV-like viewing quality and the familiar features of consumer electronics to mobile communications. The OMAP2430 is optimized for the complex applications characteristic of 3G wireless communications. Offering even higher performance than first-generation OMAP 2 processors while at a lower cost, the OMAP2430 processor provides the ultimate balance between multimedia performance, flexibility, power and cost. -

Fill Your Boots: Enhanced Embedded Bootloader Exploits Via Fault Injection and Binary Analysis

IACR Transactions on Cryptographic Hardware and Embedded Systems ISSN 2569-2925, Vol. 2021, No. 1, pp. 56–81. DOI:10.46586/tches.v2021.i1.56-81 Fill your Boots: Enhanced Embedded Bootloader Exploits via Fault Injection and Binary Analysis Jan Van den Herrewegen1, David Oswald1, Flavio D. Garcia1 and Qais Temeiza2 1 School of Computer Science, University of Birmingham, UK, {jxv572,d.f.oswald,f.garcia}@cs.bham.ac.uk 2 Independent Researcher, [email protected] Abstract. The bootloader of an embedded microcontroller is responsible for guarding the device’s internal (flash) memory, enforcing read/write protection mechanisms. Fault injection techniques such as voltage or clock glitching have been proven successful in bypassing such protection for specific microcontrollers, but this often requires expensive equipment and/or exhaustive search of the fault parameters. When multiple glitches are required (e.g., when countermeasures are in place) this search becomes of exponential complexity and thus infeasible. Another challenge which makes embedded bootloaders notoriously hard to analyse is their lack of debugging capabilities. This paper proposes a grey-box approach that leverages binary analysis and advanced software exploitation techniques combined with voltage glitching to develop a powerful attack methodology against embedded bootloaders. We showcase our techniques with three real-world microcontrollers as case studies: 1) we combine static and on-chip dynamic analysis to enable a Return-Oriented Programming exploit on the bootloader of the NXP LPC microcontrollers; 2) we leverage on-chip dynamic analysis on the bootloader of the popular STM8 microcontrollers to constrain the glitch parameter search, achieving the first fully-documented multi-glitch attack on a real-world target; 3) we apply symbolic execution to precisely aim voltage glitches at target instructions based on the execution path in the bootloader of the Renesas 78K0 automotive microcontroller. -

Portfolio Holdings Listing Select Semiconductors Portfolio As of June

Portfolio Holdings Listing Select Semiconductors Portfolio DUMMY as of August 31, 2021 The portfolio holdings listing (listing) provides information on a fund’s investments as of the date indicated. Top 10 holdings information (top 10 holdings) is also provided for certain equity and high income funds. The listing and top 10 holdings are not part of a fund’s annual/semiannual report or Form N-Q and have not been audited. The information provided in this listing and top 10 holdings may differ from a fund’s holdings disclosed in its annual/semiannual report and Form N-Q as follows, where applicable: With certain exceptions, the listing and top 10 holdings provide information on the direct holdings of a fund as well as a fund’s pro rata share of any securities and other investments held indirectly through investment in underlying non- money market Fidelity Central Funds. A fund’s pro rata share of the underlying holdings of any investment in high income and floating rate central funds is provided at a fund’s fiscal quarter end. For certain funds, direct holdings in high income or convertible securities are presented at a fund’s fiscal quarter end and are presented collectively for other periods. For the annual/semiannual report, a fund’s investments include trades executed through the end of the last business day of the period. This listing and the top 10 holdings include trades executed through the end of the prior business day. The listing includes any investment in derivative instruments, and excludes the value of any cash collateral held for securities on loan and a fund’s net other assets. -

GS40 0.11-Μm CMOS Standard Cell/Gate Array

GS40 0.11-µm CMOS Standard Cell/Gate Array Version 1.0 January 29, 2001 Copyright Texas Instruments Incorporated, 2001 The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments. IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this war- ranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WAR- RANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. -

LPC47N267 Product Brief

LPC47N267 100-Pin LPC Super I/O with X-Bus Interface Product Features • Enhanced Digital Data Separator - 2 Mbps, 1 Mbps, 500 Kbps, 300 Kbps, 250 • 3.3 Volt Operation (5V tolerant) Kbps Data Rates • Programmable Wakeup Event Interface - Programmable Precompensation Modes (IO_PME# Pin) • Serial Ports • SMI Support (IO_SMI# Pin) - Two Full Function Serial Ports • GPIOs (29) - High Speed NS16C550 Compatible UARTs • Four IRQ Input Pins with Send/Receive 16-Byte FIFOs • X-Bus Interface - Supports 230k and 460k Baud - Supports up to 4 external components - Programmable Baud Rate Generator - Supports I/O cycles (No Memory Support) - Modem Control Circuitry - 8-Bit Data Transfer • Infrared Communications Controller - 16-Bit Address Qualification - IrDA v1.2 (4Mbps), HPSIR, ASKIR, Con- - Write Protection for each component sumer IR Support • XNOR Chain -2 IR Ports • PC99 and ACPI 1.0b Compliant - 96 Base I/O Address, 15 IRQ Options and 3 • 100-pin STQFP Package DMA Options • Intelligent Auto Power Management • Multi-Mode Parallel Port with ChiProtect • 2.88MB Super I/O Floppy Disk Controller - Standard Mode IBM PC/XT, PC/AT, and PS/2 - Licensed CMOS 765B Floppy Disk Controller Compatible Bidirectional Parallel Port - Software and Register Compatible with - Enhanced Parallel Port (EPP) Compatible - Microchip's Proprietary 82077AA Compatible EPP 1.7 and EPP 1.9 (IEEE 1284 Compliant) Core - IEEE 1284 Compliant Enhanced Capabilities - Supports One Floppy Drive Directly Port (ECP) - Configurable Open Drain/Push-Pull Output - ChiProtect Circuitry for -

MSP430FR2433 Mixed-Signal Microcontroller

Product Order Technical Tools & Support & Folder Now Documents Software Community MSP430FR2433 SLASE59C –OCTOBER 2015–REVISED AUGUST 2018 MSP430FR2433 Mixed-Signal Microcontroller 1 Device Overview 1.1 Features 1 • Embedded Microcontroller Storage – 16-Bit RISC Architecture – 1015 Write Cycle Endurance – Clock Supports Frequencies up to 16 MHz – Radiation Resistant and Nonmagnetic – Wide Supply Voltage Range From 3.6 V Down – High FRAM-to-SRAM Ratio, up to 4:1 to 1.8 V (Minimum Supply Voltage is Restricted • Clock System (CS) by SVS Levels, See the SVS Specifications) – On-Chip 32-kHz RC Oscillator (REFO) • Optimized Ultra-Low-Power Modes – On-Chip 16-MHz Digitally Controlled Oscillator – Active Mode: 126 µA/MHz (Typical) (DCO) With Frequency-Locked Loop (FLL) – Standby: <1 µA With VLO – ±1% Accuracy With On-Chip Reference at – LPM3.5 Real-Time Clock (RTC) Counter With Room Temperature 32768-Hz Crystal: 730 nA (Typical) – On-Chip Very Low-Frequency 10-kHz Oscillator – Shutdown (LPM4.5): 16 nA (Typical) (VLO) • High-Performance Analog – On-Chip High-Frequency Modulation Oscillator – 8-Channel 10-Bit Analog-to-Digital Converter (MODOSC) (ADC) – External 32-kHz Crystal Oscillator (LFXT) – Internal 1.5-V Reference – Programmable MCLK Prescalar of 1 to 128 – Sample-and-Hold 200 ksps – SMCLK Derived from MCLK With • Enhanced Serial Communications Programmable Prescalar of 1, 2, 4, or 8 – Two Enhanced Universal Serial Communication • General Input/Output and Pin Functionality Interfaces (eUSCI_A) Support UART, IrDA, and – Total of 19 I/Os on -

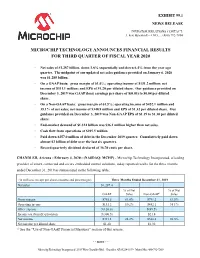

Microchip Technology Announces Financial Results for Third Quarter of Fiscal Year 2020

EXHIBIT 99.1 NEWS RELEASE INVESTOR RELATIONS CONTACT: J. Eric Bjornholt -- CFO..... (480) 792-7804 MICROCHIP TECHNOLOGY ANNOUNCES FINANCIAL RESULTS FOR THIRD QUARTER OF FISCAL YEAR 2020 ◦ Net sales of $1.287 billion, down 3.8% sequentially and down 6.4% from the year ago quarter. The midpoint of our updated net sales guidance provided on January 6, 2020 was $1.285 billion. ◦ On a GAAP basis: gross margin of 61.0%; operating income of $131.2 million; net income of $311.1 million; and EPS of $1.20 per diluted share. Our guidance provided on December 3, 2019 was GAAP (loss) earnings per share of $(0.03) to $0.04 per diluted share. ◦ On a Non-GAAP basis: gross margin of 61.5%; operating income of $452.1 million and 35.1% of net sales; net income of $340.8 million and EPS of $1.32 per diluted share. Our guidance provided on December 3, 2019 was Non-GAAP EPS of $1.19 to $1.30 per diluted share. ◦ End-market demand of $1.324 billion was $36.1 million higher than net sales. ◦ Cash flow from operations of $395.5 million. ◦ Paid down $257.0 million of debt in the December 2019 quarter. Cumulatively paid down almost $2 billion of debt over the last six quarters. ◦ Record quarterly dividend declared of 36.70 cents per share. CHANDLER, Arizona - February 4, 2020 - (NASDAQ: MCHP) - Microchip Technology Incorporated, a leading provider of smart, connected and secure embedded control solutions, today reported results for the three months ended December 31, 2019 as summarized in the following table: (in millions, except per share amounts and percentages) Three Months Ended December 31, 2019 Net sales $1,287.4 % of Net % of Net GAAP Sales Non-GAAP1 Sales Gross margin $785.5 61.0% $791.2 61.5% Operating income $131.2 10.2% $452.1 35.1% Other expense $(120.6) $(89.5) Income tax (benefit) provision $(300.5) $21.8 Net income $311.1 24.2% $340.8 26.5% Net income per diluted share $1.20 $1.32 (1) See the "Use of Non-GAAP Financial Measures" section of this release. -

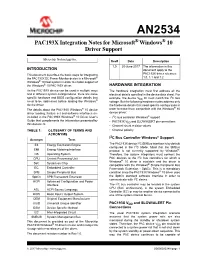

AN2534 PAC193X Integration Notes for Microsoft® Windows® 10 Driver Support Author: Razvan Ungureanu TABLE 2: REVISION HISTORY Microchip Technology Inc

AN2534 PAC193X Integration Notes for Microsoft® Windows® 10 Driver Support Author: Razvan Ungureanu TABLE 2: REVISION HISTORY Microchip Technology Inc. Rev# Date Description 1.0 20-June-2017 The information in this INTRODUCTION document apply to the This document describes the basic steps for integrating PAC193X driver releases: the PAC193X DC Power Monitor device in a Microsoft® 1.0, 1.1 and 1.2 Windows® 10 host system in order to enable support of the Windows® 10 PAC193X driver. HARDWARE INTEGRATION As the PAC193X device can be used in multiple ways The hardware integration must first address all the and in different system configurations, there are some electrical details specified in the device data sheet. For 2 specific hardware and BIOS configuration details that example, the device VDD IO must match the I C bus need to be addressed before loading the Windows® voltage. But the following hardware notes address only device driver. the hardware details that need specific configuration in ® The details about the PAC193X Windows® 10 device order to make them compatible with the Windows 10 driver loading, feature set and software interfaces are device driver: included in the PAC193X Windows® 10 Driver User’s •I2C bus controller Windows® support Guide that complements the information presented by • PAC193X VDD and SLOW/ALERT pin connections this document. • Channel shunt resistor values . TABLE 1: GLOSSARY OF TERMS AND • Channel polarity ACRONYMS I2C Bus Controller Windows® Support Acronym Term 2 E3 Energy Estimation Engine The PAC193X device I C/SMBus interface is by default configured in the I2C Mode. Mind that the SMBus EMI Energy Metering Interface protocol is not currently supported by Windows®. -

Integrated Step-Down Converter with SVID Interface for Intel® CPU

Product Order Technical Tools & Support & Folder Now Documents Software Community TPS53820 SLUSE33 –FEBRUARY 2020 Integrated Step-Down Converter with SVID Interface for Intel® CPU Power Supply 1 Features 3 Description The TPS53820 device is D-CAP+ mode integrated 1• Single chip to support Intel VR13.HC SVID POL applications step-down converter for low current SVID rails of Intel CPU power supply. It provides up to two outputs to • Two outputs to support VCCANA (5.5 A) and power the low current SVID rails such as VCCANA P1V8 (4 A) (5.5 A) and P1V8 (4 A). The device employs D-CAP+ • D-CAP+™ Control for Fast Transient Response mode control to provide fast load transient • Wide Input Voltage (4.5 V to 15 V) performance. Internal compensation allows ease of use and reduces external components. • Differential Remote Sense • Programmable Internal Loop Compensation The device also provides telemetry, including input voltage, output voltage, output current and • Per-Phase Cycle-by-Cycle Current Limit temperature reporting. Over voltage, over current and • Programmable Frequency from 800 kHz to 2 MHz over temperature protections are provided as well. 2 • I C System Interface for Telemetry of Voltage, The TPS53820 device is packaged in a thermally Current, Output Power, Temperature, and Fault enhanced 35-pin QFN and operates between –40°C Conditions and 125°C. • Over-Current, Over-Voltage, Over-Temperature (1) protections Table 1. Device Information • Low Quiescent Current PART NUMBER PACKAGE BODY SIZE (NOM) • 5 mm × 5 mm, 35-Pin QFN, PowerPAD Package TPS53820 RWZ (35) 5 mm × 5 mm (1) For all available packages, see the orderable addendum at 2 Applications the end of the data sheet. -

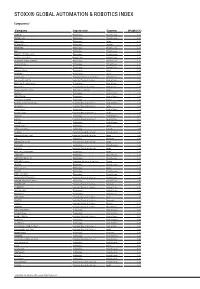

Stoxx® Global Automation & Robotics Index

STOXX® GLOBAL AUTOMATION & ROBOTICS INDEX Components1 Company Supersector Country Weight (%) SNAP 'A' Technology United States 4.24 NVIDIA Corp. Technology United States 2.80 Nidec Corp. Technology Japan 2.42 HEXAGON B Technology Sweden 2.38 TERADYNE Technology United States 2.31 KLA Technology United States 2.23 MARVELL TECHNOLOGY Technology United States 2.16 Intuitive Surgical Inc. Health Care United States 2.12 ADVANCED MICRO DEVICES Technology United States 2.12 Qualcomm Inc. Technology United States 2.09 Apple Inc. Technology United States 2.06 Advantest Corp. Technology Japan 2.05 LASERTEC Technology Japan 2.04 Garmin Ltd. Consumer Products & Services United States 2.02 Emerson Electric Co. Industrial Goods & Services United States 2.02 Microchip Technology Inc. Technology United States 1.98 Ametek Inc. Industrial Goods & Services United States 1.96 Toyota Industries Corp. Automobiles & Parts Japan 1.96 Xilinx Inc. Technology United States 1.95 SERVICENOW Technology United States 1.88 DASSAULT SYSTEMS Technology France 1.82 Rockwell Automation Corp. Industrial Goods & Services United States 1.74 Fanuc Ltd. Industrial Goods & Services Japan 1.74 Autodesk Inc. Technology United States 1.68 Keyence Corp. Industrial Goods & Services Japan 1.63 Ansys Inc. Technology United States 1.61 HALMA Industrial Goods & Services Great Britain 1.56 PTC INC Technology United States 1.53 Omron Corp. Technology Japan 1.52 OPEN TEXT (NAS) Technology Canada 1.49 COGNEX Industrial Goods & Services United States 1.48 Yaskawa Electric Corp. Industrial Goods & Services Japan 1.40 SAP Technology Germany 1.40 MINEBEA MITSUMI Industrial Goods & Services Japan 1.24 Intel Corp. -

MCP3426/7/8 16-Bit, Multi-Channel ΔΣ Analog-To-Digital Converter with I2C™ Interface and On-Board Reference

MCP3426/7/8 16-Bit, Multi-Channel ΔΣ Analog-to-Digital Converter with I2C™ Interface and On-Board Reference Features Description • 16-bit ΔΣ ADC with Differential Inputs: The MCP3426, MCP3427 and MCP3428 devices - 2 channels: MCP3426 and MCP3427 (MCP3426/7/8) are the low noise and high accuracy - 4 channels: MCP3428 16 Bit Delta-Sigma Analog-to-Digital (ΔΣ A/D) Con- verter family members of the MCP342X series from • Differential Input Full Scale Range: -V to REF Microchip Technology Inc. These devices can convert +V REF analog inputs to digital codes with up to 16 bits of reso- • Self Calibration of Internal Offset and Gain per lution. Each Conversion The MCP3426 and MCP3427 devices have two • On-Board Voltage Reference (V ): REF differential input channels and the MCP3428 has four - Accuracy: 2.048V ± 0.05% differential input channels. All electrical properties of - Drift: 15 ppm/°C these three devices are the same except the • On-Board Programmable Gain Amplifier (PGA): differences in the number of input channels and I2C - Gains of 1,2, 4 or 8 address bit selection options. • INL: 10 ppm of Full Scale Range These devices can output analog-to-digital conversion • Programmable Data Rate Options: results at rates of 15 (16-bit mode), 60 (14-bit mode), or 240 (12-bit mode) samples per second depending on - 15 SPS (16 bits) the user controllable configuration bit settings using the - 60 SPS (14 bits) two-wire I2C serial interface. During each conversion, - 240 SPS (12 bits) the device calibrates offset and gain errors • One-Shot or Continuous Conversion Options automatically. -

PICMASTER™ Support of Microsoft ® Windows™

PICMASTER Support of Microsoft Windows DDE AN584 PICMASTER™ Support of Microsoft® Windows™ DDE The PICMASTER system supports Windows Dynamic 5. You will see the trace buffer fill with instructions and Data Exchange (DDE). This feature allows the contents data if those instructions were executed and trace of the trace buffer to be transferred to other windows enabled. If you do not see any instructions in the applications such as Microsoft Excel™. This feature is trace buffer, check the Trace Settings in (1) and look invaluable to control systems designers who would like for loops or deadlock situations that would prevent to plot real-time data to debug and fine tune an applica- your program from executing these instructions. tion. This application note will show how to set this up Note: PICMASTER must be running and the trace and graph system data. buffer open with data displaying in order to use DDE for other Windows applications (such as THE TRACE BUFFER Microsoft Excel as described in the next section). The PICMASTER contains a 8K x 40 bit trace buffer. The fields within this buffer are broken up into three SETTING UP EXCEL categories: After starting Excel with a blank spread sheet, select 100 (1) Current Address of instruction 16-Bits (ADDRESS) rows in the first column by pressing the left mouse button (2) Data/Opcode Field 16-Bits (DATA) and holding it down to drag across all cells. Next Type the following string in the box: (3) External Logic Analyzer inputs 8-Bits (EXT) 5 ————— =PICMASTR|’c:\path\test.hex’!’data 0 99’ 40-Bits and hit CNTRL+SHIFT+ENTER Any instruction can be optionally traced or not traced; the The format for this command is as follows: trace for each instruction is enabled by the “T” field on the =PICMASTR|’<hex_file>‘!’<string> far left column of the program memory dump window.