Cocotb: a Python-Based Digital Logic Verification Framework

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Federation Toolflow

Federation: Open Source SoC Design Methodology Jack Koenig, Staff Engineer Aug 3, 2019 Hardware Trends: Compute Needs are Changing e.g., machine learning But, CPUs are not getting faster! Source: Medium, Entering the world of Machine Learning 2 Hardware Trends: Custom Hardware to the Rescue! Custom Chips But, custom chip development GPUs (e.g., Google TPU) costs are too high! 3 How did turn into a $1B acquisition with only 13 employees?* 4 * https://www.sigarch.org/open-source-hardware-stone-soups-and-not-stone-statues-please Why do silicon projects need experts from at least 14+ disciplines just to get started? 6 <Your Name Here> Tech Stack Tech Stack Readily-Available Reusable Technology from techstacks.io Federation Tools Infrastructure Cloud Services 7 We Should Copy “Innovations” from the Software Industry open-source standards abstraction and code reuse composability and APIs productivity tooling commodity infrastructure 8 npm Enables Modular Web Development with Reusable Packages 9 Source: https://go.tiny.cloud/blog/a-guide-to-npm-the-node-js-package-manager/ npm Enables Javascript as Most Popular Programming Language • 830.000 of packages • 10 million users • 30 billion packages downloads per month • 90% of Web built of NPM packages • NPM used everywhere: client, server, mobile, IoT • Open source libraries availability is the major driving force for Language adoption [Leo2013] proven by NPM • 70+ programming languages can be transpiled into JS, WebAssembly and published on NPM 10 Federation: the action of forming states or organizations into a single group with centralized control, within which smaller divisions have some degree of internal autonomy 11 Federation: a suite of open-source tools that SiFive is using to orchestrate modular SoC design workflows 12 Federation Tools Enable a Modular SoC Design Methodology Federation Tools IP Package 1 IP Package 2 IP Package 3 1. -

The Early History of Smalltalk

The Early History of Smalltalk http://www.accesscom.com/~darius/EarlyHistoryS... The Early History of Smalltalk Alan C. Kay Apple Computer [email protected]# Permission to copy without fee all or part of this material is granted provided that the copies are not made or distributed for direct commercial advantage, the ACM copyright notice and the title of the publication and its date appear, and notice is given that copying is by permission of the Association for Computing Machinery. To copy otherwise, or to republish, requires a fee and/or specific permission. HOPL-II/4/93/MA, USA © 1993 ACM 0-89791-571-2/93/0004/0069...$1.50 Abstract Most ideas come from previous ideas. The sixties, particularly in the ARPA community, gave rise to a host of notions about "human-computer symbiosis" through interactive time-shared computers, graphics screens and pointing devices. Advanced computer languages were invented to simulate complex systems such as oil refineries and semi-intelligent behavior. The soon-to- follow paradigm shift of modern personal computing, overlapping window interfaces, and object-oriented design came from seeing the work of the sixties as something more than a "better old thing." This is, more than a better way: to do mainframe computing; for end-users to invoke functionality; to make data structures more abstract. Instead the promise of exponential growth in computing/$/volume demanded that the sixties be regarded as "almost a new thing" and to find out what the actual "new things" might be. For example, one would compute with a handheld "Dynabook" in a way that would not be possible on a shared mainframe; millions of potential users meant that the user interface would have to become a learning environment along the lines of Montessori and Bruner; and needs for large scope, reduction in complexity, and end-user literacy would require that data and control structures be done away with in favor of a more biological scheme of protected universal cells interacting only through messages that could mimic any desired behavior. -

Co-Simulation Between Cλash and Traditional Hdls

MASTER THESIS CO-SIMULATION BETWEEN CλASH AND TRADITIONAL HDLS Author: John Verheij Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS) Computer Architecture for Embedded Systems (CAES) Exam committee: Dr. Ir. C.P.R. Baaij Dr. Ir. J. Kuper Dr. Ir. J.F. Broenink Ir. E. Molenkamp August 19, 2016 Abstract CλaSH is a functional hardware description language (HDL) developed at the CAES group of the University of Twente. CλaSH borrows both the syntax and semantics from the general-purpose functional programming language Haskell, meaning that circuit de- signers can define their circuits with regular Haskell syntax. CλaSH contains a compiler for compiling circuits to traditional hardware description languages, like VHDL, Verilog, and SystemVerilog. Currently, compiling to traditional HDLs is one-way, meaning that CλaSH has no simulation options with the traditional HDLs. Co-simulation could be used to simulate designs which are defined in multiple lan- guages. With co-simulation it should be possible to use CλaSH as a verification language (test-bench) for traditional HDLs. Furthermore, circuits defined in traditional HDLs, can be used and simulated within CλaSH. In this thesis, research is done on the co-simulation of CλaSH and traditional HDLs. Traditional hardware description languages are standardized and include an interface to communicate with foreign languages. This interface can be used to include foreign func- tions, or to make verification and co-simulation possible. Because CλaSH also has possibilities to communicate with foreign languages, through Haskell foreign function interface (FFI), it is possible to set up co-simulation. The Verilog Procedural Interface (VPI), as defined in the IEEE 1364 standard, is used to set-up the communication and to control a Verilog simulator. -

Object-Oriented Programming in the Beta Programming Language

OBJECT-ORIENTED PROGRAMMING IN THE BETA PROGRAMMING LANGUAGE OLE LEHRMANN MADSEN Aarhus University BIRGER MØLLER-PEDERSEN Ericsson Research, Applied Research Center, Oslo KRISTEN NYGAARD University of Oslo Copyright c 1993 by Ole Lehrmann Madsen, Birger Møller-Pedersen, and Kristen Nygaard. All rights reserved. No part of this book may be copied or distributed without the prior written permission of the authors Preface This is a book on object-oriented programming and the BETA programming language. Object-oriented programming originated with the Simula languages developed at the Norwegian Computing Center, Oslo, in the 1960s. The first Simula language, Simula I, was intended for writing simulation programs. Si- mula I was later used as a basis for defining a general purpose programming language, Simula 67. In addition to being a programming language, Simula1 was also designed as a language for describing and communicating about sys- tems in general. Simula has been used by a relatively small community for many years, although it has had a major impact on research in computer sci- ence. The real breakthrough for object-oriented programming came with the development of Smalltalk. Since then, a large number of programming lan- guages based on Simula concepts have appeared. C++ is the language that has had the greatest influence on the use of object-oriented programming in industry. Object-oriented programming has also been the subject of intensive research, resulting in a large number of important contributions. The authors of this book, together with Bent Bruun Kristensen, have been involved in the BETA project since 1975, the aim of which is to develop con- cepts, constructs and tools for programming. -

Pyvsc: Systemverilog-Style Constraints and Coverage in Python

PyVSC: SystemVerilog-Style Constraints, and Coverage in Python M. Ballance Milwaukie, OR, USA [email protected] Abstract—Constrained-randomization and functional Coverage is captured as a set of individual coverpoint coverage are key elements in the widely-used SystemVerilog-based instances, and is not organized into covergroup types and verification flow. The use of Python in functional verification is instances in the same way that SystemVerilog does. growing in popularity, but Python has historically lacked support for the constraint and coverage features provided by B. SystemC SystemVerilog. This paper describes PyVSC, a library that SystemC has been one of the longer-lasting languages used provides these features. for modeling and verifying hardware that is built as an embedded domain-specific language within a general-purpose Keywords—functional verification, Python, constrained programming language (C++). While libraries for constraints random, functional coverage and coverage targeting SystemC are not directly applicable in I. INTRODUCTION Python, it’s worthwhile considering approaches taken. Verification flows based on constrained-random stimulus The SystemC Verification Library (SCV) provides basic generation and functional coverage collection have become randomizations and constraints, using a Binary Decision dominant where SystemVerilog is used for the testbench Diagram (BDD) solver. BDD-based constraint solvers are environment. Consequently, verification engineers have known to have performance and capacity challenges, especially significant experience with the constructs and patterns provided with sizable constraint spaces. No support for capturing by SystemVerilog. functional coverage is provided. There is growing interest in making use of Python in The CRAVE [4] library sought to bring higher performance verification environments – either as a complete verification and capacity to randomization in SystemC using Satifiability environment or as an adjunct to a SystemVerilog verification Modulo Theories (SMT) constraint solvers. -

PGAS Communication for Heterogeneous Clusters with Fpgas

PGAS Communication for Heterogeneous Clusters with FPGAs by Varun Sharma A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto © Copyright 2020 by Varun Sharma Abstract PGAS Communication for Heterogeneous Clusters with FPGAs Varun Sharma Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto 2020 This work presents a heterogeneous communication library for generic clusters of processors and FPGAs. This library, Shoal, supports the partitioned global address space (PGAS) memory model for applications. PGAS is a shared memory model for clusters that creates a distinction between local and remote memory accesses. Through Shoal and its common application programming interface for hardware and software, applications can be more freely migrated to the optimal platform and deployed onto dynamic cluster topologies. The library is tested using a thorough suite of microbenchmarks to establish latency and throughput performance. We also show an implementation of the Jacobi method that demonstrates the ease with which applications can be moved between platforms to yield faster run times. ii Acknowledgements It takes a village to raise a child and about as many people to raise a thesis as well. Foremost, I would like to thank my supervisor, Paul Chow, for all that he’s done for me over the course of the four years that I’ve known him thus far. Thank you for accepting me as your student for my undergraduate thesis and not immediately rejecting me when I asked to pursue a Masters under your supervision as well. -

CPS323 Lecture: Concurrency Materials: 1. Coroutine Projectables

CPS323 Lecture: Concurrency Materials: 1. Coroutine Projectables 2. Handout for Ada Concurrency + Executable form (simple_tasking.adb, producer_and_consumer.adb) I. Introduction - ------------ A. Most of our attention throughout the CS curricum has been focussed on _sequential_ programming, in which a program does exactly one thing at a time, following a predictable order of steps. In particular, we expect a given program will always follow the exact same sequence of steps when run on a given set of data. B. An alternative is to think in terms of _concurrent_ programming, in which a "program" (at least in principle) does multiple things at the same time, following an order of steps that is not predictable and may differ between runs even if the same program is run on exactly the same data. C. Concurrency has long been an interest in CS, but has become of particular interest as we move into a situation in which raw hardware speeds have basically plateaued and multicore processors are coming to dominate the hardware scene. There are at least three reasons why this topic is of great interest. 1. Achieving maximum performance using technologies such as multicore processors. 2. Systems that inherently require multiple processors working together cooperatively on a single task - e.g. distributed or embedded systems. 3. Some problems are more naturally addressed by thinking in terms of multiple concurrrent components, rather than a single monolithic program. D. There are two broad approaches that might be taken to concurrency: 1. Make use of system libraries, without directly supporting parallelism in the language. (The approach taken by most languages - e.g. -

A Low-Cost Implementation of Coroutines for C

University of Wollongong Research Online Department of Computing Science Working Faculty of Engineering and Information Paper Series Sciences 1983 A low-cost implementation of coroutines for C Paul A. Bailes University of Wollongong Follow this and additional works at: https://ro.uow.edu.au/compsciwp Recommended Citation Bailes, Paul A., A low-cost implementation of coroutines for C, Department of Computing Science, University of Wollongong, Working Paper 83-9, 1983, 24p. https://ro.uow.edu.au/compsciwp/76 Research Online is the open access institutional repository for the University of Wollongong. For further information contact the UOW Library: [email protected] A LOW-COST IMPLEMENTATION OF COROUTINES FOR C Paul A. Bailes Department of Computing Science University of Wollongong Preprint No. 83-9 November 16, 1983 P.O. Box 1144, WOLLONGONG N.S.W. 2500, AUSTRALIA tel (042)-282-981 telex AA29022 A Low-Cost Implementation of Coroutines for C Paul A. Bailes Department of Computing Science University of Wollongong Wollongong N.S.W. 2500 Australia ABSTRACT We identify a set of primitive operations supporting coroutines, and demonstrate their usefulness. We then address their implementation in C accord ing to a set of criteria aimed at maintaining simplicity, and achieve a satisfactory compromise between it and effectiveness. Our package for the PDP-II under UNIXt allows users of coroutines in C programs to gain access to the primitives via an included definitions file and an object library; no penalty is imposed upon non-coroutine users. October 6, 1983 tUNIX is a Trademark of Bell Laboratories. A Low-Cost Implementation of Coroutines for C Paul A. -

Lastlayer:Towards Hardware and Software Continuous Integration

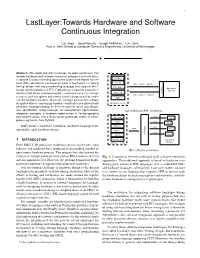

1 LastLayer:Towards Hardware and Software Continuous Integration Luis Vega, Jared Roesch, Joseph McMahan, Luis Ceze. Paul G. Allen School of Computer Science & Engineering, University of Washington F Abstract—This paper presents LastLayer, an open-source tool1 that enables hardware and software continuous integration and simulation. Python Compared to traditional testing approaches based on the register transfer Scala level (RTL) abstraction, LastLayer provides a mechanism for testing RTL input signals Python Verilog designs with any programming language that supports the C RTL DSLs hardware foreign function interface (CFFI). Furthermore, it supports a generic C Scala RTL input signals design Verilog ports interface that allows external programs convenient access to storage RTL DSLs RTL output signals hardware resources such as registers and memories in the design as well as control design VHDL ports over the hardware simulation. Moreover, LastLayer achieves this software Verilog RTL output signals hardware tests integration without requiring any hardware modification and automatically VHDL generates language bindings for these storage resources according to user specification. Using LastLayer, we evaluated two representative hardware tests Python (a) Traditional RTL simulationDPI integration examples: a hardware adder written in Verilog operating reg_a Java DPIDPI over NumPy arrays, and a ReLu vector-accelerator written in Chisel Python reg_amem_a processing tensors from PyTorch. Racket Java DPIDPI CFFI mem_a mem_b Index terms— hardware simulation, hardware language inter- HaskellRacket DPI CFFI DPI mem_b LastLayer reg_b operability, agile hardware design HaskellRust DPI LastLayer reg_b JavaScriptRust hardware design 1 INTRODUCTION softwareJavaScript tests hardware design software tests From RISC-V [9] processors to domain-specific accelerators, both industry and academia have produced an outstanding number of (b) LastLayer simulation open-source hardware projects. -

Kotlin Coroutines Deep Dive Into Bytecode #Whoami

Kotlin Coroutines Deep Dive into Bytecode #whoami ● Kotlin compiler engineer @ JetBrains ● Mostly working on JVM back-end ● Responsible for (almost) all bugs in coroutines code Agenda I will talk about ● State machines ● Continuations ● Suspend and resume I won’t talk about ● Structured concurrency and cancellation ● async vs launch vs withContext ● and other library related stuff Agenda I will talk about Beware, there will be code. A lot of code. ● State machines ● Continuations ● Suspend and resume I won’t talk about ● Structured concurrency and cancellation ● async vs launch vs withContext ● and other library related stuff Why coroutines ● No dependency on a particular implementation of Futures or other such rich library; ● Cover equally the "async/await" use case and "generator blocks"; ● Make it possible to utilize Kotlin coroutines as wrappers for different existing asynchronous APIs (such as Java NIO, different implementations of Futures, etc). via coroutines KEEP Getting Lazy With Kotlin Pythagorean Triples fun printPythagoreanTriples() { for (i in 1 until 100) { for (j in 1 until i) { for (k in i until 100) { if (i * i + j * j < k * k) { break } if (i * i + j * j == k * k) { println("$i^2 + $j^2 == $k^2") } } } } } Pythagorean Triples fun printPythagoreanTriples() { for (i in 1 until 100) { for (j in 1 until i) { for (k in i until 100) { if (i * i + j * j < k * k) { break } if (i * i + j * j == k * k) { println("$i^2 + $j^2 == $k^2") } } } } } Pythagorean Triples fun printPythagoreanTriples() { for (i in 1 until 100) { for (j -

Csc 520 Principles of Programming Languages Coroutines Coroutines

Coroutines Coroutines are supported by Simula and Modula-2. CSc 520 They are similar to Java’s threads, except the programmer has to explicitly transfer control from one Principles of Programming execution context to another. Languages Thus, like threads several coroutines can exist simultaneously but unlike threads there is no central 36: Procedures — Coroutines scheduler that decides which coroutine should run next. Christian Collberg A coroutine is represented by a closure. [email protected] A special operation transfer(C) shifts control to the coroutine C, at the location where C last left off. Department of Computer Science University of Arizona Copyright c 2005 Christian Collberg 520—Spring 2005—36 [1] 520—Spring 2005—36 [2] Coroutines. Coroutines. The next slide shows an example from Scott where two var us, cfs: coroutine; coroutines execute “concurrently”, by explicitly transferring control between each other. coroutine update_screen() { ... In the example one coroutine displays a moving detach screen-saver, the other walks the file-system to check loop { for corrupt files. ... transfer(cfs) ... } } coroutine check_file_system() { ... } main () { ... } 520—Spring 2005—36 [3] 520—Spring 2005—36 [4] Coroutines. Coroutines in Modula-2 coroutine check_file_system() { Modula-2's system module provides two functions to create and transfer ... between coroutines: detach for all files do { PROCEDURE NEWPROCESS( proc: PROC; (* The procedure *) ... transfer(cfs) addr: ADDRESS; (* The stack *) ... transfer(cfs) size: CARDINAL; (* The stack size *) ... transfer(cfs) ... VAR new: ADDRESS); (* The coroutine *) } PROCEDURE TRANSFER( } VAR source: ADDRESS; (* Current coroutine *) VAR destination: ADDRESS); (* New coroutine *) main () { us := new update_screen(); The ®rst time TRANSFER is called source will be instantiated to cfs := new check_file_system(); the main (outermost) coroutine. -

Practical Perl Tools Parallel Asynchronicity, Part 2

COLUMNS Practical Perl Tools Parallel Asynchronicity, Part 2 DAVID N. BLANK-EDELMAN David Blank-Edelman is elcome back for Part 2 of this mini-series on modern methods the Technical Evangelist at for doing multiple things at once in Perl. In the first part (which I Apcera (the comments/ highly recommend that you read first before reading this sequel), views here are David’s alone W and do not represent Apcera/ we talked about some of the simpler methods for multi-tasking like the use Ericsson) . He has spent close to thirty years of fork() and Parallel::ForkManager. We had just begun to explore using the in the systems administration/DevOps/SRE Coro module as the basis for using threads in Perl (since the native stuff is so field in large multiplatform environments ucky) when we ran out of time. Let’s pick up the story roughly where we left it. including Brandeis University, Cambridge Technology Group, MIT Media Laboratory, Coro and Northeastern University. He is the author As a quick reminder, Coro offers an implementation of coroutines that we are going to use as of the O’Reilly Otter book Automating System just a pleasant implementation of cooperative threading (see the previous column for more Administration with Perl and is a frequent invited picayune details around the definition of a coroutine). By cooperative, we mean that each speaker/organizer for conferences in the field. thread gets queued up to run, but can only do so after another thread has explicitly signaled David is honored to serve on the USENIX that it is ready to cede its time in the interpreter.