AU9360 USB Multiple Slots Flash Memory Card Reader Controller TRM

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Memory Card Reader • USB 3.0 Cable Compactflash (CF) Card • Quick Setup Guide Insert Label Side Up

Front view LED indicator QUICK SETUP GUIDE Memory Card microSD, microSDXC Reader Insert label side up. NS-DCR30D3K / NS-DCR30D3K-C SD card Insert label side up. PACKAGE CONTENTS • USB 3.0 multi-format memory card reader • USB 3.0 cable CompactFlash (CF) card • Quick Setup Guide Insert label side up. SYSTEM REQUIREMENTS Back view • Windows® 10, Windows® 8.1, Windows® 8, Windows® 7, Windows Vista®, Mac OS 9.0 or higher, or Linux Kernal 2.4.1 or above FEATURES • Supports USB 3.0 and below • Multi-port and multi-driver letter display USB cable port • Plug & Play • Works with the following card formats: Micro SD/T-FLASH/Micro SDXC/Micro SDHC, SD/SDHC/SDXC/ Mini-SD, CompactFlash (CF) type I Caution: All cards must be inserted into the card reader label side up. Failure to do so could result in damage to the memory card or the card reader. Do not force a memory card into the card reader. Before using your new product, please read these instructions to prevent any damage. CONNECTING THE CARD READER 5 Do not remove your card from the card reader until the data LED Plug one end of a USB cable into the USB port of the card reader and stops blinking and the name of your card disappears from the Finder the other end into an available USB port on your computer. Your window. computer loads the drivers automatically. SPECIFICATIONS USING THE CARD READER • Dimensions: 2.87 × 1.98 × .68 in. (7.3 × 5.05 × 1.75 cm) Cautions: • Transmission port: USB 3.0 • Insert a card, label side up, into the appropriate slot. -

GFR209 Datasheet

GFR209 12-in-1 Pocket Card Reader/Writer IOGEAR's 12-in-1 Pocket Card Reader / Writer is an ideal solution for hi-speed, bi-directional image and data file transfer between your computer and multimedia devices. Images and data can be downloaded directly to your PC or Mac from your memory cards without using additional adapters. It works with 12 popular memory card formats such as SD, SDXC, microSD, microSDXC, Mini SD, MMC, Memory Stick, and MS Duo. With direct USB 2.0 high-speed file transfer (up to 480Mbps) from memory cards used in your cell phone, MP3 player, or digital camera, you can save time and conserve power on devices. It instantly transfers your slotMusic™ songs to your PC or Mac. No matter where you go, IOGEAR's 12-in-1 Pocket Card Reader / Writer helps you to easily bring your digital images and data with you. 3-Slot,(Max) Suport memory card SDHC (32GB) / Mini SDHC (4GB) / SDXC (64GB) / MMC(4GB) Micro SDXC (64GB) / M2 (16GB / need adapter) MS (16GB) Compliant with USB 2.0 specification Backward compatible with USB 1.1 specification Supports SDXC (Secure Digital High Capacity) and microSDXC cards Plug-n-Play, Hot swappable, and Hot pluggable up to 64GB Reads / Writes microSD / microSDXC / T-Flash, SD/SDXC, mini SD, Fast data transfer - up to 480 Mbps, between your cell phone / MMC, MMC Plus, RS-MMC, MMC Mobile, MS, MS Pro, MS Duo, MS smartphone / PDA and computers Pro Duo Requirements Package Contents For PC Users 1 x Card Reader/Writer • Windows XP, Windows Vista, Windows 7, Windows 8/8.1, 10 1 x Quick Start Guide • Available USB 2.0 port • Chrome Book • Linux®, Unix and other USB supported systems* *Additional drivers and support may be needed For MAC Users • Mac 8.6 or greater. -

Memory Card Reader/Writer

Memory Card Reader/Writer USER MANUAL Thank you for purchasing a PROMASTER® Memory Card Reader/Writer. The PROMASTER® Memory Card Reader/Writer lets you access your pictures or other files from a memory card without the need to directly connect a camera or other media device to your computer. Follow the simple instructions in this user manual and enjoy the benefits of these convenient features: • Easily access media and manage content almost anywhere Supports automatic card detection and high speed data transfer Eliminates need for direct connection of media device to save battery power Windows and Mac compatible — hot swappable, Plug and Play INSTALLATION Using the included USB cable, connect the Reader/Writer to a USB port on your computer. Double-click on "My Computer" to confirm that a drive letter labeled Removable Disk appears. Check that the internal blue power LED lights confirming a proper connection. Insert your memory card in the reader slot to use the card reader function. Double-click on the Removable Disk drive letter to read or write desired files to or from your computer or storage card. OPERATIONS GUIDE OVERVIEW The read and write commands for memory cards are the same as those used for moving data to and from any other computer storage device, such as a USB drive or floppy disk. You simply plug the PROMASTER® Reader/Writer into any USB port of your PC or Mac and begin transferring information stored on flash media cards to your computer and back. OPERATING TIPS Using Compact Flash (CF I and II) & Microdrive Reader When inserting cards, the side with the holes should face the card slot on the PROMASTER® reader. -

Targus Flash Memory Card Reader User's Guide

Targus Flash Memory Card Reader for Notebook Computers Making Your Mobile Life Easier. USER’S GUIDE Visit our Web site at: www.targus.com Making Your Mobile Life Easier. Features and specifications are subject to change without notice. © 2001 Targus Corp. 400-0055-001A BRUSSELS HANNOVER BARCELONA TOKYO MILANO AMSTERDAM SINGAPORE LONDON PARIS NEW YORK LOS ANGELES TORONTO HONG KONG SYDNEY 2 Targus Memory Card Reader Introduction Thank you for purchasing the Targus Memory Card Reader. Lightweight and ultra-portable, the reader runs off your computer’s power supply and enables you to transfer data from supported memory media to your computer. Devices that use memory media include a digital camera, personal organizer, voice recorder, MP3 player, Personal Digital Assistant (PDA), or handheld computer. See “Supported Media Formats” on page 11 for a list of compatible media. After installing the driver software, you can use the reader at any time by plugging in its Universal Serial Bus (USB) connector to your computer’s USB port. You can also use the reader with the supplied USB extension cable to increase the cable length. In addition to this user’s guide, this package contains: • Targus Memory Card Reader • Driver software diskette • USB extension cable Targus Memory Card Reader 3 System Requirements To use the Targus Memory Card Reader, your computer must meet the following hardware requirements and run one of the operating systems listed in the table below. Hardware Operating System • PC with a Pentium® • Windows® 98/Me/ processor or equivalent 2000/XP and a hard disk drive • USB interface • Standard diskette drive Installing the Targus Memory Card Reader Driver Software NOTE: The Windows® Me/XP operating systems support the Plug and Play operation. -

USB 3.0 Multi-Format Memory Card Reader NS-DCR30A2/NS-DCR30A2-C

NS-DCR30A2-NS-DCR30A2-C_15-0446_MAN_V2_ENG.fm Page 1 Tuesday, June 2, 2015 9:22 AM USER GUIDE USB 3.0 Multi-Format Memory Card Reader NS-DCR30A2/NS-DCR30A2-C Before using your new product, please read these instructions to prevent any damage. NS-DCR30A2-NS-DCR30A2-C_15-0446_MAN_V2_ENG.fm Page 2 Tuesday, June 2, 2015 9:22 AM NS-DCR30A2/NS-DCR30A2-C Multi-Format Memory Card Reader NS-DCR30A2/NS-DCR30A2-C Multi-Format Memory Card Reader Contents Welcome . .2 Features . .2 Important safety instructions . .3 Card reader components . .3 Package contents . .3 Minimum system requirements . .3 Front and back view . .4 Card slots. .5 Using your card reader . .6 Connecting your card reader . .6 Data LED . .7 Formatting a memory card in Windows . .7 Formatting a memory card with Macintosh . .8 Troubleshooting . .8 Specifications . .9 Legal notices. .10 ONE-YEAR LIMITED WARRANTY - INSIGNIA . .11 Welcome Congratulations on your purchase of a high-quality Insignia product. Your NS-DCR30A2/NS-DCR30A2-C memory card reader represents the state-of-the-art in memory card reader design and is designed for reliable and trouble-free performance. Features • Easily transfer music, photos, video, and other files between your computer and a digital camera/camcorder, action camera, smartphone, tablet, or similar device. • Supports SD, SDHC, SDXC, microSD, microSDHC, microSDXC, MMC, MMCplus, MemoryStick, MS PRO, MS-Duo, MS PRO Duo, MS PRO-HG Duo, MemoryStick Micro (M2), CompactFlash types I and II cards. • Plug & Play: drivers automatically load. • USB 3.0 high speed transfer. Also compatible with USB 2.0 computers. -

(MS, MS PRO, MMC, SD, Mmcplus, SDHC) Expresscard/34

Memory Express Ltd 51 Park Royal Road, Tel: 020 8453 9700 London, Web: www.memory-express.co.uk NW10 7LQ Email: [email protected] StarTech.com ExpressCard 12-in-1 Multi Media Memory Card Card reader 12 in 1 (MS, MS PRO, MMC, SD, MMCplus, SDHC) ExpressCard/34 This 12-in-1 memory card reader allows you to access several different types of media cards/memory cards from your laptop computer. Simply insert the card reader into an ExpressCard slot, and youll be able to read from and write to MemoryStick (MS) and Secure Digital (SD) media quickly and easily. This ExpressCard memory card reader is an ideal selection for accessing data such as digital photos, multimedia and more, relying on broad compatibility while adding to the capability of an existing notebook computer. Warranty 1 Year Warranty Barcode 0065030828208 Interface 1 x USB 2.0 System Requirements Microsoft Windows 2000 ME XP Vista Mac OS X Dimensions 3.3cm (W) x 7.8cm (D) x 0.5cm (H) - Weight 0.01kg Features * Compatible with Windows Vista * Hot swapping and plug and play * USB 2.0 transfer rate up to 480 Mbps * Fits into 34mm or 54mm ExpressCard slots * Supports high speed and high capacity memory cards * Convenient 12-in-1 card reader for accessing the next generation memory cards * Plug-and-play, no drivers required * Supports SDHC * Lightweight, convenient to carry Specification General This 12-in-1 memory card reader allows you to access several different types of media cards/memory cards from your laptop computer. Simply insert the card reader into an ExpressCard slot, and youll be able to read from and write to MemoryStick (MS) and Secure Digital (SD) media quickly and easily. -

USB 3.0 Flash Memory Card Reader Installation Guide

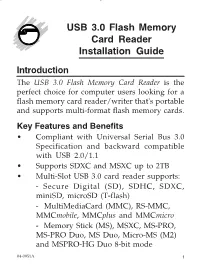

USB 3.0 Flash Memory Card Reader Installation Guide Introduction The USB 3.0 Flash Memory Card Reader is the perfect choice for computer users looking for a flash memory card reader/writer that's portable and supports multi-format flash memory cards. Key Features and Benefits • Compliant with Universal Serial Bus 3.0 Specification and backward compatible with USB 2.0/1.1 • Supports SDXC and MSXC up to 2TB • Multi-Slot USB 3.0 card reader supports: - Secure Digital (SD), SDHC, SDXC, miniSD, microSD (T-flash) - MultiMediaCard (MMC), RS-MMC, MMCmobile, MMCplus and MMCmicro - Memory Stick (MS), MSXC, MS-PRO, MS-PRO Duo, MS Duo, Micro-MS (M2) and MSPRO-HG Duo 8-bit mode 04-0951A 1 System Requirements • Notebook or desktop computer with an available USB port (USB 3.0 recommended) • Windows® 8 (32-/64-bit) / 7 (32-/64-bit) / Vista (32-/64-bit) / XP (32-/64-bit) / Server 2003 & 2008 (32-/64-bit) / Server 2008 R2 • Mac OS® X v10.6 or later Package Contents • USB 3.0 Flash Memory Card Reader • Installation guide Layout SD/SDHC/ SDXC/MMC Micro SD/ TF MS/MSXC USB 3.0 connector Figure 1: Layout Note: The Micro SD slot and SD slot can not be used simultaneously 2 Installation In order to work as a USB 3.0 card reader, the driver for your USB 3.0 host controller has to be properly installed. 1. Plug the Card Reader's USB 3.0 connector to a USB 3.0 port of the computer. 2. The Card Reader will automatically be detected and installed when connected to the USB 3.0 port. -

USB 2.0 6-In-1 Memory Card Reader/Writer

R TRENDnet TRENDware, USA TMR-61U2 USB 2.0 6-in-1 Memory Card Reader/Writer TRENDnet's TMR-61U2 USB 2.0 6-in-1 Memory Card Reader/Writer provides an ideal solution to read and write up to 6 types of memory cards including MultiMedia Card, CompactFlash Card, IBM Micro Drive, Smart Media Card, Secure Digital Card, and Memory Stick. Its 4-slot design accommodates up to 4 different types of memory cards at the same time for convenient file transfers between different types of cards. Transfer large files between your computer, digital camera, PDA, MP3 player and more. The TMR-61U2 has a UBS 2.0 interface that offers plug-and-play installation, Hi-Speed data transfer rate, and backward compatibility with USB1.1 interface. TRENDnet's TMR-61U2 6-in-1 Memory Card Reader/Writer provides incredibly easy and fast data transfer method for your memory cards. Características Benefícios Compliant with Hi-Speed USB 2.0 standard Integration Friendly: Supports Windows, Mac OS, and Backward compatible with USB 1.1 interface Linux. Reads and Writes Compact Flash Card (CF), Micro Drive (MD), Smart Media Card (SM), Memory Stick (MS), Secure Digital Efficiency: Card (SD) and MultiMedia Card (MMC) Save time from retrieving data from Reads/writes up to 4 different types of memory cards at the different types of memory card same time devices retrieving data from different types of Compatible with Windows 98/98SE/ME/2000/XP, Mac OS 8.6 memory card devices and above, and Linux kernel 2.4.0 and above Does not require driver installation for Windows ME/XP, Mac Flexible: OS 10.1.2 or above, and Linux Kernel 2.4.0 or above Minimize space and cables needed for connecting various memory card Supports USB high-speed (480Mbps), full-speed (12Mbps) and readers low-speed (1.5Mbps) transfer rates Supports Plug & Play and Hot-Swap Cost Effective: Reads and writes 6 different types of Portable compact design and no external power source memory cards (up to 4 at the same required time). -

Multimedia Memory Card Reader & Writer Expresscard

Easy Access to All of Your Key Benefits Gadgets’ Data Reads from and writes to all Memory Stick, MMC, SD and xD-Picture Card Sonnet’s 21-in-1 Multimedia Memory Card memory cards Reader & Writer ExpressCard/34 is a Simply Compatible with MacBook Pro and Fast™ solution for moving files between your Windows notebooks with ExpressCard electronic devices’ memory cards and your slot notebook computer’s hard drive, with no cables Fast file transfers between memory card required. This handy device works with the and computer without cables most popular memory card formats, including Memory Stick™, MMC (Multimedia Card), SD Inserts completely into slot with no (Secure Digital), XD-Picture Card™, and all their protrusion—may be left in all the time variations—wide compatibility enables you to Plug and play—no drivers to install work with memory cards used in devices such as digital cameras, cell phones, MP3 players, digital picture frames, and more! Mac Compatibility MacBook Pro (15" and 17") Wonderfully small, the Multimedia Memory Card Mac OS X Version 10.5 or 10.4 Reader & Writer ExpressCard/34 inserts flush Copy picture files from your digital camera's memory inside your MacBook Pro or Windows notebook’s card to your computer. ExpressCard slot so you can store it there when Windows Compatibility it’s not in use. Its ingenious design enables it to PC notebook with ExpressCard/54 or accept all the compatible memory cards through ExpressCard/34 slot a single slot—just push the card in. When you’re Windows Vista done transferring files to or from the memory card, just push it in further, and it pops out. -

All-In-1 USB 3.0 Card Reader/Writer

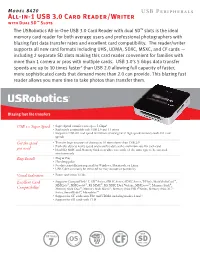

Model 8420 USB Peripherals All-in-1 USB 3.0 Card Reader/Writer with Dual SD™ Slots The USRobotics All-in-One USB 3.0 Card Reader with dual SD™ slots is the ideal memory card reader for both average users and professional photographers with blazing fast data transfer rates and excellent card compatibility. The reader/writer supports all new card formats including UHS, UDMA, SDXC, MSXC, and CF cards — including 2 separate SD slots making this card reader convenient for families with more than 1 camera or pros with multiple cards. USB 3.0’s 5 Gbps data transfer speeds are up to 10 times faster† than USB 2.0 allowing full capacity of faster, more sophisticated cards that demand more than 2.0 can provide. This blazing fast reader allows you more time to take photos than transfer them. Blazing fast file transfers USB 3.0 Super Speed • Super Speed transfer rates up to 5 Gbps† • Backwards compatible with USB 2.0 and 1.1 ports • Surpasses USB 2.0 read speed limitations allowing latest high speed memory cards full read speeds Get the speed • Transfer large amounts of data up to 10 times faster than USB 2.0† • Each slot detects native speed and transfers data at the maximum rate for each card you need • Dual SD, MMC and Memory Stick slots allow two cards of the same type to be accessed simultaneously Easy Install • Plug & Play • Hot Swappable • No driver installation required for Windows, Macintosh, or Linux • USB Cable can easily be removed for easy storage or portability Visual Indicators • Power and status LEDs Excellent Card • Supports CompactFlash® -

SBAC-US30 Brochure

SBAC-US30 SxS PRO+ and SxS-1 solid state memory USB 3.0 reader/writer Overview Hiigh speed transfers from SxS PRO+ and SxS-1 cards The SBAC-US30 SxS PRO+ and SxS-1 memory card reader/writer works on both Windows-based PCs and Macintosh computers via a USB 3.0 interface for high-speed transfer of audio-visual material. The reader is also compatible with a USB 2.0 interface. This compact and portable device is the successor to the SBAC-US20 and comes in handy in many situations on location, for desktop browsing and fully-fledged editing. • Higher speed transfers, approx. 2x faster than predecessor model Read speeds of approx. 440 MBps from latest SxS Pro+ and SxS-1 cards. Write speeds of approx. 350 MBps to latest SxS Pro+ cards. SBAC-US30 1 Features • Compatible with Windows and Mac operating systems The SBAC-US30 works on both Windows-based PCs and Macintosh computers. • USB 3.0 and USB 2.0 transfers The SBAC-US30 provides high speed transfer of audio/visual material from a SxS PRO+ or SxS-1 solid state memory card using an USB 3.0 interface, allowing you to make transfers when your computer does not have an ExpressCard slot. The device also provides compatibility with USB 2.0. • Bus-powered operation (AC adapter is not necessary) The SBAC-US30 is compatible with media other than a SxS PRO+ or SxS-1 card when using the following adapters: SD card adapter, Memory Stick adapter, XQD Express card adapter. SBAC-US30 2 Compatible Products 4K and HD System Cameras PMW-400K Three 2/3-inch type Exmor PMW-F55LIVE CMOS sensors with 16x zoom HD lens -

Installation Slot Identification

Thank you for purchasing the ProMaster® SD/MS Multi Memory Card Reader/Writer. The ProMaster® SD/MS Multi Memory Card Reader/Writer lets you access your pictures or other files from a memory card without the need to directly connect a camera or other media device to your computer. Follow the simple instructions in this user manual and enjoy the benefits of these convenient features: Easily access media and manage content almost anywhere Includes slot-to-slot read/write/copy and USB mass-storage capabilities Secure Digital (SD), Secure Digital High Capacity (SDHC), Secure Digital Extended Capacity (SDXC), Micro Secure Digital (Micro SD), Mini Secure Digital (Mini SD), Micro Secure Digital (Micro SD)/T-Flash, MultiMediaCard (MMC), RS MultiMediaCard (RS-MMC), MultiMedia Micro (MMC Micro), MultiMedia Plus 4.0 (MMC Plus 4.0), MultiMedia Mobile (MMC Mobile), Memory Stick (MS), Memory Stick PRO (MS PRO), Memory Stick Duo (MS Duo), Memory Stick PRO Duo (MS PRO Duo), Memory Stick PRO HG DUO, Micro MS (M2), Memory Stick Micro* *Some cards may require adapter supplied by memory card manufacturer. Supports automatic card detection and USB 2.0 high speed data transfer Eliminates need for direct connection of media device to save battery power Windows, Mac, and Linux compatible — hot swappable, Plug and Play INSTALLATION Connect the ProMaster® SD/MS Multi Memory Card Reader/Writer to any open USB port on your computer. Double-click on "My Computer" to confirm that the A drive letter labeled Removable Disk appears. Check that the blue power LED light on the reader comes on to confirm a proper connection.