Assembly Language: Part 1

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Frequently Asked Questions in Mathematics

Frequently Asked Questions in Mathematics The Sci.Math FAQ Team. Editor: Alex L´opez-Ortiz e-mail: [email protected] Contents 1 Introduction 4 1.1 Why a list of Frequently Asked Questions? . 4 1.2 Frequently Asked Questions in Mathematics? . 4 2 Fundamentals 5 2.1 Algebraic structures . 5 2.1.1 Monoids and Groups . 6 2.1.2 Rings . 7 2.1.3 Fields . 7 2.1.4 Ordering . 8 2.2 What are numbers? . 9 2.2.1 Introduction . 9 2.2.2 Construction of the Number System . 9 2.2.3 Construction of N ............................... 10 2.2.4 Construction of Z ................................ 10 2.2.5 Construction of Q ............................... 11 2.2.6 Construction of R ............................... 11 2.2.7 Construction of C ............................... 12 2.2.8 Rounding things up . 12 2.2.9 What’s next? . 12 3 Number Theory 14 3.1 Fermat’s Last Theorem . 14 3.1.1 History of Fermat’s Last Theorem . 14 3.1.2 What is the current status of FLT? . 14 3.1.3 Related Conjectures . 15 3.1.4 Did Fermat prove this theorem? . 16 3.2 Prime Numbers . 17 3.2.1 Largest known Mersenne prime . 17 3.2.2 Largest known prime . 17 3.2.3 Largest known twin primes . 18 3.2.4 Largest Fermat number with known factorization . 18 3.2.5 Algorithms to factor integer numbers . 18 3.2.6 Primality Testing . 19 3.2.7 List of record numbers . 20 3.2.8 What is the current status on Mersenne primes? . -

Chapter 7 Expressions and Assignment Statements

Chapter 7 Expressions and Assignment Statements Chapter 7 Topics Introduction Arithmetic Expressions Overloaded Operators Type Conversions Relational and Boolean Expressions Short-Circuit Evaluation Assignment Statements Mixed-Mode Assignment Chapter 7 Expressions and Assignment Statements Introduction Expressions are the fundamental means of specifying computations in a programming language. To understand expression evaluation, need to be familiar with the orders of operator and operand evaluation. Essence of imperative languages is dominant role of assignment statements. Arithmetic Expressions Their evaluation was one of the motivations for the development of the first programming languages. Most of the characteristics of arithmetic expressions in programming languages were inherited from conventions that had evolved in math. Arithmetic expressions consist of operators, operands, parentheses, and function calls. The operators can be unary, or binary. C-based languages include a ternary operator, which has three operands (conditional expression). The purpose of an arithmetic expression is to specify an arithmetic computation. An implementation of such a computation must cause two actions: o Fetching the operands from memory o Executing the arithmetic operations on those operands. Design issues for arithmetic expressions: 1. What are the operator precedence rules? 2. What are the operator associativity rules? 3. What is the order of operand evaluation? 4. Are there restrictions on operand evaluation side effects? 5. Does the language allow user-defined operator overloading? 6. What mode mixing is allowed in expressions? Operator Evaluation Order 1. Precedence The operator precedence rules for expression evaluation define the order in which “adjacent” operators of different precedence levels are evaluated (“adjacent” means they are separated by at most one operand). -

Operators and Expressions

UNIT – 3 OPERATORS AND EXPRESSIONS Lesson Structure 3.0 Objectives 3.1 Introduction 3.2 Arithmetic Operators 3.3 Relational Operators 3.4 Logical Operators 3.5 Assignment Operators 3.6 Increment and Decrement Operators 3.7 Conditional Operator 3.8 Bitwise Operators 3.9 Special Operators 3.10 Arithmetic Expressions 3.11 Evaluation of Expressions 3.12 Precedence of Arithmetic Operators 3.13 Type Conversions in Expressions 3.14 Operator Precedence and Associability 3.15 Mathematical Functions 3.16 Summary 3.17 Questions 3.18 Suggested Readings 3.0 Objectives After going through this unit you will be able to: Define and use different types of operators in Java programming Understand how to evaluate expressions? Understand the operator precedence and type conversion And write mathematical functions. 3.1 Introduction Java supports a rich set of operators. We have already used several of them, such as =, +, –, and *. An operator is a symbol that tells the computer to perform certain mathematical or logical manipulations. Operators are used in programs to manipulate data and variables. They usually form a part of mathematical or logical expressions. Java operators can be classified into a number of related categories as below: 1. Arithmetic operators 2. Relational operators 1 3. Logical operators 4. Assignment operators 5. Increment and decrement operators 6. Conditional operators 7. Bitwise operators 8. Special operators 3.2 Arithmetic Operators Arithmetic operators are used to construct mathematical expressions as in algebra. Java provides all the basic arithmetic operators. They are listed in Tabled 3.1. The operators +, –, *, and / all works the same way as they do in other languages. -

ARM Instruction Set

4 ARM Instruction Set This chapter describes the ARM instruction set. 4.1 Instruction Set Summary 4-2 4.2 The Condition Field 4-5 4.3 Branch and Exchange (BX) 4-6 4.4 Branch and Branch with Link (B, BL) 4-8 4.5 Data Processing 4-10 4.6 PSR Transfer (MRS, MSR) 4-17 4.7 Multiply and Multiply-Accumulate (MUL, MLA) 4-22 4.8 Multiply Long and Multiply-Accumulate Long (MULL,MLAL) 4-24 4.9 Single Data Transfer (LDR, STR) 4-26 4.10 Halfword and Signed Data Transfer 4-32 4.11 Block Data Transfer (LDM, STM) 4-37 4.12 Single Data Swap (SWP) 4-43 4.13 Software Interrupt (SWI) 4-45 4.14 Coprocessor Data Operations (CDP) 4-47 4.15 Coprocessor Data Transfers (LDC, STC) 4-49 4.16 Coprocessor Register Transfers (MRC, MCR) 4-53 4.17 Undefined Instruction 4-55 4.18 Instruction Set Examples 4-56 ARM7TDMI-S Data Sheet 4-1 ARM DDI 0084D Final - Open Access ARM Instruction Set 4.1 Instruction Set Summary 4.1.1 Format summary The ARM instruction set formats are shown below. 3 3 2 2 2 2 2 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1 9876543210 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 Cond 0 0 I Opcode S Rn Rd Operand 2 Data Processing / PSR Transfer Cond 0 0 0 0 0 0 A S Rd Rn Rs 1 0 0 1 Rm Multiply Cond 0 0 0 0 1 U A S RdHi RdLo Rn 1 0 0 1 Rm Multiply Long Cond 0 0 0 1 0 B 0 0 Rn Rd 0 0 0 0 1 0 0 1 Rm Single Data Swap Cond 0 0 0 1 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 1 Rn Branch and Exchange Cond 0 0 0 P U 0 W L Rn Rd 0 0 0 0 1 S H 1 Rm Halfword Data Transfer: register offset Cond 0 0 0 P U 1 W L Rn Rd Offset 1 S H 1 Offset Halfword Data Transfer: immediate offset Cond 0 -

PYTHON BASIC OPERATORS Rialspo Int.Co M/Pytho N/Pytho N Basic O Perato Rs.Htm Copyrig Ht © Tutorialspoint.Com

PYTHON BASIC OPERATORS http://www.tuto rialspo int.co m/pytho n/pytho n_basic_o perato rs.htm Copyrig ht © tutorialspoint.com What is an operator? Simple answer can be g iven using expression 4 + 5 is equal to 9. Here, 4 and 5 are called operands and + is called operator. Python lang uag e supports the following types of operators. Arithmetic Operators Comparison (i.e., Relational) Operators Assig nment Operators Log ical Operators Bitwise Operators Membership Operators Identity Operators Let's have a look on all operators one by one. Python Arithmetic Operators: Assume variable a holds 10 and variable b holds 20, then: [ Show Example ] Operator Description Example + Addition - Adds values on either side of the a + b will g ive 30 operator - Subtraction - Subtracts rig ht hand operand a - b will g ive -10 from left hand operand * Multiplication - Multiplies values on either side a * b will g ive 200 of the operator / Division - Divides left hand operand by rig ht b / a will g ive 2 hand operand % Modulus - Divides left hand operand by rig ht b % a will g ive 0 hand operand and returns remainder ** Exponent - Performs exponential (power) a**b will g ive 10 to the power 20 calculation on operators // Floor Division - The division of operands 9//2 is equal to 4 and 9.0//2.0 is equal to where the result is the quotient in which the 4.0 dig its after the decimal point are removed. Python Comparison Operators: Assume variable a holds 10 and variable b holds 20, then: [ Show Example ] Operator Description Example == Checks if the value of two operands are equal (a == b) is not true. -

Multiplication and Division Instructions

MultiplicationMultiplication andand DivisionDivision InstructionsInstructions • MUL Instruction • IMUL Instruction • DIV Instruction • Signed Integer Division • Implementing Arithmetic Expressions Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. 1 MULMUL InstructionInstruction • The MUL (unsigned multiply) instruction multiplies an 8-, 16-, or 32-bit operand by either AL, AX, or EAX. • The instruction formats are: MUL r/m8 MUL r/m16 MUL r/m32 Implied operands: Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. 2 MULMUL ExamplesExamples 100h * 2000h, using 16-bit operands: .data val1 WORD 2000h The Carry flag indicates whether or val2 WORD 100h not the upper half of .code the product contains mov ax,val1 significant digits. mul val2 ; DX:AX = 00200000h, CF=1 12345h * 1000h, using 32-bit operands: mov eax,12345h mov ebx,1000h mul ebx ; EDX:EAX = 0000000012345000h, CF=0 Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. 3 YourYour turnturn .. .. .. What will be the hexadecimal values of DX, AX, and the Carry flag after the following instructions execute? mov ax,1234h mov bx,100h mul bx DX = 0012h, AX = 3400h, CF = 1 Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. 4 YourYour turnturn .. .. .. What will be the hexadecimal values of EDX, EAX, and the Carry flag after the following instructions execute? mov eax,00128765h mov ecx,10000h mul ecx EDX = 00000012h, EAX = 87650000h, CF = 1 Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. 5 IMULIMUL InstructionInstruction • IMUL (signed integer multiply ) multiplies an 8-, 16-, or 32-bit signed operand by either AL, AX, or EAX • Preserves the sign of the product by sign-extending it into the upper half of the destination register Example: multiply 48 * 4, using 8-bit operands: mov al,48 mov bl,4 imul bl ; AX = 00C0h, OF=1 OF=1 because AH is not a sign extension of AL. -

Mathematics Learning

1 Key understandings in mathematics learning Paper 1: Overview By Terezinha Nunes, Peter Bryant and Anne Watson, University of Oxford A review commissioned by the Nuffield Foundation 2 PaperSUMMARY 1: Overview – PAPER 2: Understanding whole numbers About this review In 2007, the Nuffield Foundation commissioned a Contents team from the University of Oxford to review the available research literature on how children learn Summary of findings 3 mathematics. The resulting review is presented in a series of eight papers: Overview 10 Paper 1: Overview References 36 Paper 2: Understanding extensive quantities and whole numbers Paper 3: Understanding rational numbers and intensive quantities About the authors Paper 4: Understanding relations and their graphical Terezinha Nunes is Professor of Educational representation Studies at the University of Oxford. Paper 5: Understanding space and its representation Peter Bryant is Senior Research Fellow in the in mathematics Department of Education, University of Oxford. Paper 6: Algebraic reasoning Anne Watson is Professor of Mathematics Paper 7: Modelling, problem-solving and integrating Education at the University of Oxford. concepts Paper 8: Methodological appendix About the Nuffield Foundation Papers 2 to 5 focus mainly on mathematics relevant The Nuffield Foundation is an endowed to primary schools (pupils to age 11 y ears), while charitable trust established in 1943 by William papers 6 and 7 consider aspects of mathematics Morris (Lord Nuffield), the founder of Morris in secondary schools. Motors, with the aim of advancing social w ell being. We fund research and pr actical Paper 1 includes a summar y of the review, which experiment and the development of capacity has been published separately as Introduction and to undertake them; working across education, summary of findings. -

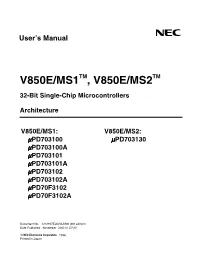

V850e/Ms1 , V850e/Ms2

User’s Manual V850E/MS1TM, V850E/MS2TM 32-Bit Single-Chip Microcontrollers Architecture V850E/MS1: V850E/MS2: µPD703100 µPD703130 µPD703100A µPD703101 µPD703101A µPD703102 µPD703102A µPD70F3102 µPD70F3102A Document No. U12197EJ6V0UM00 (6th edition) Date Published November 2002 N CP(K) 1996 Printed in Japan [MEMO] 2 User’s Manual U12197EJ6V0UM NOTES FOR CMOS DEVICES 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it. 2 HANDLING OF UNUSED INPUT PINS FOR CMOS Note: No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. -

High-Speed Multi Operand Addition Utilizing Flag Bits

HIGH-SPEED MULTI OPERAND ADDITION UTILIZING FLAG BITS BY VIBHUTI DAVE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering in the Graduate College of the Illinois Institute of Technology Approved _________________________ Adviser _________________________ Co – Adviser Chicago, Illinois May 2007 ACKNOWLEDGEMENT I would like to thank my mentor Dr. Erdal Oruklu for his constant support and undue faith in me. I highly appreciate the time he has invested during my research and for the completion of this dissertation. This dissertation would not have been possible without Dr. Jafar Saniie, my advisor and his attempts to challenge me throughout my academic program, encouraging me when I was successful and pushing me to do better when I fell short. I would also like to thank Dr. Dimitrios Velenis and Dr. James Stine for their constructive criticism about my work and helping me to perform better. A special thanks to the committee members for their support and time. iii TABLE OF CONTENTS Page ACKNOWLEDGEMENT ....................................................................................... iii LIST OF TABLES ................................................................................................... vi LIST OF FIGURES ................................................................................................. vii ABSTRACT ............................................................................................................ -

10 Instruction Sets: Characteristics and Functions Instruction Set = the Complete Collection of Instructions That Are Recognized by a CPU

William Stallings Computer Organization and Architecture 8th Edition Chapter 10 Instruction Sets: Characteristics and Functions Instruction Set = The complete collection of instructions that are recognized by a CPU. Representations: • Machine code (Binary/Hex) • Assembly code (Mnemonics) Example (IAS – see ch.2): 00000101 0000000011 ADD M(3) Elements of an Instruction • Operation code (opcode) —Do this • Source operand(s) reference(s) —To this • Result operand reference —Put the answer here • Next instruction reference —When you’ve finished, go here to find out what to do next... 00000101 0000000011 ADD M(3) Where are the operands stored? • In the instruction itself —immediate addressing • Main memory —or virtual memory or caches, but this is transparent to the CPU • CPU register • I/O device —If memory-mapped, it’s just another address 00000101 0000000011 ADD M(3) Instruction Cycle State Diagram (ch.3) Instruction Representation • In machine code each instruction (incl. operands!) has a unique bit pattern • In assembly code: —ADD M(3) —ADD A,B —etc. High-level language and assembly language X = X + Y compiles into: • Load register A with contents of memory address 513 • Add reg. A w/contents of mem. addr. 514 • Store reg. A into mem. addr. 513 Conclusion: assembly is closer to the hardware. Instruction Types • Data processing (ALU) • Data storage (main memory) • Data movement (I/O) • Program flow control Number of Addresses (a) • 3 addresses —Operand 1, Operand 2, Result —a = b + c; —There may be a forth – the next instruction! (usually -

Assembly Language

Chapter 2 Instructions: Assembly Language Reading: The corresponding chapter in the 2nd edition is Chapter 3, in the 3rd edition it is Chapter 2 and Appendix A and in the 4th edition it is Chapter 2 and Appendix B. 2.1 Instructions and Instruction set The language to command a computer architecture is comprised of instructions and the vocabulary of that language is called the instruction set. The only way computers can rep- resent information is based on high or low electric signals, i.e., transistors (electric switches) being turned on or off. Being limited to those 2 alternatives, we represent information in com- puters using bits (binary digits), which can have one of two values: 0 or 1. So, instructions will be stored in and read by computers as sequences of bits. This is called machine language. To make sure we don't need to read and write programs using bits, every instruction will also have a "natural language" equivalent, called the assembly language notation. For example, in C, we can use the expression c = a + b; or, in assembly language, we can use add c; a; b and these instructions will be represented by a sequence of bits 000000 010001001 in the computer. Groups of bits are named as follows: ··· bit 0 or 1 byte 8 bits half word 16 bits word 32 bits double word 64 bits Since every bit can only be 0 or 1, with a group of n bits, we can generate 2n different combinations of bits. For example, we can make 28 combinations with one byte (8 bits), 216 with one half word (16 bits), and 232 with one word (32 bits). -

X86 Assembly Language Reference Manual

x86 Assembly Language Reference Manual Sun Microsystems, Inc. 901 N. San Antonio Road Palo Alto, CA 94303-4900 U.S.A. Part No: 805-4693-10 October 1998 Copyright 1998 Sun Microsystems, Inc. 901 San Antonio Road, Palo Alto, California 94303-4900 U.S.A. All rights reserved. This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers. Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd. Sun, Sun Microsystems, the Sun logo, SunDocs, Java, the Java Coffee Cup logo, and Solaris are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc. The OPEN LOOK and SunTM Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun’s licensees who implement OPEN LOOK GUIs and otherwise comply with Sun’s written license agreements.