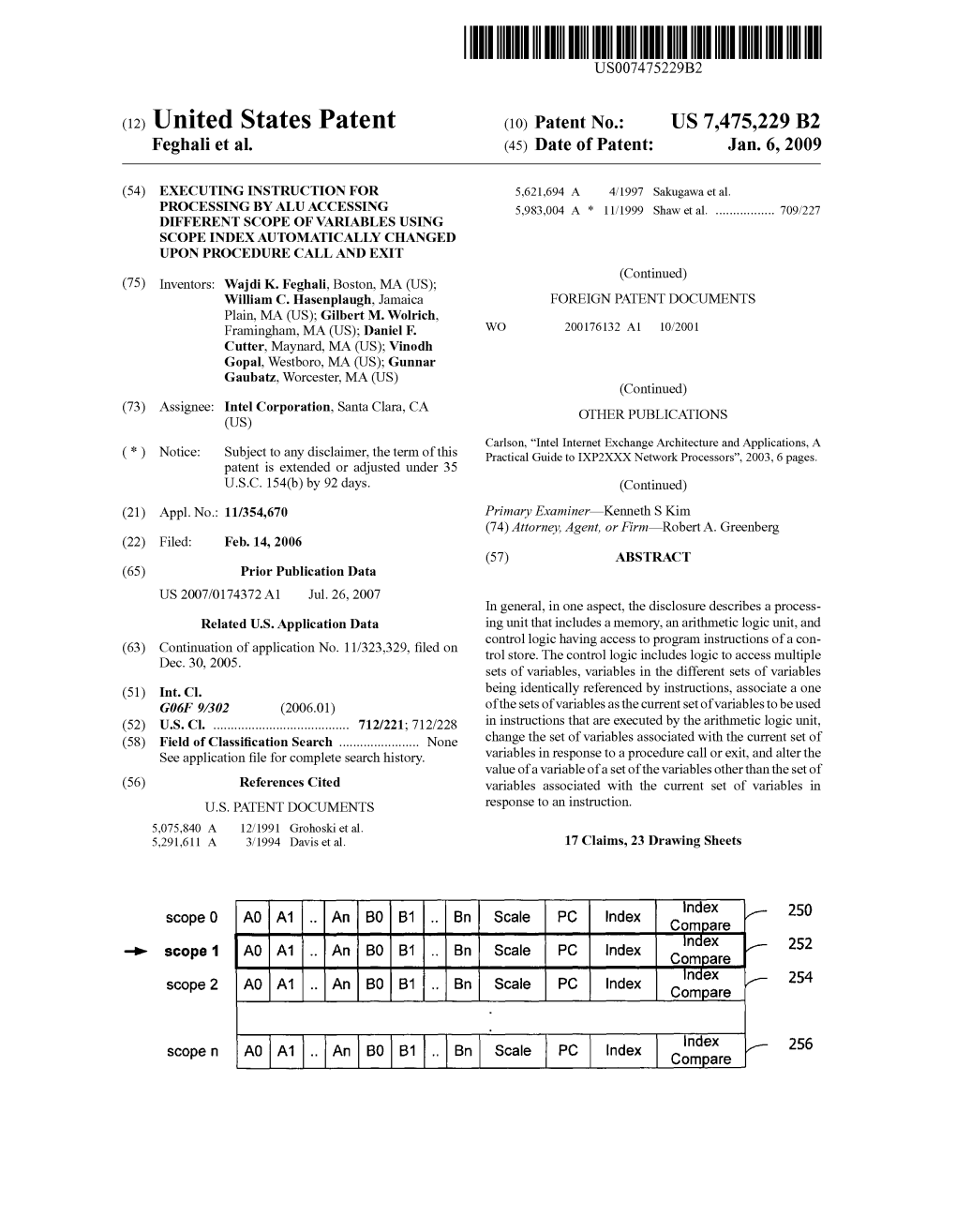

AOA. an BOB1.Bn Scale PC Index E 252 Scope 2 Aoat

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

AMD Athlon™ Processor X86 Code Optimization Guide

AMD AthlonTM Processor x86 Code Optimization Guide © 2000 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other applica- tion in which the failure of AMD’s product could create a situation where per- sonal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD logo, AMD Athlon, K6, 3DNow!, and combinations thereof, AMD-751, K86, and Super7 are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc. Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation. -

A PROGRAMMABLE COMPUTER INTERFACE for CAMAC F by Robert W

NASA TECHNICAL NOTE NASA TN D-7148 A PROGRAMMABLE COMPUTER INTERFACE FOR CAMAC f by Robert W. Bercaw, Theodore E. Fessler, \ and Jeffrey M. Arnold Lewis Research Center Cleveland, Ohio 44135 NATIONAL AERONAUTICS AND SPACE ADMINISTRATION • WASHINGTON, D. C. • MARCH 1973 1. Report No. 2. Government Accession No. 3. Recipient's Catalog No. NASA TN D-7148 4. Title and Subtitle 5. Report Date March 1973 A PROGRAMMABLE COMPUTER INTERFACE FOR CAMAC 6. Performing Organization Code 7. Author(s) 8. Performing Organization Report No. Robert W. Bercaw, Theodore E. Fessler, and Jeffrey M. Arnold E-6957 10. Work Unit No. 9. Performing Organization Name and Address 503-10 Lewis Research Center 11. Contract or Grant No. National Aeronautics and Space Administration Cleveland, Ohio 44135 13. Type of Report and Period Covered 12. Sponsoring Agency Name and Address Technical Note National Aeronautics and Space Administration 14. Sponsoring Agency Code Washington, B.C. 20546 15. Supplementary Notes 16. Abstract An interface has been developed for CAMAC instrumentation systems that implements data transfers controlled either by the computer CPU or by an autonomous (data-channel) processor in the interface unit. The data channel processor executes programs stored in the computer memory. These programs consist of standard CAMAC module commands plus special control characters and commands for the processor itself. The interface was built for the PDP-15 computer, which has an 18-bit word structure, but both 18- and 24-bit data transfers can be made. A software system has been written that exploits the many features of the processor. 17. Key Words (Suggested by Author(s)) 18. -

Application Note Saving Data During a Power Failure Using the Dataflash® E-Series Family

Saving Data During a Power Failure Using the DataFlash® E-Series Family Application Note Saving Data During a Power Failure Using the DataFlash® E-Series Family Abstract This application note is intended to provide readers with information on how to save critical data to the Flash memory of DataFlash E-Series devices in the event of a power failure. The power failure is simulated by removing power to the devices. This document does not discuss how the power failure is detected, how the microcontroller may respond to the failure, or how the power rail is controlled for both the DataFlash device and the microcontroller. Product Highlights • Single 3V Read/Write Operation (1.65V - 3.6V Supply Range) • SPI Mode 0 and Mode 3 Compatible • Fast Read Access Times: 85 MHz Maximum Clock Frequency • Individual Hardware and Software Sector Protection • Security: 128-byte Register • JEDEC Standard Manufacturer and Device ID Read • Endurance: 100,000 Program/Erase Cycles per Page Minimum • Data Retention: 20 Years • Packaging Options: SOIC, DFN, WLCSP, Die/Wafer • Green (Pb/Halide-free) Packaging Options Application Note 114 11-Dec-2020 AN114 1 of 13 © 2020 Dialog Semiconductor Saving Data During a Power Failure Using the DataFlash® E-Series Family Revision History Revision Date Description A0 11-Dec-2020 Initial Release Application Note 114 11-Dec-2020 AN114 2 of 13 © 2020 Dialog Semiconductor Saving Data During a Power Failure Using the DataFlash® E-Series Family 1 Introduction The DataFlash E-series family of Flash memory devices are often used in applications such as server configuration, data logging, event counters and failure/error/status loggers. -

14-/12-Bit, 250MSPS, Ultralow-Power ADC with Analog Buffers Check for Samples: ADS41B29, ADS41B49

ADS41B29 ADS41B49 www.ti.com SBAS486E – NOVEMBER 2009–REVISED JULY 2012 14-/12-Bit, 250MSPS, Ultralow-Power ADC with Analog Buffers Check for Samples: ADS41B29, ADS41B49 1FEATURES DESCRIPTION The ADS41B29/B49 are members of the ultralow- 23• ADS41B49: 14-Bit, 250MSPS ADS41B29: 12-Bit, 250MSPS power ADS4xxx analog-to-digital converter (ADC) family, featuring integrated analog input buffers. • Integrated High-Impedance These devices use innovative design techniques to Analog Input Buffer: achieve high dynamic performance, while consuming – Input Capacitance: 2pF extremely low power. The analog input pins have – 200MHz Input Resistance: 3kΩ buffers, with benefits of constant performance and input impedance across a wide frequency range. The • Maximum Sample Rate: 250MSPS devices are well-suited for multi-carrier, wide • Ultralow Power: bandwidth communications applications such as PA – 1.8V Analog Power: 180mW linearization. – 3.3V Buffer Power: 96mW The ADS41B49/29 have features such as digital gain – I/O Power: 135mW (DDR LVDS) and offset correction. The gain option can be used to improve SFDR performance at lower full-scale input • High Dynamic Performance: ranges, especially at high input frequencies. The – SNR: 69dBFS at 170MHz integrated dc offset correction loop can be used to – SFDR: 82.5dBc at 170MHz estimate and cancel the ADC offset. At lower sampling rates, the ADC automatically operates at • Output Interface: scaled-down power with no loss in performance. – Double Data Rate (DDR) LVDS with Programmable Swing and Strength: The devices support both double data rate (DDR) low-voltage differential signaling (LVDS) and parallel – Standard Swing: 350mV CMOS digital output interfaces. The low data rate of – Low Swing: 200mV the DDR LVDS interface (maximum 500MBPS) – Default Strength: 100Ω Termination makes it possible to use low-cost field-programmable gate array (FPGA)-based receivers. -

Real-Time Operating System (RTOS)

Real-Time Operating System ELC 4438 – Spring 2016 Liang Dong Baylor University RTOS – Basic Kernel Services Task Management • Scheduling is the method by which threads, processes or data flows are given access to system resources (e.g. processor time, communication bandwidth). • The need for a scheduling algorithm arises from the requirement for most modern systems to perform multitasking (executing more than one process at a time) and multiplexing (transmit multiple data streams simultaneously across a single physical channel). Task Management • Polled loops; Synchronized polled loops • Cyclic Executives (round-robin) • State-driven and co-routines • Interrupt-driven systems – Interrupt service routines – Context switching void main(void) { init(); Interrupt-driven while(true); } Systems void int1(void) { save(context); task1(); restore(context); } void int2(void) { save(context); task2(); restore(context); } Task scheduling • Most RTOSs do their scheduling of tasks using a scheme called "priority-based preemptive scheduling." • Each task in a software application must be assigned a priority, with higher priority values representing the need for quicker responsiveness. • Very quick responsiveness is made possible by the "preemptive" nature of the task scheduling. "Preemptive" means that the scheduler is allowed to stop any task at any point in its execution, if it determines that another task needs to run immediately. Hybrid Systems • A hybrid system is a combination of round- robin and preemptive-priority systems. – Tasks of higher priority can preempt those of lower priority. – If two or more tasks of the same priority are ready to run simultaneously, they run in round-robin fashion. Thread Scheduling ThreadPriority.Highest ThreadPriority.AboveNormal A B ThreadPriority.Normal C ThreadPriority.BelowNormal D E F ThreadPriority.Lowest Default priority is Normal. -

Parallelization Hardware Architecture Type to Enter Text

Parallelization Hardware architecture Type to enter text Delft University of Technology Challenge the future Contents • Introduction • Classification of systems • Topology • Clusters and Grid • Fun Hardware 2 hybrid parallel vector superscalar scalar 3 Why Parallel Computing Primary reasons: • Save time • Solve larger problems • Provide concurrency (do multiple things at the same time) Classification of HPC hardware • Architecture • Memory organization 5 1st Classification: Architecture • There are several different methods used to classify computers • No single taxonomy fits all designs • Flynn's taxonomy uses the relationship of program instructions to program data • SISD - Single Instruction, Single Data Stream • SIMD - Single Instruction, Multiple Data Stream • MISD - Multiple Instruction, Single Data Stream • MIMD - Multiple Instruction, Multiple Data Stream 6 Flynn’s Taxonomy • SISD: single instruction and single data stream: uniprocessor • SIMD: vector architectures: lower flexibility • MISD: no commercial multiprocessor: imagine data going through a pipeline of execution engines • MIMD: most multiprocessors today: easy to construct with off-the-shelf computers, most flexibility 7 SISD • One instruction stream • One data stream • One instruction issued on each clock cycle • One instruction executed on single element(s) of data (scalar) at a time • Traditional ‘von Neumann’ architecture (remember from introduction) 8 SIMD • Also von Neumann architectures but more powerful instructions • Each instruction may operate on more than one data element • Usually intermediate host executes program logic and broadcasts instructions to other processors • Synchronous (lockstep) • Rating how fast these machines can issue instructions is not a good measure of their performance • Two major types: • Vector SIMD • Parallel SIMD 9 Vector SIMD • Single instruction results in multiple operands being updated • Scalar processing operates on single data elements. -

The 8255A Is Generally Seen As 8-Bit Bidirectional Data Buffer, Which Is

PROGRAMMABLE PERIPHERAL INTERFACE 8255 The 8255A is generally seen as 8-bit bidirectional data buffer, which is specially designed to transfer the data with the execution of input output instructions requested by the CPU. It has the ability to use with almost any microprocessor. It consists of three 8-bit bidirectional I/O ports (24I/O lines) which can be configured with their different functional characteristics, each possessing unique features to upgrade the flexibility of 8255. Ports of 8255A 8255A consists of three ports, i.e., PORT A, PORT B, and PORT C. Port A contains one 8-bit output latch/buffer and one 8-bit input buffer possessing both pull- up and pull-down devices present in Port A. Port B is similar to PORT A. Port C can be split into two parts, i.e. PORT C lower (PC0-PC3) and PORT C upper (PC7- PC4) with the help of control word. These three ports are further classified into two groups, i.e. Group A includes PORT A and upper PORT C. Group B includes PORT B and lower PORT C. These two groups can be programmed in three different modes, i.e. the first mode is named as mode 0, the second mode is named as Mode 1 and the third mode is named as Mode 2. Data Bus Buffer : It is a tri-state 8-bit bidirectional data buffer, which helps in interfacing the microprocessor to the system data bus. Data is transmitted or received by the buffer with the input output instructions given by the CPU. -

COS 318: Operating Systems I/O Device Interactions and Drivers

Topics COS 318: Operating Systems u So far: l Management of CPU and concurrency l Management of main memory and virtual memory I/O Device Interactions and u Next: Management of the I/O system Drivers l Interacting with I/O devices l Device drivers Jaswinder Pal Singh l Storage Devices Computer Science Department Princeton University u Then, File Systems l File System Structure (http://www.cs.princeton.edu/courses/cos318/) l Naming and Directories l Efficiency/Performance l Reliability and Protection 2 Input and Output Revisit Hardware u A computer u Compute hardware CPU l CPU cores and caches CPU l Computation (CPU, memory hierarchy) CPUCPU CPU l Memory $ l Move data into and out of a system (locketween I/O devices Chip l I/O and memory hierarchy) l Controllers and logic Memory I/O bridge u Challenges with I/O devices I/O bus l Different categories with different characteristics: storage, u I/O Hardware networking, displays, keyboard, mouse ... l I/O bus or interconnect l Large number of device drivers to support l I/O device l I/O controller or adapter l Device drivers run in kernel mode and can crash systems • Often on parent board Network u Goals of the OS • Cable connects it to device • Often using standard interfaces: IDE, l Provide a generic, consistent, convenient and reliable way to SATA, SCSI, USB, FireWire… access I/O devices • Has registers for control, data signals • Processor gives commands and/or l Achieve potential I/O performance in a system data to controller to do I/O • Special I/O instructions (w. -

Ans: the Buffer Register Prevents the High Speed Processor from Being

1. a) What is use of buffers? Ans: The Buffer Register prevents the high speed processor from being locked to a slow I/O device during a sequence of data transfer or reduces speed mismatch between faster and slower devices. b) Write basic performance equation. Ans: T=(N*S)/R Where, TPerformance Parameter RClock Rate in cycles/sec NActual number of instruction execution SAverage number of basic steps needed to execute one machine instruction. c) What is an interrupt? Ans: An interrupt is a signal to processor generated by hardware or software indicating an event that needs immediate attention. d) How control memory works? Ans: Control Memory is the storage in the microprogrammed control unit to store the microprogram(sequence of micro instructions). e) What is role of micro programmed control? Ans: A microprogrammed control unit is a relatively simple logic circuit that is capable of sequencing through microinstructions and (2) generating control signals to execute each microinstruction. f) Explain indirect register addressing modes. Ans: Register indirect addressing means that the location of an operand is held in a register. It is also called indexed addressing or base addressing. g) State the meaning of locality of reference. Ans: Many instructions in localized areas of the program are executed repeatedly during some time period. This behaviour manifests itself in two ways: temporal and spatial. h) Define virtual memory. Ans: virtual memory is a memory management technique creates the illusion to users of a very large main memory. Also a Technique that automatically move program and data blocks into the physical main memory when they are required for execution is called the Virtual Memory. -

8-Bit Microcontroller with 12 Kbyte Flash AT89S8253

Features • Compatible with MCS®51 Products • 12K Bytes of In-System Programmable (ISP) Flash Program Memory – SPI Serial Interface for Program Downloading – Endurance: 10,000 Write/Erase Cycles • 2K Bytes EEPROM Data Memory – Endurance: 100,000 Write/Erase Cycles • 64-byte User Signature Array • 2.7V to 5.5V Operating Range • Fully Static Operation: 0 Hz to 24 MHz (in x1 and x2 Modes) 8-bit • Three-level Program Memory Lock • 256 x 8-bit Internal RAM Microcontroller • 32 Programmable I/O Lines • Three 16-bit Timer/Counters with 12 Kbyte • Nine Interrupt Sources Flash • Enhanced UART Serial Port with Framing Error Detection and Automatic Address Recognition • Enhanced SPI (Double Write/Read Buffered) Serial Interface • Low-power Idle and Power-down Modes AT89S8253 • Interrupt Recovery from Power-down Mode • Programmable Watchdog Timer • Dual Data Pointer • Power-off Flag • Flexible ISP Programming (Byte and Page Modes) – Page Mode: 64 Bytes/Page for Code Memory, 32 Bytes/Page for Data Memory • Four-level Enhanced Interrupt Controller • Programmable and Fuseable x2 Clock Option • Internal Power-on Reset • 42-pin PDIP Package Option for Reduced EMC Emission • Green (Pb/Halide-free) Packaging Option 1. Description The AT89S8253 is a low-power, high-performance CMOS 8-bit microcontroller with 12K bytes of In-System Programmable (ISP) Flash program memory and 2K bytes of EEPROM data memory. The device is manufactured using Atmel’s high-density non- volatile memory technology and is compatible with the industry-standard MCS-51 instruction set and pinout. The on-chip downloadable Flash allows the program mem- ory to be reprogrammed in-system through an SPI serial interface or by a conventional nonvolatile memory programmer. -

D: Serial Driver

CHAPTER 7 Serial Driver 7 This chapter describes how you can use the Serial Driver to transfer data to a device connected to a Macintosh modem or printer port. The Serial Driver supports 7 asynchronous serial data communication between applications and serial devices Serial Driver through these ports. The Serial Driver provides low-level support for communicating with serial devices that cannot be accessed through the Communications Toolbox or Printing Manager. For example, a scientific instrument or a printer that does not support QuickDraw. Before you decide to use the Serial Driver, you should determine whether it is the appropriate solution for your communication needs. The Communications Toolbox is the recommended method for integrating modems and other telecommunications devices into the Macintosh environment. The Communications Toolbox provides hardware-independent services and a standard interface that offers compatibility with all Macintosh models. To find out more about the Communications Toolbox, see Inside the Macintosh Communications Toolbox. Likewise, the Printing Manager is the recommended interface for printers and similar output devices. Using the Printing Manager makes your hardware or software product compatible with every other device or application that supports this standard interface. Refer to Inside Macintosh: Imaging With QuickDraw for more information. To use the Serial Driver, you should understand how to open, close, and communicate with device drivers using the Device Manager. You can find this information in -

A New Approach to Making I2C Bus Buffers

A New Approach to Making I2C Bus Buffers SCOPE: The information in this paper helps electronic engineers and engineering managers stay informed of developments with the I2C (Inter-Integrated-Circuit) bus system. All existing I2C bus buffers use the signal amplitude to set the signal flow direction, and use voltage offset techniques to avoid bus buffer latching. The no-offset buffer is different and unique in that it uses the signal timing as the direction flow control, thus eliminating many prior design headaches. The I2C Bus – From Humble Beginnings The I2C Bus – From Humble Beginnings to to New Uses 1 I2C Signal Flows 2 New Uses I2C-bus Buffer Basics 2 The simplicity and low cost of the I2C bus has enticed electronic engineers Making I2C-bus Buffers that Work 2 to find more uses for the two-wire Inter-Integrated-Circuit protocol, and its Innovation in I2C-bus Buffer many derivatives. Techniques — The No-offset Type 3 Key Features of No-offset Bus Buffers 3 While the technology has been around for decades, and is still a viable Introducing the Industry’s First solution for many maintenance and control applications, additional No-offset Bus Buffers 5 components have been invented to make it better and more useful. In Summary 8 particular, to overcome some of the basic limitations due to adding more devices to the bus or extending the bus length beyond its original maximum of just a few meters. The most popular addition to the family has been the bus buffer, which relays the signals, but there have also been a variety of other devices invented that can switch the I2C-bus to different branches and greatly enhance its usefulness.