Turbo Boost Up, AVX Clock Down: Complica,Ons for Scaling Tests

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

HP Engage Flex Pro-C Retail System Your Retail Workhorse, Now Available in a Handy Miniature Size

Datasheet HP Engage Flex Pro-C Retail System Your retail workhorse, now available in a handy miniature size Efficiently manage your retail business from the store floor to the back office with the petite but powerful HP Engage Flex Pro-C. Our stable, secure, and highest-performing compact retail platform is 30% smaller than its predecessor and still delivers maximum flexibility for a range of deployments. Build your best solution for even the smallest spaces HP recommends Windows 10 Pro for business Configure the perfect fit for your space, users, and environment— point of sale, video surveillance, processing/controlling, digital Windows 10 Pro1 signage or OEM needs—with flexible connectivity, graphics, and networking options and a suite of retail peripherals.2 Poised to perform and expand with your business Tackle every retail challenge with a powerful 8th Gen Intel® processor3 and Intel® Optane™ memory.4 Adjust capacity as your needs change with endless storage options like an Intel® Optane™ SSD, SATA or M.2—up to four total drives per system.2 Secure, manageable, and reliable out of the box Reduce the cost and complexity of managing your platforms and secure your critical assets with innovative, integrated, and proactive security and manageability features for your system and its data. Featuring Stick with an OS you know with your choice of Windows 10 Pro, Windows IoT or FreeDOS. Get hardware-enforced self-healing protection from HP Sure Start Gen4, manage your system across the OS with HP Manageability Integration Kit, maintain critical OS processes with HP Sure Run, and restore your image over a network with HP Sure Recover. -

Deskmini H470 Series.Pdf

Version 1.0 Published June 2020 This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation. CALIFORNIA, USA ONLY The Lithium battery adopted on this motherboard contains Perchlorate, a toxic substance controlled in Perchlorate Best Management Practices (BMP) regulations passed by the California Legislature. When you discard the Lithium battery in California, USA, please follow the related regulations in advance. “Perchlorate Material-special handling may apply, see www.dtsc.ca.gov/hazardouswaste/ perchlorate” AUSTRALIA ONLY Our goods come with guarantees that cannot be excluded under the Australian Consumer Law. You are entitled to a replacement or refund for a major failure and compensation for any other reasonably foreseeable loss or damage caused by our goods. You are also entitled to have the goods repaired or replaced if the goods fail to be of acceptable quality and the failure does not amount to a major failure. The terms HDMI™ and HDMI High-Definition Multimedia Interface, and the HDMI logo are trademarks or registered trademarks of HDMI Licensing LLC in the United States and other countries. Contents Chapter 1 Introduction 1 1.1 Package Contents 1 1.2 Specifications 2 Chapter 2 Product Overview 4 2.1 Front View 4 2.2 Rear View 5 1.3 Motherboard Layout 6 Chapter 3 Hardware Installation 13 3.1 Begin Installation 13 3.2 -

HP Proone 400 G6 20 All-In-One PC Ready for Versatile Work Environments

Datasheet HP ProOne 400 G6 20 All-in-One PC Ready for versatile work environments Easy to deploy, sleek, and feature-rich, the HP ProOne 400 20 All-in-One PC features a contemporary design with business-class performance, collaboration, security, and manageability features. Functionality for the multi-device world HP recommends Windows 10 Pro for Provide users with multiple devices options for how they work and stay productive. New business flexibility is delivered by the HP ProOne 400 20 AiO that can be used as a full PC or as an additional display for another desktop or laptop PC.2 1 HP recommends Windows 10 Pro for Sleek, elegant design business Featuring a sleek design, this AiO undergoes MIL-STD 810H testing3 and still suits the front 2 desk or an owner’s office. The anti-glare 19.5-inch diagonal display provides plenty of Intel® Core™ processors workspace. HP exclusive security and manageability Help prevent data breaches and downtime with HP Sure Sense4, HP Sure Click5, and HP BIOSphere Gen5.6 Simplify management with the HP Manageability Integration Kit.7 Ease fleet deployment and management with the optional Intel® Q470 chipset and Intel® vPro™.8 Powerful options Choose a high-performance 10th Gen Intel® Core™ processor9 with optional PCIe NVMe™ SSD storage10 and high-speed DDR4 memory10 or Intel® Optane™ memory H1011, and optional high-end discrete graphics.10 Support a commitment to create and use more sustainable products. The high-efficiency power supply, use of ocean-bound plastics in the speaker box and molded pulp packaging help reduce the impact on the environment.12 Malware is evolving rapidly, and traditional antivirus can’t always recognize new attacks. -

Intel® Xeon® Processor 5600 Series Specification Update February 2015 Contents

Intel® Xeon® Processor 5600 Series Specification Update Febuary 2015 Reference Number: 323372-017US You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps. Intel technologies may require enabled hardware, specific software, or services activation. Check with your system manufacturer or retailer. No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm%20 Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor_number for details See the http://processorfinder.intel.com/ or contact your Intel representative for more information. -

Intel Unveils All New 2010 Intel® Core™ Processor Family

Intel Unveils All New 2010 Intel® Core™ Processor Family Industry's Smartest, Most Advanced Technology Available in Variety of Price Points LAS VEGAS, Jan 07, 2010 (BUSINESS WIRE) -- Intel Corporation: NEWS HIGHLIGHTS 1 ● Mainstream processors now offer Intel(R) Turbo Boost Technology , automatically adapting to an individual's performance needs ● First 32 nanometer processors and first time Intel is mass-producing a variety of chips at mainstream prices at start of new manufacturing process, reflecting last year's $7 billion investment during economic recession 4 ● Intel(R) Core(TM) i5 processors are about twice as fast as comparable existing PCs for visibly faster video, photo and music downloading experience ● Historic milestone: select processors integrate graphics directly on processors; also include Intel's second generation high-k metal gate transistors ● Beyond laptops and PCs, processors also target ATMs, travel kiosks, digital displays ● More than 10 new chipsets and new 802.11n WiFi and WiMAX products with new Intel(R) My WiFi features Intel Corporation introduced its all new 2010 Intel(R) Core(TM) family of processors today, delivering unprecedented integration and smart performance, including Intel(R) Turbo Boost Technology1 for laptops, desktops and embedded devices. The introduction of new Intel(R) Core(TM) i7, i5 and i3 chips coincides with the arrival of Intel's groundbreaking new 32 nanometer (nm) manufacturing process - which for the first time in the company's history - will be used to immediately produce and deliver processors and features at a variety of price points, and integrate high-definition graphics inside the processor. This unprecedented ramp and innovation reflects Intel's $7 billion investment announced early last year in the midst of a major global economic recession. -

Variation Among Processors Under Turbo-‐Boost

Variation Among Processors Under Turbo-Boost Bilge Acun, Ph.D. Candidate Department of Computer Science University of Illinois at Urbana-Champaign This talk is based on the publicaon: Bilge Acun, Phil Miller, Laxmikant Kale. ICS 2016. 1 “Variaon Among Processors under Turbo Boost in HPC Systems”. Motivation: Performance Variation 16% Performance Only 1% VariaEon on Variaon on Edison, Blue Waters! Cab, Stampede! ��������������������������� ���� ���� �������� ���� ��� ���� ������ ���� ���� ���� ���� Acun, Miller, Kale. “Variaon Among Processors under Turbo ���� Boost in HPC Systems” [ICS 2016] �������������������� �� ���� ���� ���� ���� ���� ���� ���� ���� 2 ������� • 16K cores running local DGEMM kernel of Intel-MKL What is Dynamic Overclocking? • Processor changes the frequency opportunis3cally since it cannot run at the highest limit all the 3me. • E.g. Intel Turbo Boost Technology • Factors effec3ng the dynamic frequency: • Type of the workload • Number of ac3ve cores • Current consump3on �������������������������� • Power consump3on ��� • Temperature Acun, Miller, Kale. “Variaon Among Processors under Turbo Boost in HPC Systems” [ICS 2016] ��� ��������������� �������� ���� ���� 3 �� ���� ���� ���� ���� ���� ���������� Motivation: Frequency Variation ������������������������������ ���� ������ ��������������� ���� ��� ��������������� ���� �������� ��������������� ���� ���� ���� �������������� ���� ���� Acun, Miller, Kale. “Variaon Among Processors under Turbo ���� ���� ���� ���� ���� ���� �� ���� ���� Boost in HPC Systems” [ICS 2016] ��������������� -

![Intel® Select Solutions for HPC & AI Converged Clusters [Univa*]](https://docslib.b-cdn.net/cover/4283/intel%C2%AE-select-solutions-for-hpc-ai-converged-clusters-univa-1644283.webp)

Intel® Select Solutions for HPC & AI Converged Clusters [Univa*]

SOLUTION BRIEF Intel® Select Solutions High Performance Computing and AI May 2019 Intel® Select Solutions for HPC & AI Converged Clusters [Univa*] Intel Select Solutions deliver the compute-intensive resources needed to run artificial-intelligence (AI) workloads on existing high-performance computing (HPC) clusters. Enterprises are looking to simulation and modeling, artificial intelligence (AI), and big data analytics to help them achieve breakthrough discoveries and innovation. They understand these workloads benefit from a high-performance computing (HPC) infrastructure, yet they might still believe that separate HPC, AI, and big data clusters are the best choice for running these workloads. Contributing to this belief are two challenges. The first challenge is a fundamental difference in how workloads request resources and how HPC systems allocate them. AI and analytics workloads request compute resources dynamically, an approach that isn’t compatible with the batch scheduling software used to allocate system resources in HPC clusters. The second challenge is the pattern of using computing systems based on graphics processing units (GPUs) as dedicated solutions for AI workloads. Enterprises might not realize that adding these workloads to an existing HPC cluster is feasible without the use of GPUs. Enterprises can deliver the compute infrastructure needed by AI workloads, with high levels of performance and cost-effectiveness, without adding the complexity of managing separate, dedicated systems. What they need is the ability to run HPC, big data analytics, and AI workloads within the same HPC infrastructure and with optimized resource scheduling that helps save time and reduce computing costs. Creating a converged platform to run HPC, AI, and analytics workloads in a single cluster infrastructure supports breakthrough innovation, made possible by the convergence of these workloads, while increasing the value and utilization of resources. -

Intel Select Solutions for HPC & AI Converged Clusters

Solution Brief Intel® Select Solutions High Performance Computing and AI March 2021 Intel Select Solutions for HPC & AI Converged Clusters Intel Select Solutions deliver the compute-intensive resources needed to run artificial-intelligence (AI) workloads on existing high-performance computing (HPC) clusters. Enterprises are looking to simulation and modeling, artificial intelligence (AI), and big data analytics to help them achieve breakthrough discoveries and innovation. They understand these workloads benefit from a high-performance computing (HPC) infrastructure, yet they might still believe that separate HPC, AI, and big data clusters are the best choice for running these workloads. Contributing to this belief are two challenges. The first challenge is a fundamental difference in how workloads request resources and how HPC systems allocate them. AI and analytics workloads request compute resources dynamically, an approach that isn’t compatible with batch scheduling software used to allocate system resources in HPC clusters. The second challenge is the pattern of using computing systems based on graphics processing units (GPUs) as dedicated solutions for AI workloads. Enterprises might not realize that adding these workloads to an existing HPC cluster is feasible without the use of GPUs. Enterprises can deliver the compute infrastructure needed by AI workloads, with high levels of performance and cost-effectiveness, without adding the complexity of managing separate, dedicated systems. What they need is the ability to run HPC, big data analytics, and AI workloads within the same HPC infrastructure. They also need optimized resource scheduling that helps save time and reduce computing costs. Creating a converged platform to run HPC, AI, and analytics workloads in a single cluster infrastructure supports breakthrough innovation. -

Intel® Core™ I7-860 and Core™ I5-750 Processors for Embedded Computing

PRODUCT BRIEF Intel® Core™ i7 and Core™ i5 Processors Embedded Computing Intel® Core™ i7-860 and Core™ i5-750 Processors for Embedded Computing Product Overview Product Highlights Based on 45nm process technology, Innovative Integration: An integrated ∆ ∆ Intel® Core™ i7-860 and Core™ i5-750 high-speed, 1333 MHz dual-channel DDR3 processors feature quad-core process- memory controller and flexible x16 PCI 1 ing and Intel® Turbo Boost Technology Express* 2.0 controller are integrated to meet the needs of compute-intensive with the processor. embedded applications. The Intel Core i7-860 processor also features Intel® Intel® Turbo Boost Technology: Appli- Hyper-Threading Technology2 which cations take advantage of higher speed enables simultaneous multi-threading execution on demand by using available within each processor core. processor thermal headroom to let the individual processor cores run at a When paired with the Intel® Q57 chipset, higher frequency. these platforms provide outstanding performance for a variety of market Intel® Hyper-Threading Technology: segments, including retail, digital signage, Simultaneous multi-threading boosts digital security surveillance, gaming, performance for parallel, multi-threaded medical, communications and industrial applications. It delivers two processing automation and control. threads per physical core for a total of eight threads, significantly enhancing The dual-channel integrated memory computational throughput and multi- controller supports high-speed data trans- tasking capabilities (Intel Core fer, providing lower memory latency in a i7-860 processor only). two-chip solution, with board real estate savings over previous three-chip platforms. Intel® Intelligent Power Technology3: Developers can create one board design Reduces idle power consumption through and scale their product line with a variety architectural improvements such as of processors using the same socket. -

Intel® Core™ I5 Desktop Processor with Intel® HD Graphics

PRODUCT BRIEF Intel® Core™ i5 Desktop Processor with Intel® HD Graphics Intel® Core™ i5 Desktop Processor Product Overview • Intel Smart Cache improves responsive- Performance has an immediate, perceptible The Intel® Core™ i5 processor with Intel® ness by providing faster access to data. impact on what you do on your PC. Accelerate your productivity, inspire your digital HD Graphics offers an unparalleled com- • Intel HD Graphics is the ideal graphics creations, and enjoy video smoothness puting experience. This revolutionary solution for your everyday visual computing new architecture, featuring Intel® Turbo and music quality on a system with the needs. Boost Technology1, allows for new levels Intel Core i5 processor—the smart choice of intelligent performance, advanced for home and office. media and graphics features, and expanded Comparison Table business capabilities—all while being energy efficient. INTEL® CoRE™ i5-6XX INTEL® CoRE™ i5-6X1 SERIES SERIES Technology Socket LG A1156 LG A1156 What makes this new architecture so Intel® Turbo Boost Technology1 Yes Yes revolutionary? The features of Intel® Turbo Intel® Hyper-Threading Technology1 Yes Yes Boost Technology, Intel® Hyper-Threading Intel® Smart Cache 4 MB L3 shared 4 MB L3 shared Technology1, and the improvements to Intel® Integrated Memory Controller Yes Yes Smart Cache combine to create dynamic and adaptive performance that accelerates Number of Memory Channels 2 (DDR3 1333 MHz) 2 (DDR3 1333 MHz) everything without the user having to do Intel® HD Graphics Yes Yes anything. Add the integration of the memory Graphics Core Frequency 733 MHz 900 MHz controller and the graphics to the processor Intel® vPro™ Technology Yes No and the Intel Core i5 processor gets things 1 done faster and more efficiently. -

Precision 7550 Setup and Specifications Guide

Precision 7550 Setup and specifications guide Regulatory Model: P93F Regulatory Type: P93F001 May 2021 Rev. A05 Notes, cautions, and warnings NOTE: A NOTE indicates important information that helps you make better use of your product. CAUTION: A CAUTION indicates either potential damage to hardware or loss of data and tells you how to avoid the problem. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. © 2020 - 2021 Dell Inc. or its subsidiaries. All rights reserved. Dell, EMC, and other trademarks are trademarks of Dell Inc. or its subsidiaries. Other trademarks may be trademarks of their respective owners. Contents Chapter 1: Set up your computer...................................................................................................5 Chapter 2: Chassis overview..........................................................................................................7 Display view...........................................................................................................................................................................7 Right view..............................................................................................................................................................................9 Left view.............................................................................................................................................................................. 10 Palmrest view..................................................................................................................................................................... -

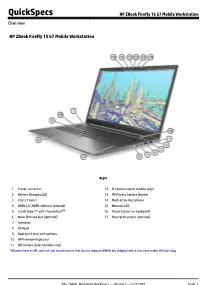

HP Zbook Firefly 15 G7 Mobile Workstation Overview

QuickSpecs HP ZBook Firefly 15 G7 Mobile Workstation Overview HP ZBook Firefly 15 G7 Mobile Workstation Right 1. Power connector 12. IR Camera (select models only) 2. Battery Charging LED 13. HP Privacy Camera Shutter 3. USB 3.1 Gen 1 14. Multi-array microphone 4. HDMI 2.0 (HDMI cable not included) 15. Webcam LED 5. 2 USB Type-C® with ThunderboltTM 16. Power button (on keyboard) 6. Nano SIM card slot (optional)1 17. fingerprint sensor (optional) 7 Speakers 8. Clickpad 9. Dual point stick with buttons 10. HP Premium Keyboard 11. HD Camera (select models only) 1All units have a SIM card slot and icon but units that do not support WWAN are shipped with a non-removable SIM slot plug DA - 16660 Worldwide QuickSpecs — Version 1 — 6.23.2020 Page 1 QuickSpecs HP ZBook Firefly 15 G7 Mobile Workstation Overview Left 1. Nano security lock slot (cable lock sold separately) 3. Audio combo jack 2. USB 3.1 Gen 1 4. HP Smart Card Reader Bottom 1. Fan Venting DA - 16660 Worldwide QuickSpecs — Version 1 — 6.23.2020 Page 2 QuickSpecs HP ZBook Firefly 15 G7 Mobile Workstation Overview At A Glance Work anywhere without compromising on performance or security with Windows 10 Pro1, powered by HP's collaboration and connectivity technology. Open large files and run apps simultaneously for speedy multitasking and productivity with the next generation NVIDIA® Quadro® graphics with 4GB of video memory. Bring your ideas to life quickly and effectively with the latest 10th gen quad core Intel® CoreTM processors2 with up to 4.9 GHz of acceleration when you need it most.3 Strenuously tested to meet ISV certification and deliver superb performance and support with leading software providers, including Autodesk and Adobe®.4 Have confidence with the world's most secure mobile workstations.5 Instantly protect against visual hacking with HP Sure View Reflect6 and defend against firmware and malware attacks with HP Sure Start Gen57, HP Sure Sense8 and HP Sure Platform9, new tamper detection switch.