ARTIK 530/530S Module Datasheet Samsung Semiconductor, Inc

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Politics of Roman Memory in the Age of Justinian DISSERTATION Presented in Partial Fulfillment of the Requirements for the D

The Politics of Roman Memory in the Age of Justinian DISSERTATION Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University By Marion Woodrow Kruse, III Graduate Program in Greek and Latin The Ohio State University 2015 Dissertation Committee: Anthony Kaldellis, Advisor; Benjamin Acosta-Hughes; Nathan Rosenstein Copyright by Marion Woodrow Kruse, III 2015 ABSTRACT This dissertation explores the use of Roman historical memory from the late fifth century through the middle of the sixth century AD. The collapse of Roman government in the western Roman empire in the late fifth century inspired a crisis of identity and political messaging in the eastern Roman empire of the same period. I argue that the Romans of the eastern empire, in particular those who lived in Constantinople and worked in or around the imperial administration, responded to the challenge posed by the loss of Rome by rewriting the history of the Roman empire. The new historical narratives that arose during this period were initially concerned with Roman identity and fixated on urban space (in particular the cities of Rome and Constantinople) and Roman mythistory. By the sixth century, however, the debate over Roman history had begun to infuse all levels of Roman political discourse and became a major component of the emperor Justinian’s imperial messaging and propaganda, especially in his Novels. The imperial history proposed by the Novels was aggressivley challenged by other writers of the period, creating a clear historical and political conflict over the role and import of Roman history as a model or justification for Roman politics in the sixth century. -

ROTEX Gassolarunit Gas Condensing Boiler with Stratified Solar Storage Tank

For specialist technical operation ROTEX GasSolarUnit Gas condensing boiler with stratified solar storage tank Installation and maintenance instructions 0085 BM 0065 Type Rated thermal output GB ROTEX GSU 320 3 - 20 kW modulating Edition 09/2007 ROTEX GSU 520S 3 - 20 kW modulating ROTEX GSU 530S 7 - 30 kW modulating ROTEX GSU 535 8 - 35 kW modulating Manufacture number Customer Guarantee and conformity ROTEX accepts the guarantee for material and manufacturing defects according to this statement. Within the guarantee period, ROTEX agrees to have the device repaired by a person assigned by the company, free of charge. ROTEX reserves the right to replace the device. The guarantee is only valid if the device has been used properly and it can be proved that it was installed properly by an expert firm. As proof, we strongly recommend completing the enclosed installation and instruction forms and returning them to ROTEX. Guarantee period The guarantee period begins on the day of installation (billing date of the installation company), however at the latest 6 months after the date of manufacture (billing date). The guarantee period is not extended if the device is returned for repairs or if the device is replaced. Guarantee period of burner, boiler body and boiler electronics: 2 years Guarantee exclusion Improper use, intervention in the device and unprofessional modifications immediately invalidate the guarantee claim. Dispatch and transport damage are excluded from the guarantee offer. The guarantee explicitly excludes follow-up costs, especially the assembly and disassembly costs of the device. There is no guarantee claim for wear parts (according to the manufacturer's definition), such as lights, switches, fuses. -

The Edictum Theoderici: a Study of a Roman Legal Document from Ostrogothic Italy

The Edictum Theoderici: A Study of a Roman Legal Document from Ostrogothic Italy By Sean D.W. Lafferty A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Department of History University of Toronto © Copyright by Sean D.W. Lafferty 2010 The Edictum Theoderici: A Study of a Roman Legal Document from Ostrogothic Italy Sean D.W. Lafferty Doctor of Philosophy Department of History University of Toronto 2010 Abstract This is a study of a Roman legal document of unknown date and debated origin conventionally known as the Edictum Theoderici (ET). Comprised of 154 edicta, or provisions, in addition to a prologue and epilogue, the ET is a significant but largely overlooked document for understanding the institutions of Roman law, legal administration and society in the West from the fourth to early sixth century. The purpose is to situate the text within its proper historical and legal context, to understand better the processes involved in the creation of new law in the post-Roman world, as well as to appreciate how the various social, political and cultural changes associated with the end of the classical world and the beginning of the Middle Ages manifested themselves in the domain of Roman law. It is argued here that the ET was produced by a group of unknown Roman jurisprudents working under the instructions of the Ostrogothic king Theoderic the Great (493-526), and was intended as a guide for settling disputes between the Roman and Ostrogothic inhabitants of Italy. A study of its contents in relation to earlier Roman law and legal custom preserved in imperial decrees and juristic commentaries offers a revealing glimpse into how, and to what extent, Roman law survived and evolved in Italy following the decline and eventual collapse of imperial authority in the region. -

Jordanes and the Invention of Roman-Gothic History Dissertation

Empire of Hope and Tragedy: Jordanes and the Invention of Roman-Gothic History Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University By Brian Swain Graduate Program in History The Ohio State University 2014 Dissertation Committee: Timothy Gregory, Co-advisor Anthony Kaldellis Kristina Sessa, Co-advisor Copyright by Brian Swain 2014 Abstract This dissertation explores the intersection of political and ethnic conflict during the emperor Justinian’s wars of reconquest through the figure and texts of Jordanes, the earliest barbarian voice to survive antiquity. Jordanes was ethnically Gothic - and yet he also claimed a Roman identity. Writing from Constantinople in 551, he penned two Latin histories on the Gothic and Roman pasts respectively. Crucially, Jordanes wrote while Goths and Romans clashed in the imperial war to reclaim the Italian homeland that had been under Gothic rule since 493. That a Roman Goth wrote about Goths while Rome was at war with Goths is significant and has no analogue in the ancient record. I argue that it was precisely this conflict which prompted Jordanes’ historical inquiry. Jordanes, though, has long been considered a mere copyist, and seldom treated as an historian with ideas of his own. And the few scholars who have treated Jordanes as an original author have dampened the significance of his Gothicness by arguing that barbarian ethnicities were evanescent and subsumed by the gravity of a Roman political identity. They hold that Jordanes was simply a Roman who can tell us only about Roman things, and supported the Roman emperor in his war against the Goths. -

Accessories for Two-Way Radios PRYME RADIO PRODUCTS MSRP

Accessories for Two-Way Radios PRYME RADIO PRODUCTS Effective Apr.1, 2021 MSRP PRICE LIST Prices subject to change without notice. Quick Disconnect (QD) accessories and radio adapters provide both security and usability. Just install the PA series adapter onto the radio then plug the QD accessory into the rugged six-pin QD connector. CLICK ON PICTURE FOR LINK TO PRODUCT ON THE PRYME WEBSITE. DON'T SEE WHAT YOU WANT? WE ARE ALWAYS ADDING NEW PRODUCTS - PLEASE CALL FOR THE LATEST INFO. Click on Photo PART NUMBER PRODUCT DESCRIPTION MSRP These QD Accessories can also be used on PRYMEBLU adapters that have a QD connector. (List) SPM-4205 Storm Trooper® WATER-PROOF SPEAKER MICROPHONE with Hi/Low Volume control switch and NC $110.00 (Noise canceling) Mic. Designed to meet IP67 standards for water-proof and dust resistance and comes with a 3 year warranty. 3.5mm jack for listen only earphones. X05 Connector (order radio adapter separately) SPM-2205 TROOPER II® Series HEAVY DUTY SPEAKER MICROPHONES have a Noise canceling Mic and are designed $70.00 to meet MIL-STD-810 mechanical and IP57 Dust and Water Proof standards. Troopers also have a 3.5mm earphone jack and 3-year warranty. X05 Connector (order radio adapter separately) SPM-2105 TROOPER® Series HEAVY DUTY SPEAKER MICROPHONES have a Replaceable Cable and are designed to $70.00 meet MIL-STD-810 mechanical and IP56 Dust and Water Resistant standards. Troopers also have a 3.5mm earphone jack and 3-year warranty. X05 Connector (order radio adapter separately) SPM-605 OEM (Motorola) Style SPEAKER MICROPHONE. -

International Brangus Breeders Association 5750 Epsilon San Antonio, TX 78249 (210) 696-4343

International Brangus Breeders Association 5750 Epsilon San Antonio, TX 78249 (210) 696-4343 2015 SUMMIT COW LISTING The following requirments are used to identify the Summit Cows: ~ Initially calved at 30 months of age or younger ~ Maintained a calving interval of 380 days or less ~ Must have weaned at least 3 calves ~ All calves weaned must have weaning records submitted ~ Average weaning weight ratio on all weaned calves is 105 or higher ~ All calves must be sired by a registered Brangus bull ~ All 2015 Summit Cows must have recorded a calf born since Jul 1, 2013 To be listed here, the cows must be owned by current IBBA members Owner Reg No PHN Name Award Year 3-D FARMS R10085158 75S A&D BIG SKY KATE 75S 2014 Summit Cow 4F WARD RANCH R761503 101J6 MS HCC CATHY 101J6 2009 Summit Cow R9681551 420/4 MS JR/ CADENCE 312H2 420/4 2015 Summit Cow ** R9677477 59/3 MS JR/ CAPTAIN 59/3 2013 Summit Cow R819407 876/2 MS JR LAZY BAR CADENCE 876/2 2009 Summit Cow R793914 876/1 MS TWIN OAKS 876/1 2014 Summit Cow R804851 98/2 MS TWIN OAKS CADENCE 98/2 2009 Summit Cow 4 MILE CATTLE COMPANY R10044384 35S4 SVF MS 35S4 2012 Summit Cow ADDISON BRANGUS FARMS R10071347 27S SVF MS 607N2 27S 2015 Summit Cow ** A FRANK BROCK R728577 114H BF MS. BRAVO 114H 2009 Summit Cow R674732 746-6 BF MS BRAVO 746-6 2011 Summit Cow R728599 93H BF MS. BRAVO 93H 2008 Summit Cow R728582 97H BF MS. -

25011016 Justinian

"Our Most Pious Consort Given Us by God": Dissident Reactions to the Partnership of Justinian and Theodora, A.D. 525-548 Author(s): Charles Pazdernik Source: Classical Antiquity, Vol. 13, No. 2 (Oct., 1994), pp. 256-281 Published by: University of California Press Stable URL: http://www.jstor.org/stable/25011016 Accessed: 12-01-2017 22:58 UTC REFERENCES Linked references are available on JSTOR for this article: http://www.jstor.org/stable/25011016?seq=1&cid=pdf-reference#references_tab_contents You may need to log in to JSTOR to access the linked references. JSTOR is a not-for-profit service that helps scholars, researchers, and students discover, use, and build upon a wide range of content in a trusted digital archive. We use information technology and tools to increase productivity and facilitate new forms of scholarship. For more information about JSTOR, please contact [email protected]. Your use of the JSTOR archive indicates your acceptance of the Terms & Conditions of Use, available at http://about.jstor.org/terms University of California Press is collaborating with JSTOR to digitize, preserve and extend access to Classical Antiquity This content downloaded from 128.228.173.41 on Thu, 12 Jan 2017 22:58:39 UTC All use subject to http://about.jstor.org/terms CHARLES PAZDERNIK "Our Most Pious Consort Given Us by God": Dissident Reactions to the Partnership of Justinian and Theodora, A.D. 525-548 T E VIVIDNESS with which the reign of Justinian I and his empress Theodora holds our imagination emerges no less from the coloring given the period in the writings of contemporary figures than from the events themselves, however momentous they were. -

GPSMAP® 400/500 Series Owner’S Manual © 2010—2011 Garmin Ltd

GPSMAP® 400/500 series owner’s manual © 2010—2011 Garmin Ltd. or its subsidiaries Garmin International, Inc. Garmin (Europe) Ltd. Garmin Corporation 1200 East 151st Street, Liberty House No. 68, Zhangshu 2nd Road, Olathe, Kansas 66062, USA Hounsdown Business Park, Xizhi Dist., New Taipei City, 221, Taiwan (R.O.C.) Tel. (913) 397.8200 or (800) 800.1020 Southampton, Hampshire, SO40 9LR UK Tel. 886/2.2642.9199 Fax (913) 397.8282 Tel. +44 (0) 870.8501241 (outside the UK) Fax 886/2.2642.9099 0808 2380000 (within the UK) Fax +44 (0) 870.8501251 All rights reserved. Except as expressly provided herein, no part of this manual may be reproduced, copied, transmitted, disseminated, downloaded or stored in any storage medium, for any purpose without the express prior written consent of Garmin. Garmin hereby grants permission to download a single copy of this manual onto a hard drive or other electronic storage medium to be viewed and to print one copy of this manual or of any revision hereto, provided that such electronic or printed copy of this manual must contain the complete text of this copyright notice and provided further that any unauthorized commercial distribution of this manual or any revision hereto is strictly prohibited. Information in this document is subject to change without notice. Garmin reserves the right to change or improve its products and to make changes in the content without obligation to notify any person or organization of such changes or improvements. Visit the Garmin Web site (www.garmin.com) for current updates and supplemental information concerning the use and operation of this and other Garmin products. -

Justinian,S Compilation: Classical Legacy and Legal Source

r9931 JusnmaN's ColpnlnoN JUSTINIAN,S COMPILATION: CLASSICAL LEGACY AND LEGAL SOURCE Peter Stein" When we think of the legacy of antiquitY, w€ think first of Greek philosophy, Greek art, Greek drama, and when we turn to what we have received from the Romans, they gave us Roman roads and Roman law. Almost everything that we know about ancient Roman law derives from a compilation of legal materials made between the years 529 and 534 A.D. on the orders of the Byzantine emperor Justinian.l The Corpus iuris, as it is known, is composed of materials of very different origin. One part, the Institutes, is an elementary textbook intended for students at the beginning of their studies, based on a pioneering work by Gaius written nearly four centuries before. Another part, the Code, is a collection of pieces of imperial legislation, mainly the authoritative answers, issued over the years in the names of particular emperors, to questions on law put by litigants or judges. They are artanged in chronological order under specific subject headings or titles. Like the Institutes, the Code was modelled on an earlier precedent, the Code of Theodosius II of 438 A.D. By far the largest part of Justinian's compilation is, however, one for which there was no Roman precedent, namely the Digest or Pandects. This is an anthology of extracts from the writings of legal experts, the classical jurists, who wrote mainly in the first two centuries A.D., the most recent being three centuries earlier than Justinian's time. It is a work of considerable bulk, being four times the size of the Code and one and a half times the size of the Bible. -

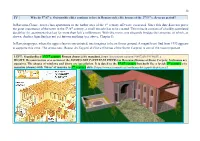

IV in Ravenna-Classe, Lower-Class Apartments in the Harbor Area of The

38 IV Why do 5th/6th c. Ostrogothic elites continue to live in Roman-style elite houses of the 2nd/3rd c. Severan period? In Ravenna-Classe, lower-class apartments in the harbor area of the 1st century AD were excavated. Since this date does not prove the great importance of the town in the 5th/6th century, a small miracle has to be created. This miracle consists of a boldly postulated durability for apartments that last for more than half a millennium. With this move, one elegantly bridges the centuries, of which, as shown, Andrea Agnellus has not yet known anything (see above, Chapter I). In Ravenna proper, where the upper class is concentrated, one imagines to be on firmer ground. A magnificent find from 1993 appears to supports this view. The aristocratic Domus dei Tappeti di Pietra (Domus of the Stone Carpets) is one of the most important LEFT: Standardized 1st/2nd century Roman domus (city mansion). [https://pl.pinterest.com/pin/91057223699970657/.] RIGHT: Reconstruction of a section of the DOMUS DEI TAPPETI DI PIETRA in Ravenna (Domus of Stone Carpets; bedrooms are upstairs). The shapes of windows and doors are speculation. It is dated to the 5th/6th century but built like a lavish 2nd century city mansion (domus) with 700 m2 of mosaics in 2nd century style. [https://www.ravennantica.it/en/domus-dei-tappeti-di-pietra-ra/.] 39 Italian archaeological sites discovered in recent decades. Located inside the eighteenth-century Church of Santa Eufemia, in a vast underground environment located about 3 meters below street level, it consists of 14 rooms paved with polychrome mosaics and marble belonging to a private building of the fifth-sixth century. -

AD 536 the Sun Dimmed and Global Temperatures Plunged, Leading to Famine, Plague and the Collapse of Empires

“ The sun began to be darkened by day and the moon by night, while the ocean was tumultuous with spray from the 24th of March in this year till the 24th of June in the following year… And, as the winter was a severe one, so much so that from the large and unwonted quantity of snow the birds perished… there was distress… among men… from the evil things” ZACHARIAS OF MYTILENE (Chronicle, 9.19, 10.1) The year of darkness In AD 536 the sun dimmed and global temperatures plunged, leading to famine, plague and the collapse of empires. At last clues are emerging about the cause of this event, as Colin Barras reports 34 | NewScientist | 18 January 2014 EBvb^ofp>A203)^ka?vw^kqfkb efpqlof^kMol`lmfrplc@^bp^ob^e^pgrpq T^oofsbafkplrqebokFq^iv+Qeb_^i^k`blc mltbofkqebJbafqboo^kb^kfpfkciru7S^ka^ip e^ap^`hbaOljbfk122^kaqebTbpqbok Olj^kBjmfobe^ac^iibkfk143+Grpqfkf^kF) qeb?vw^kqfkb%loB^pqbokOlj^k&Bjmbolo) fpabqbojfkbaqlob`i^fjqebilpqqboofqlofbp+ >cqbo^pr``bppcri`^jm^fdk^d^fkpqqebKloqe >cof`^kS^ka^iHfkdaljfkqebb^oiv20-p) Grpqfkf^kafpm^q`ebpefp^ojvqlobq^hbFq^iv+ Vbq^pMol`lmfrpob`loap)pljbqefkdlaa qebke^mmbkba+Qebprkafjjba)^kaqeb afjkbppi^pqbaclojlobqe^k^vb^o+Qebob tbobcolpqp^kapkltpfkqebjfaaiblc prjjboÌqebtfkqbokbsboob^iivbkaba+Colj Fq^ivqlFobi^ka)@efk^ql@bkqo^i>jbof`^)qeb vb^o203t^pqeb_bdfkkfkdlc^ab`^ab*ilkd `liapk^m_bpbq_vqrojlfi+Obifdflkpilpq _bifbsbop)`fqfbp`lii^mpba^kalkblcqeb dob^qbpqmi^drbpfkefpqlovhfiiba^nr^oqbo lcqebmlmri^qflkfkqeb?vw^kqfkbBjmfob+ Grpqfkf^kÑp^ojfbpafaj^k^dbqlobq^hbOljb) _rqefptb^hbkbabjmfobt^plsbopqobq`eba) ^kapllkilpqqebqboofqlov^d^fk+ -

Snap Acting Relay PRODUCT MANUAL YT-520 / 525 / 530 / 535 Series

Snap acting relay PRODUCT MANUAL YT-520 / 525 / 530 / 535 Series YT-520S YT-520D YT-525S YT-525D YT-530S YT-530D YT-535S YT-535D Rotork YTC Limited VERSION 1.04 Snap acting relay YT-520 / 525 / 530 / 535 series Product Manual Contents 1 Introduction .................................................................................................................................................3 1.1 General Information for the users .........................................................................................................3 1.2 Manufacturer Warranty .........................................................................................................................3 2 Product Description ...................................................................................................................................4 2.1 General .................................................................................................................................................4 2.2 Main Features and Functions ...............................................................................................................4 2.3 Label Description ..................................................................................................................................5 2.4 Product Code ........................................................................................................................................6 2.5 Product Specification ............................................................................................................................6