440GX Application Note

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Red Hat Enterprise Linux 3 Security Guide

Red Hat Enterprise Linux 3 Security Guide Red Hat Enterprise Linux 3: Security Guide Copyright © 2003 by Red Hat, Inc. Red Hat, Inc. 1801 Varsity Drive Raleigh NC 27606-2072 USA Phone: +1 919 754 3700 Phone: 888 733 4281 Fax: +1 919 754 3701 PO Box 13588 Research Triangle Park NC 27709 USA rhel-sg(EN)-3-Print-RHI (2003-07-25T17:12) Copyright © 2003 by Red Hat, Inc. This material may be distributed only subject to the terms and conditions set forth in the Open Publication License, V1.0 or later (the latest version is presently available at http://www.opencontent.org/openpub/). Distribution of substantively modified versions of this document is prohibited without the explicit permission of the copyright holder. Distribution of the work or derivative of the work in any standard (paper) book form for commercial purposes is prohibited unless prior permission is obtained from the copyright holder. Red Hat, Red Hat Network, the Red Hat "Shadow Man" logo, RPM, Maximum RPM, the RPM logo, Linux Library, PowerTools, Linux Undercover, RHmember, RHmember More, Rough Cuts, Rawhide and all Red Hat-based trademarks and logos are trademarks or registered trademarks of Red Hat, Inc. in the United States and other countries. Linux is a registered trademark of Linus Torvalds. Motif and UNIX are registered trademarks of The Open Group. XFree86 is a trademark of The XFree86 Project, Inc, and is pending registration. Intel and Pentium are registered trademarks of Intel Corporation. Itanium and Celeron are trademarks of Intel Corporation. AMD, Opteron, Athlon, Duron, and K6 are registered trademarks of Advanced Micro Devices, Inc. -

Porte TCP/IP 19/09/2021

1 MarkOne Tools Porte TCP/IP 19/09/2021 1 PORTS 0F TCP/IP Protocols and Services Introduction The port numbers are divided into three ranges: the Well Known Ports: are those from 0 through 1023. DCCP Well Known ports SHOULD NOT be used without IANA registration. The registration procedure is defined in [RFC4340], Section 19.9. the Registered Ports: are those from 1024 through 49151. DCCP Registered ports SHOULD NOT be used without IANA registration. The registration procedure is defined in [RFC4340], Section 19.9. the Dynamic and/or Private Ports: are those from 49152 through 65535 PLEASE NOTE THE FOLLOWING: 1. UNASSIGNED PORT NUMBERS SHOULD NOT BE USED. THE IANA WILL ASSIGN THE NUMBER FOR THE PORT AFTER YOUR APPLICATION HAS BEEN APPROVED. 2. ASSIGNMENT OF A PORT NUMBER DOES NOT IN ANY WAY IMPLY AN ENDORSEMENT OF AN APPLICATION OR PRODUCT, AND THE FACT THAT NETWORK TRAFFIC IS FLOW- ING TO OR FROM A REGISTERED PORT DOES NOT MEAN THAT IT IS "GOOD" TRAFFIC. FIREWALL AND SYSTEM ADMINISTRATORS SHOULD CHOOSE HOW TO CONFIGURE THEIR SYSTEMS BASED ON THEIR KNOWLEDGE OF THE TRAFFIC IN QUESTION, NOT WHETHER THERE IS A PORT NUMBER REGISTERED OR NOT. Socket: è costituito dal concatenamento di un indirizzo IP con il numero di porta di una specifica applicazione (p.es. 10.65.10.13:2001) TCP/IP protocols Port Name Alias 0 IP IP 1 icmp ICMP 3 ggp GGP 6 tcp TCP 8 egp EGP 12 pup PUP 17 udp UDP 20 hmp HMP 22 xns-idp XNS-IDP 27 rdp RDP 66 rvd RVD 1 last updated 2007-01-24 2 MarkOne Tools Porte TCP/IP 19/09/2021 WELL KNOWN PORT NUMBERS The Well Known Ports are assigned by the IANA and on most systems can only be used by system (or root) processes or by programs executed by privileged users. -

Prosafe Gigabit Quad WAN SSL VPN Firewall SRX5308 CLI Reference Manual

ProSafe Gigabit Quad WAN SSL VPN Firewall SRX5308 CLI Reference Manual 350 East Plumeria Drive San Jose, CA 95134 USA August 2012 202-11138-01 v1.0 ProSafe Gigabit Quad WAN SSL VPN Firewall SRX5308 © 2012 NETGEAR, Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of NETGEAR, Inc. NETGEAR, the NETGEAR logo, and Connect with Innovation are trademarks and/or registered trademarks of NETGEAR, Inc. and/or its subsidiaries in the United States and/or other countries. Information is subject to change without notice. Other brand and product names are registered trademarks or trademarks of their respective holders. © 2012 All rights reserved. Technical Support Thank you for choosing NETGEAR. To register your product, get the latest product updates, get support online, or for more information about the topics covered in this manual, visit the Support website at http://support.netgear.com. Phone (US & Canada only): 1-888-NETGEAR Phone (Other Countries): Check the list of phone numbers at http://support.netgear.com/app/answers/detail/a_id/984. Statement of Conditions To improve internal design, operational function, and/or reliability, NETGEAR reserves the right to make changes to the products described in this document without notice. NETGEAR does not assume any liability that may occur due to the use, or application of, the product(s) or circuit layout(s) described herein. Revision History Publication Part Number Version Publish Date Comments 202-11138-01 1.0 August 2012 First publication 2 Contents Chapter 1 Introduction Command Syntax and Conventions. -

Annex Communications Server Network Administrator's Guide 166

1\N"l:X COMMUNICATIONS SERVER Network Administrator's Guide )xy1og1ca] Copyright @ 1990 Xylogics, Inc. 166- 024- 000 Revision E November 1991 1\N-41:X COMMUNICATIONS SERVER Network Administrator's Guide 166-024-000 Revision E November 1991 Notice The information in this manual is subject to change without notice, and should not be construed as a commitment by Xylogics, Inc. Xylogics assumes no responsibility for any errors that may appear in this document. Annex, Annex II, Annex lie, Annexthree, and Annex 3 are trademarks of Xylogics, Inc. UNIX is a registered trademark of AT&T. Ethernet is a registered trademark of Xerox Corporation. IBM is a registered trademark of the International Business Machines Corporation. XENIX Is a trademark of Microsoft Corporation. LAT is a trademark of Digital Equipment Corporation. Postscript is a registered trademark of Adobe Systems Incorporated. Copyright© 1990 Xylogics, Inc. Printed in the USA. Contents Preface .................................................. xiii General . xiii Supported Version . xiv Printing Conventions . xiv Related Documents . xv Book A: Overview Chapter 1: Introduction to the Annex ....................... A-1 General . A-1 Annex Capabilities . A-2 Network Administrator (na) Utility . A-2 Command Line Interpreter (CLI) . A-3 Customizing the User Interface . A-3 Expedited Remote Procedure Call Daemon (erpcd) . A-3 Extensive Security System . A-3 Port Servers and Rotaries . A-4 UNIX Host-originated Connections.................................. A-5 Name Server Support . A-5 Network Management . A-6 Full Routing . A-6 Multi-protocol Support . A-7 Applications for the Annex . A-7 Connecting Terminals . A-7 Connecting Remote Hosts, Networks, and Annexes.................... A-8 Connecting PCs to the Network . -

Appendix a Protocol Filters

APPENDIX A Protocol Filters The tables in this appendix list some of the protocols that you can filter on the access point. In each table, the Protocol column lists the protocol name, the Additional Identifier column lists other names for the same protocol, and the ISO Designator column lists the numeric designator for each protocol. Cisco IOS Software Configuration Guide for Cisco Aironet Access Points A-1 Appendix A Protocol Filters Table A-1 EtherType Protocols Protocol Additional Identifier ISO Designator ARP — 0x0806 RARP — 0x8035 IP — 0x0800 Berkeley Trailer Negotiation — 0x1000 LAN Test — 0x0708 X.25 Level3 X.25 0x0805 Banyan — 0x0BAD CDP — 0x2000 DEC XNS XNS 0x6000 DEC MOP Dump/Load — 0x6001 DEC MOP MOP 0x6002 DEC LAT LAT 0x6004 Ethertalk — 0x809B Appletalk ARP Appletalk 0x80F3 AARP IPX 802.2 — 0x00E0 IPX 802.3 — 0x00FF Novell IPX (old) — 0x8137 Novell IPX (new) IPX 0x8138 EAPOL (old) — 0x8180 EAPOL (new) — 0x888E Telxon TXP TXP 0x8729 Aironet DDP DDP 0x872D Enet Config Test — 0x9000 NetBUI — 0xF0F0 Cisco IOS Software Configuration Guide for Cisco Aironet Access Points A-2 Appendix A Protocol Filters Table A-2 IP Protocols Protocol Additional Identifier ISO Designator dummy — 0 Internet Control Message Protocol ICMP 1 Internet Group Management Protocol IGMP 2 Transmission Control Protocol TCP 6 Exterior Gateway Protocol EGP 8 PUP — 12 CHAOS — 16 User Datagram Protocol UDP 17 XNS-IDP IDP 22 ISO-TP4 TP4 29 ISO-CNLP CNLP 80 Banyan VINES VINES 83 Encapsulation Header encap_hdr 98 Spectralink Voice Protocol SVP 119 Spectralink raw -

VMG4825-B10A User's Guide

VMG4825-B10A Wireless N VDSL2 IAD with USB Version 5.11 Edition 1, 05/2016 Quick Start Guide User’s Guide Default Login Details LAN IP Address http://192.168.1.1 Login admin, user www.zyxel.com Password 1234, user Copyright © 2016 ZyXEL Communications Corporation IMPORTANT! READ CAREFULLY BEFORE USE. KEEP THIS GUIDE FOR FUTURE REFERENCE. Screenshots and graphics in this book may differ slightly from your product due to differences in your product firmware or your computer operating system. Every effort has been made to ensure that the information in this manual is accurate. Related Documentation •Quick Start Guide The Quick Start Guide shows how to connect the VMG and access the Web Configurator. •More Information Go to support.zyxel.com to find other information on the VMG. VMG4825-B10A User’s Guide 2 Contents Overview Contents Overview User’s Guide .......................................................................................................................................14 Introducing the VMG ...............................................................................................................................15 The Web Configurator .............................................................................................................................22 Quick Start ...............................................................................................................................................29 Tutorials ..................................................................................................................................................32 -

Terminal / Remote Access Server Reference Manual

Terminal / Remote Access Server Reference Manual version 1.2 Reference Manual - Terminal / Remote Access Server Conventions To help with reading and using this reference manual, we will use the following conventions : Bold : ACS commands. Only commands are displayed in bold font, not parameters. Italic : Commands parameters and examples values are displayed in italic font. Text box All text typed during an ACS session GRAY Commands syntax - 2 - Reference Manual - Terminal / Remote Access Server CONTENTS AUDIT...................................................................................................................................5 CLOSE SESSION................................................................................................................8 DHCP...................................................................................................................................9 DOMAIN.............................................................................................................................11 EXIT...................................................................................................................................13 FINGER..............................................................................................................................14 HELP..................................................................................................................................15 IFCONFIG..........................................................................................................................16 -

Liste Des Applications Et Ports TCP/UDP Associés

Liste des applications et ports TCP/UDP Associés Application Port N° Application Port N° Application Port N° Application Port N° Application Port N° tcpmux 1/tcp nntp 119/tcp ldap 389/tcp ldaps 636/udp gnunet 2086/tcp echo 7/tcp ntp 123/tcp ldap 389/udp tinc 655/tcp gnunet 2086/udp echo 7/udp ntp 123/udp imsp 406/tcp tinc 655/udp rtcm-sc104 2101/tcp discard 9/tcp pwdgen 129/tcp imsp 406/udp silc 706/tcp rtcm-sc104 2101/udp discard 9/udp pwdgen 129/udp svrloc 427/tcp silc 706/udp gsigatekeeper 2119/tcp systat 11/tcp loc-srv 135/tcp svrloc 427/udp kerberos-adm 749/tcp gsigatekeeper 2119/udp daytime 13/tcp loc-srv 135/udp https 443/tcp webster 765/tcp gris 2135/tcp daytime 13/udp netbios-ns 137/tcp https 443/udp webster 765/udp gris 2135/udp netstat 15/tcp netbios-ns 137/udp snpp 444/tcp rsync 873/tcp cvspserver 2401/tcp qotd 17/tcp netbios-dgm 138/tcp snpp 444/udp rsync 873/udp cvspserver 2401/udp msp 18/tcp netbios-dgm 138/udp microsoft-ds 445/tcp ftps-data 989/tcp venus 2430/tcp msp 18/udp netbios-ssn 139/tcp microsoft-ds 445/udp ftps 990/tcp venus 2430/udp chargen 19/tcp netbios-ssn 139/udp kpasswd 464/tcp telnets 992/tcp venus-se 2431/tcp chargen 19/udp imap2 143/tcp kpasswd 464/udp telnets 992/udp venus-se 2431/udp ftp-data 20/tcp imap2 143/udp saft 487/tcp imaps 993/tcp codasrv 2432/tcp ftp 21/tcp snmp 161/tcp saft 487/udp imaps 993/udp codasrv 2432/udp fsp 21/udp snmp 161/udp isakmp 500/tcp ircs 994/tcp codasrv-se 2433/tcp ssh 22/tcp snmp-trap 162/tcp isakmp 500/udp ircs 994/udp codasrv-se 2433/udp ssh 22/udp snmp-trap 162/udp rtsp -

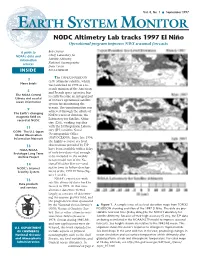

September 1997 EARTH SYSTEM MONITOR NODC Altimetry Lab Tracks 1997 El Niño Operational Program Improves NWS Seasonal Forecasts

Vol. 8, No. 1 ● September 1997 EARTH SYSTEM MONITOR NODC Altimetry Lab tracks 1997 El Niño Operational program improves NWS seasonal forecasts A guide to Bob Cheney NOAA's data and Chief, Laboratory for information Satellite Altimetry services National Oceanographic Data Center INSIDE NOAA/NESDIS The TOPEX/POSEIDON 3 (T/P) altimeter satellite, which News briefs was launched in 1992 as a re- search mission of the American 5 and French space agencies, has The NOAA Central recently become an integral part Library and coastal of NOAA’s operational satellite ocean information system for monitoring the 9 oceans. The transformation was achieved through the efforts of The Earth’s changing NODC’s newest division, the magnetic field on Laboratory for Satellite Altim- record at NGDC etry (LSA), working together 11 with the Jet Propulsion Labora- tory (JPL) and the Naval GOIN: The U.S.-Japan Global Observation Oceanographic Office Information Network (NAVOCEANO). Since late 1996, the highly-accurate sea level 13 observations provided by T/P NASA/NOAA have been available with a delay Prototype Long Term of only two days—fast enough Archive Project to be included in the weekly ocean model run of the Na- 14 tional Weather Service—and NODC’s Internet just in time to follow develop- Security System ment of the 1997 El Niño (Fig- ures 1 and 2). 15 NOAA’s experience with satellite altimetry dates back to Data products and services Geos-3 in 1975. At that time altimeter data were viewed largely as a means of determin- NT OF C E OM TM M ing the marine gravity field, and R E A R P C the program was thus sponsored E E D ▲ Figure 1. -

AXIS 5470E/670E) Data Streams Via the SNA Transport Protocol

AXIS AXIS Print Server Print Server AXIS 5470e/570/670e AXIS 5470e/570/670e AXIS 5470e/570/670e Print Ser AXIS 5470e/570/670e Print Server User’s Guide Axis Communications Part No: 17735 www.axis.com Revision 1.0, Date: September 2000 Copyright © Axis Communications AB, 2000 Lund Phone: +46 46 272 18 00 Boston Phone: +1 978 614 20 00 Miami Phone: +1 305 629 3524 User’s Manual Paris Phone: +33 1 49 69 1550 v London er User’ Phone: +44 207 553 9200 Madrid Phone: +34 91 803 46 43 s Guide Munich Phone: +49 811 555 08 0 Rotterdam Phone: +31 10 444 34 34 Turin Phone: +39 011 841 321 Tokyo Phone: +81 3 3545 8282 Singapore Phone: +65 836 2777 Hong Kong Phone: +852 2836 0813 Shanghai Phone: +86 21 6431 1690 Taipei Phone: +886 2 2546 9668 High Performance Multi-Protocol Print Servers for Virtually All Networks Seoul Phone: +82 2 780 9636 Sydney Phone: +61 2 9967 5700 www.axis.com The Axis logo is a registered trademark of Axis Communications AB. All other trademarks are owned by their respective companies. 2 AXIS 5470e/570/670e User’s Manual Safety Notices Please take some time to read through the safety notices before installing the AXIS 5470e/570/670e. Caution! - must be observed to avoid loss of data or damage to your equipment. Important: - must be observed to avoid operational impairment. Do not proceed beyond any of the above notices unless you have taken appropriate measures! Electromagnetic Compatibility (EMC) notices - USA This equipment generates and radiates radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. -

CN2610 Dual-LAN Async Server User's Manual

CN2610 Dual-LAN Async Server User’s Manual Third Edition, June 2006 www.moxa.com/product MOXA Technologies Co., Ltd. Tel: +886-2-8919-1230 Fax: +886-2-8919-1231 Web: www.moxa.com MOXA Technical Support Worldwide: [email protected] The Americas [email protected] CN2610 Async Server User’s Manual The software described in this manual is furnished under a license agreement and may be used only in accordance with the terms of that agreement. Copyright Notice Copyright © 2006 MOXA Technologies Co., Ltd. All rights reserved. Reproduction without permission is prohibited. Trademarks MOXA is a registered trademark of The Moxa Group. All other trademarks or registered marks in this manual belong to their respective manufacturers. Disclaimer Information in this document is subject to change without notice and does not represent a commitment on the part of Moxa. Moxa provides this document “as is,” without warranty of any kind, either expressed or implied, including, but not limited to, its particular purpose. Moxa reserves the right to make improvements and/or changes to this manual, or to the products and/or the programs described in this manual, at any time. Information provided in this manual is intended to be accurate and reliable. However, Moxa Technologies assumes no responsibility for its use, or for any infringements on the rights of third parties that may result from its use. This product might include unintentional technical or typographical errors. Changes are periodically made to the information herein to correct such errors, and these changes are incorporated into new editions of the publication. -

ELFIQ APP OPTIMIZER White Paper V1.03 - May 2015 CONTENTS Introduction

ELFIQ APP OPTIMIZER White Paper V1.03 - May 2015 CONTENTS Introduction ...............................................................................................................................................................................3 Signature-Based Recognition vs. ACL’s ................................................................................................................3 Detection Engine ...................................................................................................................................................................3 Using Groups or Individual Applications .............................................................................................................3 Actions Once an Application is Detected ...........................................................................................................3 Appendix A: Application List ........................................................................................................................................ 4 martellotech.com elfiq.com 2 INTRODUCTION The Elfiq AppOptimizer is designed to give organizations full control over their existing and future bandwidth, guaranteeing key applications such as Citrix XenDesktop or Skype get priority treatment and undesirables such as peer-to-peer file transfers or games are limited or no longer permitted. It is an add-on-module that provides application-layer deep packet inspection (layer 7) classification and control, including Mobile, Social Networking, P2P, Instant Messaging,