An Evaluation of Soft Processors As a Reliable Computing Platform

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

RAD750 at Our Website: Click HERE RAD750 Board

Full-service, independent repair center -~ ARTISAN® with experienced engineers and technicians on staff. TECHNOLOGY GROUP ~I We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins. Custom engineering Your definitive source so your equipment works exactly as you specify. for quality pre-owned • Critical and expedited services • Leasing / Rentals/ Demos equipment. • In stock/ Ready-to-ship • !TAR-certified secure asset solutions Expert team I Trust guarantee I 100% satisfaction Artisan Technology Group (217) 352-9330 | [email protected] | artisantg.com All trademarks, brand names, and brands appearing herein are the property o f their respective owners. Find the BAE Systems RAD750 at our website: Click HERE RAD750 Board Hardware Specification Document Number 234A524 Release Date August 1, 2000 Copyright by BAE SYSTEMS All Rights Reserved Document Number: 234A524 RAD750 CompactPCI Hardware Specification Notices Before using this information and the product it supports, be sure to read the general information on the back cover of this book. Trademarks The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both: IBM IBM Logo PowerPC PowerPC 750 The following are trademarks of BAE SYSTEMS in the United States, or other countries, or both: RAD750 The following are registered trademarks of PCI Industrial Computer Manufacturing Group in the United States, or other countries, or both: PICMG CompactPCI Other company, product, and service names may be trademarks or service marks of others. Preliminary Edition (Version 4.0, 8/1/2000) This unpublished document is the preliminary edition of RAD750 3U CompactPCI board Hardware Specification. -

Debugging System for Openrisc 1000- Based Systems

Debugging System for OpenRisc 1000- based Systems Nathan Yawn [email protected] 05/12/09 Copyright (C) 2008 Nathan Yawn Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license should be included with this document. If not, the license may be obtained from www.gnu.org, or by writing to the Free Software Foundation. This document is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. History Rev Date Author Comments 1.0 20/7/2008 Nathan Yawn Initial version Contents 1.Introduction.............................................................................................................................................5 1.1.Overview.........................................................................................................................................5 1.2.Versions...........................................................................................................................................6 1.3.Stub-based methods.........................................................................................................................6 2.System Components................................................................................................................................7 -

Embedded Processors on FPGA: Hard-Core Vs Soft-Core Vivek J

Grand Valley State University ScholarWorks@GVSU Masters Theses Graduate Research and Creative Practice 5-19-2017 Embedded processors on FPGA: Hard-core vs Soft-core Vivek J. Vazhoth Kanhiroth Grand Valley State University Follow this and additional works at: http://scholarworks.gvsu.edu/theses Part of the Engineering Commons Recommended Citation Vazhoth Kanhiroth, Vivek J., "Embedded processors on FPGA: Hard-core vs Soft-core" (2017). Masters Theses. 845. http://scholarworks.gvsu.edu/theses/845 This Thesis is brought to you for free and open access by the Graduate Research and Creative Practice at ScholarWorks@GVSU. It has been accepted for inclusion in Masters Theses by an authorized administrator of ScholarWorks@GVSU. For more information, please contact [email protected]. Embedded processors on FPGA: Hard-core vs Soft-core Vivek Jayakrishnan Vazhoth Kanhiroth A Thesis submitted to the Graduate Faculty of GRAND VALLEY STATE UNIVERSITY In Partial Fulfilment of the Requirements For the Degree of Master of Science in Electrical Engineering Padnos College of Engineering and Computing April 2017 DEDICATION To my parents Jayakrishnan and Jayalakshmi who are my biggest inspiration and to my mentor Rajesh without whose help I would never have come out of my shell. 3 ACKNOWLEDGEMENTS I would like to thank my Thesis Advisor Dr. Chirag Parikh without whose patience, guidance and understanding I would not have finished this thesis. I would also like to thank my Thesis committee members Dr. Christian Trefftz and Dr. Azizur Rahman for their valuable inputs and feedback about my thesis. I am indebted to Dr. Shabbir Choudhuri for always being approachable and helping me on innumerable occasions over the last 3 years. -

Microkernel Mechanisms for Improving the Trustworthiness of Commodity Hardware

Microkernel Mechanisms for Improving the Trustworthiness of Commodity Hardware Yanyan Shen Submitted in fulfilment of the requirements for the degree of Doctor of Philosophy School of Computer Science and Engineering Faculty of Engineering March 2019 Thesis/Dissertation Sheet Surname/Family Name : Shen Given Name/s : Yanyan Abbreviation for degree as give in the University calendar : PhD Faculty : Faculty of Engineering School : School of Computer Science and Engineering Microkernel Mechanisms for Improving the Trustworthiness of Commodity Thesis Title : Hardware Abstract 350 words maximum: (PLEASE TYPE) The thesis presents microkernel-based software-implemented mechanisms for improving the trustworthiness of computer systems based on commercial off-the-shelf (COTS) hardware that can malfunction when the hardware is impacted by transient hardware faults. The hardware anomalies, if undetected, can cause data corruptions, system crashes, and security vulnerabilities, significantly undermining system dependability. Specifically, we adopt the single event upset (SEU) fault model and address transient CPU or memory faults. We take advantage of the functional correctness and isolation guarantee provided by the formally verified seL4 microkernel and hardware redundancy provided by multicore processors, design the redundant co-execution (RCoE) architecture that replicates a whole software system (including the microkernel) onto different CPU cores, and implement two variants, loosely-coupled redundant co-execution (LC-RCoE) and closely-coupled redundant co-execution (CC-RCoE), for the ARM and x86 architectures. RCoE treats each replica of the software system as a state machine and ensures that the replicas start from the same initial state, observe consistent inputs, perform equivalent state transitions, and thus produce consistent outputs during error-free executions. -

ASIC Implemented Microblaze-Based Coprocessor for Data Stream

ASIC-IMPLEMENTED MICROBLAZE-BASED COPROCESSOR FOR DATA STREAM MANAGEMENT SYSTEMS A Thesis Submitted to the Faculty of Purdue University by Linknath Surya Balasubramanian In Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical and Computer Engineering May 2020 Purdue University Indianapolis, Indiana ii THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF THESIS APPROVAL Dr. John J. Lee, Chair Department of Electrical and Computer Engineering Dr. Lauren A. Christopher Department of Electrical and Computer Engineering Dr. Maher E. Rizkalla Department of Electrical and Computer Engineering Approved by: Dr. Brian King Head of Graduate Program iii ACKNOWLEDGMENTS I would first like to express my gratitude to my advisor Dr. John J. Lee and my thesis committee members Dr. Lauren A. Christopher and Dr. Maher E. Rizkalla for their patience, guidance, and support during this journey. I would also like to thank Mrs. Sherrie Tucker for her patience, help, and encouragement. Lastly, I must thank Dr. Pranav Vaidya and Mr. Tareq S. Alqaisi for all their support, technical guidance, and advice. Thank you all for taking time and helping me complete this study. iv TABLE OF CONTENTS Page LIST OF TABLES :::::::::::::::::::::::::::::::::: vi LIST OF FIGURES ::::::::::::::::::::::::::::::::: vii ABSTRACT ::::::::::::::::::::::::::::::::::::: ix 1 INTRODUCTION :::::::::::::::::::::::::::::::: 1 1.1 Previous Work ::::::::::::::::::::::::::::::: 1 1.2 Motivation :::::::::::::::::::::::::::::::::: 2 1.3 Thesis Outline :::::::::::::::::::::::::::::::: -

Implementation, Verification and Validation of an Openrisc-1200

(IJACSA) International Journal of Advanced Computer Science and Applications, Vol. 10, No. 1, 2019 Implementation, Verification and Validation of an OpenRISC-1200 Soft-core Processor on FPGA Abdul Rafay Khatri Department of Electronic Engineering, QUEST, NawabShah, Pakistan Abstract—An embedded system is a dedicated computer system in which hardware and software are combined to per- form some specific tasks. Recent advancements in the Field Programmable Gate Array (FPGA) technology make it possible to implement the complete embedded system on a single FPGA chip. The fundamental component of an embedded system is a microprocessor. Soft-core processors are written in hardware description languages and functionally equivalent to an ordinary microprocessor. These soft-core processors are synthesized and implemented on the FPGA devices. In this paper, the OpenRISC 1200 processor is used, which is a 32-bit soft-core processor and Fig. 1. General block diagram of embedded systems. written in the Verilog HDL. Xilinx ISE tools perform synthesis, design implementation and configure/program the FPGA. For verification and debugging purpose, a software toolchain from (RISC) processor. This processor consists of all necessary GNU is configured and installed. The software is written in C components which are available in any other microproces- and Assembly languages. The communication between the host computer and FPGA board is carried out through the serial RS- sor. These components are connected through a bus called 232 port. Wishbone bus. In this work, the OR1200 processor is used to implement the system on a chip technology on a Virtex-5 Keywords—FPGA Design; HDLs; Hw-Sw Co-design; Open- FPGA board from Xilinx. -

Openpiton: an Open Source Manycore Research Framework

OpenPiton: An Open Source Manycore Research Framework Jonathan Balkind Michael McKeown Yaosheng Fu Tri Nguyen Yanqi Zhou Alexey Lavrov Mohammad Shahrad Adi Fuchs Samuel Payne ∗ Xiaohua Liang Matthew Matl David Wentzlaff Princeton University fjbalkind,mmckeown,yfu,trin,yanqiz,alavrov,mshahrad,[email protected], [email protected], fxiaohua,mmatl,[email protected] Abstract chipset Industry is building larger, more complex, manycore proces- sors on the back of strong institutional knowledge, but aca- demic projects face difficulties in replicating that scale. To Tile alleviate these difficulties and to develop and share knowl- edge, the community needs open architecture frameworks for simulation, synthesis, and software exploration which Chip support extensibility, scalability, and configurability, along- side an established base of verification tools and supported software. In this paper we present OpenPiton, an open source framework for building scalable architecture research proto- types from 1 core to 500 million cores. OpenPiton is the world’s first open source, general-purpose, multithreaded manycore processor and framework. OpenPiton leverages the industry hardened OpenSPARC T1 core with modifica- Figure 1: OpenPiton Architecture. Multiple manycore chips tions and builds upon it with a scratch-built, scalable uncore are connected together with chipset logic and networks to creating a flexible, modern manycore design. In addition, build large scalable manycore systems. OpenPiton’s cache OpenPiton provides synthesis and backend scripts for ASIC coherence protocol extends off chip. and FPGA to enable other researchers to bring their designs to implementation. OpenPiton provides a complete verifica- tion infrastructure of over 8000 tests, is supported by mature software tools, runs full-stack multiuser Debian Linux, and has been widespread across the industry with manycore pro- is written in industry standard Verilog. -

I.MX 8Quadxplus Power and Performance

NXP Semiconductors Document Number: AN12338 Application Note Rev. 4 , 04/2020 i.MX 8QuadXPlus Power and Performance 1. Introduction Contents This application note helps you to design power 1. Introduction ........................................................................ 1 management systems. It illustrates the current drain 2. Overview of i.MX 8QuadXPlus voltage supplies .............. 1 3. Power measurement of the i.MX 8QuadXPlus processor ... 2 measurements of the i.MX 8QuadXPlus Applications 3.1. VCC_SCU_1V8 power ........................................... 4 Processors taken on NXP Multisensory Evaluation Kit 3.2. VCC_DDRIO power ............................................... 4 (MEK) Platform through several use cases. 3.3. VCC_CPU/VCC_GPU/VCC_MAIN power ........... 5 3.4. Temperature measurements .................................... 5 This document provides details on the performance and 3.5. Hardware and software used ................................... 6 3.6. Measuring points on the MEK platform .................. 6 power consumption of the i.MX 8QuadXPlus 4. Use cases and measurement results .................................... 6 processors under a variety of low- and high-power 4.1. Low-power mode power consumption (Key States modes. or ‘KS’)…… ......................................................................... 7 4.2. Complex use case power consumption (Arm Core, The data presented in this application note is based on GPU active) ......................................................................... 11 5. SOC -

Part 1 of 4 : Introduction to RISC-V ISA

PULP PLATFORM Open Source Hardware, the way it should be! Working with RISC-V Part 1 of 4 : Introduction to RISC-V ISA Frank K. Gürkaynak <[email protected]> Luca Benini <[email protected]> http://pulp-platform.org @pulp_platform https://www.youtube.com/pulp_platform Working with RISC-V Summary ▪ Part 1 – Introduction to RISC-V ISA ▪ What is RISC-V about ▪ Description of ISA, and basic principles ▪ Simple 32b implementation (Ibex by LowRISC) ▪ How to extend the ISA (CV32E40P by OpenHW group) ▪ Part 2 – Advanced RISC-V Architectures ▪ Part 3 – PULP concepts ▪ Part 4 – PULP based chips | ACACES 2020 - July 2020 Working with RISC-V Few words about myself Frank K. Gürkaynak (just call me Frank) Senior scientist at ETH Zurich (means I am old) working with Luca Studied / Worked at Universities: in Turkey, United States and Switzerland (ETHZ and EPFL) Involved in Digital Design, Low Power Circuits, Open Source Hardware Part of PULP project from the beginning in 2013 | ACACES 2020 - July 2020 Working with RISC-V RISC-V Instruction Set Architecture ▪ Started by UC-Berkeley in 2010 SW ▪ Contract between SW and HW Applications ▪ Partitioned into user and privileged spec ▪ External Debug OS ▪ Standard governed by RISC-V foundation ▪ ETHZ is a founding member of the foundation ISA ▪ Necessary for the continuity User Privileged ▪ Defines 32, 64 and 128 bit ISA Debug ▪ No implementation, just the ISA ▪ Different implementations (both open and close source) HW ▪ At ETH Zurich we specialize in efficient implementations of RISC-V cores | ACACES 2020 - July 2020 Working with RISC-V RISC-V maintains basically a PDF document | ACACES 2020 - July 2020 Working with RISC-V ISA defines the instructions that processor uses C++ program translated to RISC-V instructions defined by ISA. -

A Soft Processor Microblaze-Based Embedded System for Cardiac Monitoring

(IJACSA) International Journal of Advanced Computer Science and Applications, Vol. 4, No. 9, 2013 A Soft Processor MicroBlaze-Based Embedded System for Cardiac Monitoring El Hassan El Mimouni Mohammed Karim University Sidi Mohammed Ben Abdellah University Sidi Mohammed Ben Abdellah Fès, Morocco Fès, Morocco Abstract—this paper aims to contribute to the efforts of recent years, and has become also an important way to assert design community to demonstrate the effectiveness of the state of the heart’s condition [5 - 9]. the art Field Programmable Gate Array (FPGA), in the embedded systems development, taking a case study in the II. SYSTEM OVERVIEW biomedical field. With this design approach, we have developed a We have designed and implemented a prototype of basic System on Chip (SoC) for cardiac monitoring based on the soft embedded system for cardiac monitoring, whose functional processor MicroBlaze and the Xilkernel Real Time Operating block diagram is shown in the figure 2; it exhibits a modular System (RTOS), both from Xilinx. The system permits the structure that facilitates the development and debugging. Thus, acquisition and the digitizing of the Electrocardiogram (ECG) analog signal, displaying heart rate on seven segments module it includes 2 main modules: and ECG on Video Graphics Adapter (VGA) screen, tracing the An analog module intended for acquiring and heart rate variability (HRV) tachogram, and communication conditioning of the analog ECG signal to make it with a Personal Computer (PC) via the serial port. We have used appropriate for use by the second digital module ; the MIT_BIH Database records to test and evaluate our implementation performance. -

Up Cores T Est Folder Opencores Name Status Author Style / Clone

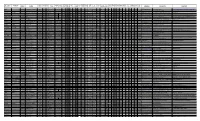

_uP_cores_t opencores style / data inst repor com LUTs blk F tool MIPS clks/ KIPS src # src tool fltg Ha max max byte # # pipe start last status author FPGA top file doc reference note worthy comments date LUT? est folder name clone size size ter ment ALUT mults ram max ver /clk inst /LUT code files chain pt vd data inst adrs inst reg len year revis cray1 alpha Christopher Fenton cray1 64 16 kintex-7-3 James Brakefield13463 6 19 10 127 ## 14.7 6.00 1.0 56.6 verilog 46 cray_sys_topyes yes Y N 4M 4M N 512 2010 CRAY data sheets homebrew Cray1 www.chrisfenton.com/homebrew-cray-1a/ fpgammix stable Tommy Thorn MMIX 64 32 arria-2 James Brakefield11605 A 8 10 94 ## q13.1 1.50 4.0 3.0 system verilog2 core yes yes Y Y 4G 4G Y 256 288 2006 2008 clone of Knuth's MMIX micro-coded s1_core S1 Core stable Fabrizio Fazzino etal SPARC 64 32 kintex-7-3 James Brakefield52845 6 8 59 56 ## v14.1 2.00 1.0 2.1 verilog 136 s1_top yes yes Y N 4G 4G Y 32 2007 2012 SPARC data sheets reduced version of OpenSPARC T1 Vivado run microblaze proprietaryXilinx uBlaze 32 32 kintex-7 Xilinx 546 6 1 320 1.03 1.0 603.7 not avail yes yes opt 4G 4G Y 86 32 3 2002 www.xilinx.com/tools/microblaze.htmMicroBlaze MCS, smallest configuration70 configuration options, MMU optional ARM_Cortex_A9 ASIC ARM ARM a9 32 16 arria V altera 4500 A 1050 2.50 1.0 583.3 asic yes yes Y 4G 4G Y 80 16 10 2012 altera data sheets uses pro-rated LC area dual issue, includes fltg-pt & MMU & caches nios2 proprietaryAltera Nios II 32 32 stratix-5 Altera 895 A 310 1.13 1.0 389.7 not avail yes yes opt 4G 4G -

Performance Evaluation of FPGA Based Embedded ARM Processor

10.1109/ULTSYM.2013.0135 Performance Evaluation of FPGA based Embedded ARM Processor for Ultrasonic Imaging Spenser Gilliland, Pramod Govindan, Thomas Gonnot and Jafar Saniie Department of Electrical and Computer Engineering Illinois Institute of Technology, Chicago IL, U.S.A. Abstract- This study evaluates the performance of an FPGA based embedded ARM processor system to implement signal processing for ultrasonic imaging and nondestructive testing applications. FPGA based embedded processors possess many advantages including a reduced overall development time, increased performance, and the ability to perform hardware- software (HW/SW) co-design. This study examines the execution performance of split spectrum processing, chirplet signal decomposition, Wigner-Ville distributions and short time Fourier transform implementations, on two embedded processing platforms: a Xilinx Virtex-5 FPGA with embedded MicroBlaze processor and a Xilinx Zynq FPGA with embedded ARM processor. Overall, the Xilinx Zynq FPGA significantly outperforms the Virtex-5 based system in software applications I. INTRODUCTION Figure 1. RUSH SoC setup Generally, ultrasonic imaging applications use personal computers or hand held devices. As these devices are not frequency diverse flaw detection [1], parametric echo specifically designed for efficiently executing estimation [2], and joint time-frequency distribution [3]) on computationally intensive ultrasonic signal processing the RUSH platform using a Xilinx Virtex-5 FPGA with an algorithms, the performance of these applications can be embedded soft-core MicroBlaze processor [4,5] and a improved by executing the algorithms using a dedicated Xilinx Zynq 7020 FPGA with an embedded ARM processor embedded system-on-chip (SoC) hardware. However, [6,7] as shown in Figure 2. porting these applications onto an embedded system requires deep knowledge of the processor architecture and RUSH embedded software development tools.