Master / Slave D Type Flip-Flop Tutorial

A couple of definitions :-

RIPPLE THROUGH. An input changes level during the clock period, and the change appears at the output.

PROPAGATION DELAY. The time between applying a signal to an input, and the resulting change in the output.

These can give problems in logic circuits.

The master/slave flip-flop overcomes them.

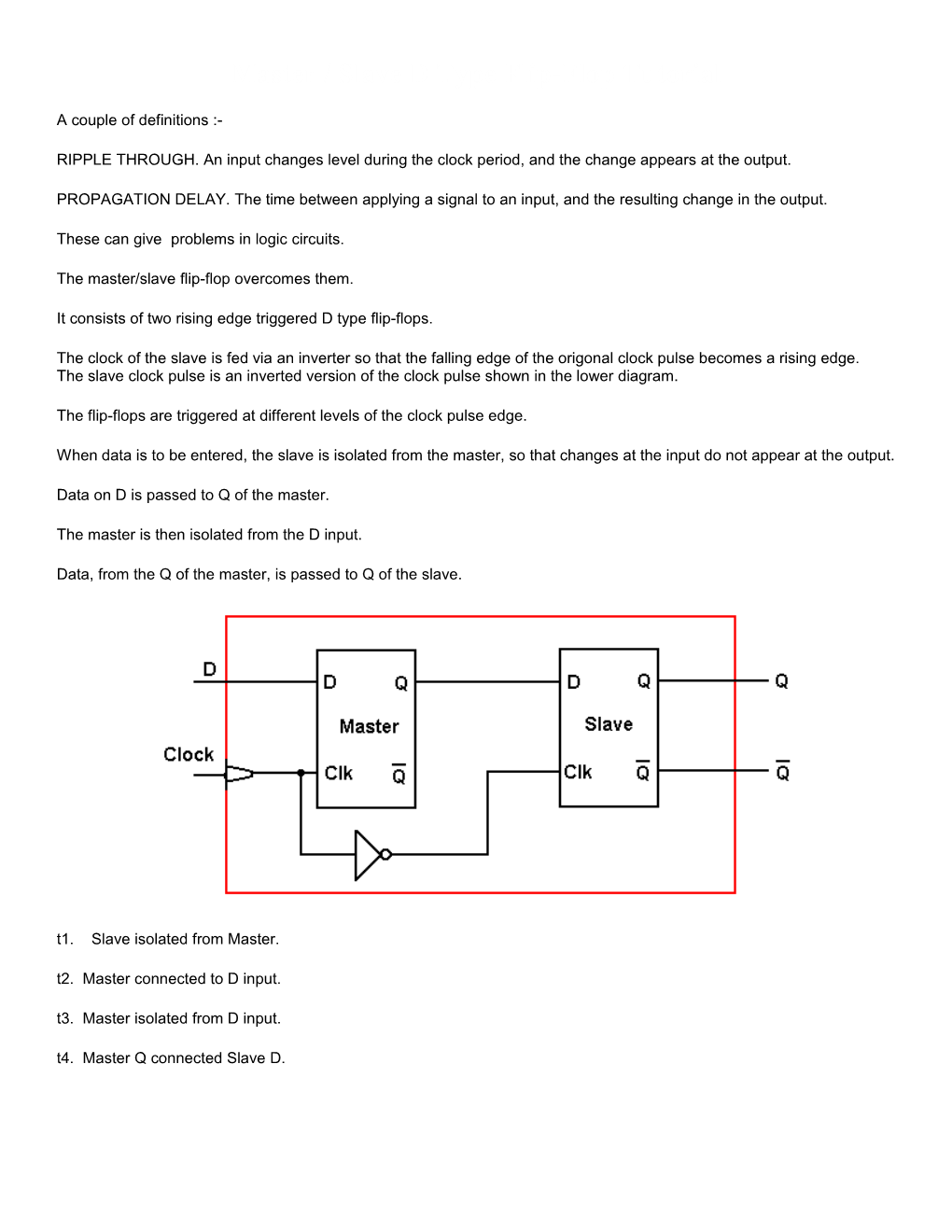

It consists of two rising edge triggered D type flip-flops.

The clock of the slave is fed via an inverter so that the falling edge of the origonal clock pulse becomes a rising edge. The slave clock pulse is an inverted version of the clock pulse shown in the lower diagram.

The flip-flops are triggered at different levels of the clock pulse edge.

When data is to be entered, the slave is isolated from the master, so that changes at the input do not appear at the output.

Data on D is passed to Q of the master.

The master is then isolated from the D input.

Data, from the Q of the master, is passed to Q of the slave.

t1. Slave isolated from Master. t2. Master connected to D input. t3. Master isolated from D input. t4. Master Q connected Slave D. Switch Debouncing Tutorial

When a mechanical power switch is operated, the power is not available instantly.

The switch contacts bounce, giving a series of pulses, as shown in the graph.

The circuit may see these as a series of logic pulses and behave incorrectly.

The circuit shown prevents this.

If we revise the SET/RESET flip-flop, we will recall that once Q has been pulsed high by the SET input, further pulsing produces no change at Q.

Therefore Q only recognizes the first pulse from the bouncing switch and ignores any others.

Similarly, when Q is taken low by taking RESET high, only the first pulse is recognized. NOR Gate Flip-Flop Tutorial

Here, one input of each gate is held LOW by "pull down" resistors.

The other input is cross-coupled to the output of the other gate.

Initially, as shown in diagram A, gate 2 has two LOW inputs, so its output is HIGH.

This HIGH output is one input of gate 1, so the output of gate 1 is LOW.

When the SET input of gate 2 is momentarily pulsed HIGH, the output of gate 2 goes LOW.

This means that both inputs of gate 1 are LOW, so its output is HIGH, which is coupled to an input of gate 2.

Even though the pulse has finished, the output of gate 2 stays LOW because of this HIGH input.

The gates are now in the state shown in diagram B.

We say that the circuit has remembered or LATCHED and is in the SET state.

If the SET is pulsed again, nothing happens, the circuit stays in the SET state.

If the RESET on gate 1 is now pulsed HIGH, the output of gate 1 goes LOW.

This is coupled to gate 2 which now has two LOW inputs, so its output goes HIGH.

The gates have been RESET to their original states.

If the RESET is pulsed again, nothing happens, the circuit stays in the RESET state.

Note that when one output is HIGH, the other is LOW and vice-versa.

If both inputs are taken LOW simultaneously, then there is no change; both inputs are already LOW.

If both inputs are taken HIGH simultaneously, then the result is INDETERMINATE and is to be avoided.

A similar circuit can be constructed using nand gates and pull up resistors.

The inputs are pulsed low to change states. Master–slave (pulse-triggered) D flip-flop

A master–slave D flip-flop is created by connecting two gated D latches in series, and inverting the enable input to one of them. It is called master–slave because the second latch in the series only changes in response to a change in the first (master) latch.

The term pulse-triggered means that data is entered on the rising edge of the clock pulse, but the output does not reflect the change until the falling edge of the clock pulse.

A master–slave D flip-flop. It responds on the negative edge of the enable input (usually a clock).

For a positive-edge triggered master–slave D flip-flop, when the clock signal is low (logical 0) the "enable" seen by the first or "master" D latch (the inverted clock signal) is high (logical 1). This allows the "master" latch to store the input value when the clock signal transitions from low to high. As the clock signal goes high (0 to 1) the inverted "enable" of the first latch goes low (1 to 0) and the value seen at the input to the master latch is "locked". Nearly simultaneously, the twice inverted "enable" of the second or "slave" D latch transitions from low to high (0 to 1) with the clock signal. This allows the signal captured at the rising edge of the clock by the now "locked" master latch to pass through the "slave" latch. When the clock signal returns to low (1 to 0), the output of the "slave" latch is "locked", and the value seen at the last rising edge of the clock is held while the "master" latch begins to accept new values in preparation for the next rising clock edge.

An implementation of a master–slave D flip-flop that is triggered on the positive edge of the clock

By removing the leftmost inverter in the above circuit, a D-type flip flop that strobes on the falling edge of a clock signal can be obtained. This has a truth table like this:

D Q > Qnext 0 X Falling 0 1 X Falling 1

Most D-type flip-flops in ICs have the capability to be set and reset, much like an SR flip-flop. Usually, the illegal S = R = 1 condition is resolved in D-type flip-flops.

Inputs Outputs S R D > Q Q' 0 1 X X 0 1 1 0 X X 1 0 1 1 X X 1 1

By setting S = R = 0, the flip-flop can be used as described above