ELECTRONIC DIGIT 1

LAB 6: J-K FLIP-FLOP

OBJECTIVES:

1. To investigate the basic circuit of J-K flip-flop constructed using basic gates. 2. To investigate the operation of J-K flip-flop and R-S flip-flop. 3. Determine input and output states of J-K flip-flop circuits.

EQUIPMENTS/COMPONENTS

Logic gates ( 74XX-series) J-K flip- flop (7476) LED monitor Oscilloscope Signal Generator

INTRODUCTION

Flip-flop is a basic memory element that is able to store binary information. Even though it is made up of a combinational logic gate that has no storage capability, the way it is connected permit information to be stored. It is called flip-flop because it can be flipped into its set condition in which it stores a binary 1, or flopped into its reset condition in which it stores a binary 0.

PROCEDURE

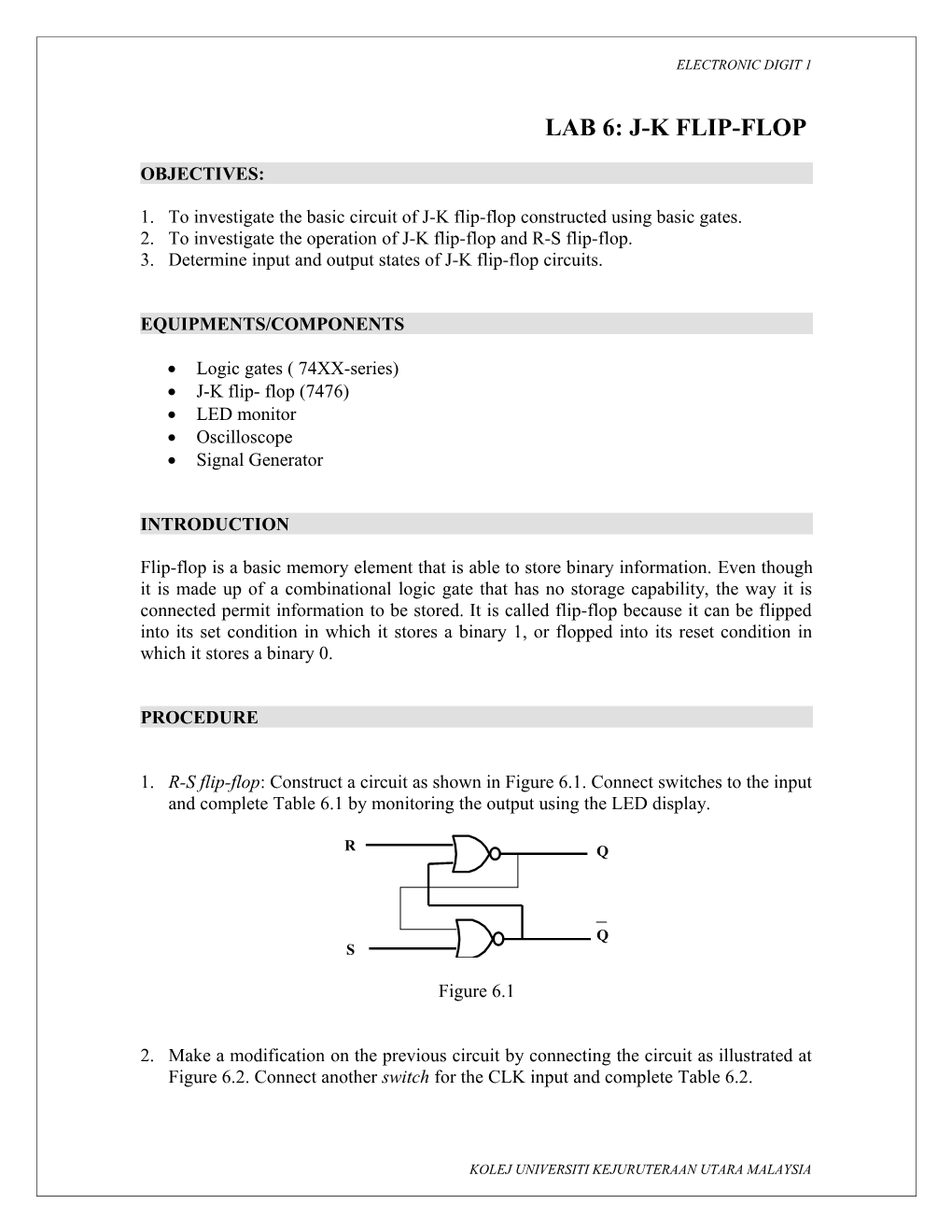

1. R-S flip-flop: Construct a circuit as shown in Figure 6.1. Connect switches to the input and complete Table 6.1 by monitoring the output using the LED display.

R Q

Q S

Figure 6.1

2. Make a modification on the previous circuit by connecting the circuit as illustrated at Figure 6.2. Connect another switch for the CLK input and complete Table 6.2.

KOLEJ UNIVERSITI KEJURUTERAAN UTARA MALAYSIA ELECTRONIC DIGIT 1

R Q

CLK

Q S

Figure 6.2

3. J-K flip-flop: Combine the circuit constructed in procedure 2 with gate AND as shown in Figure 6.3. Perform the following series of test on the circuit by completing Table 6.3.

Q K FigureFigure 6.25-2 CLK J (flip-flop RS) Q

Figure 6.3

4. Figure 6.4 shows IC 7476 which is a JK flip-flop. Verify the operation of JK flip-flop by ignoring the PRE and CLR input. Fill in the results at Table 6.4.

PRE

J Q CLK 7476 K Q

CLR

Figure 6.4

5. Experiment in procedure 4 is repeated but this time the PRE and CLR input are considered. Test all the possible input combination and complete Table 6.5.

KOLEJ UNIVERSITI KEJURUTERAAN UTARA MALAYSIA ELECTRONIC DIGIT 1

Name: ______Matrix No. : ______

RESULTS

Table 6.1

Input Output R S Q Q 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0

Table 6.2

Input Output R S CLK Q Q 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

Table 6.3

KOLEJ UNIVERSITI KEJURUTERAAN UTARA MALAYSIA ELECTRONIC DIGIT 1

Input Output J K CLK Q Q 1 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 1 1 1 1 0 1 1 1 1 1 0

Table 6.4

Input Output J K CLK Q Q 1 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 1 1 1 1 0 1 1 1 1 1 0

Table 6.5

KOLEJ UNIVERSITI KEJURUTERAAN UTARA MALAYSIA ELECTRONIC DIGIT 1

Input Output

KOLEJ UNIVERSITI KEJURUTERAAN UTARA MALAYSIA ELECTRONIC DIGIT 1

CLR PRE J K CLK Q Q 1 1 0 0 0 1 1 0 1 1 1 1 1 0 0 1 1 1 1 1 1 0 0 0 0 1 0 0 1 1 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 1 1 0 1 1 0 0 0 1 1 1 1 0 0 0 0 0 0 0 0 1 1 0 0 1 0 0 0 0 1 1 1

CONCLUSIONS

1. Based on your observations, explain the different between RS flip-flop and JK flip- flop in term of its operation.

KOLEJ UNIVERSITI KEJURUTERAAN UTARA MALAYSIA ELECTRONIC DIGIT 1

2. Discuss the effect of PRE and CLR in JK flip-flop.

APPENDIX

KOLEJ UNIVERSITI KEJURUTERAAN UTARA MALAYSIA ELECTRONIC DIGIT 1

KOLEJ UNIVERSITI KEJURUTERAAN UTARA MALAYSIA